本文引用地址:http://www.eepw.com.cn/article/202302/443565.htm

0 引言

慣性導(dǎo)航系統(tǒng)(Inertial Navigation System,INS)[1],是利用陀螺儀和加速度計(jì)[2],測量載體的加速度和角速度,并實(shí)時(shí)解算其速度、位置及姿態(tài)的系統(tǒng)[3]。慣性導(dǎo)航系統(tǒng)在運(yùn)行過程中既不會(huì)接收外部信號(hào),更不會(huì)向外輻射電磁波。高隱蔽性、全天候、快速響應(yīng)[4]的特性使得慣導(dǎo)系統(tǒng)在飛機(jī)、艦船、火箭和戰(zhàn)略武器中起到了核心的作用。同時(shí)慣性導(dǎo)航也在逐步走向民用,在海底勘探、地下開發(fā)、隧道施工、機(jī)器人技術(shù)等新的國民經(jīng)濟(jì)應(yīng)用場景下,有著大量的工業(yè)落地案例,發(fā)揮了巨大作用[5]。

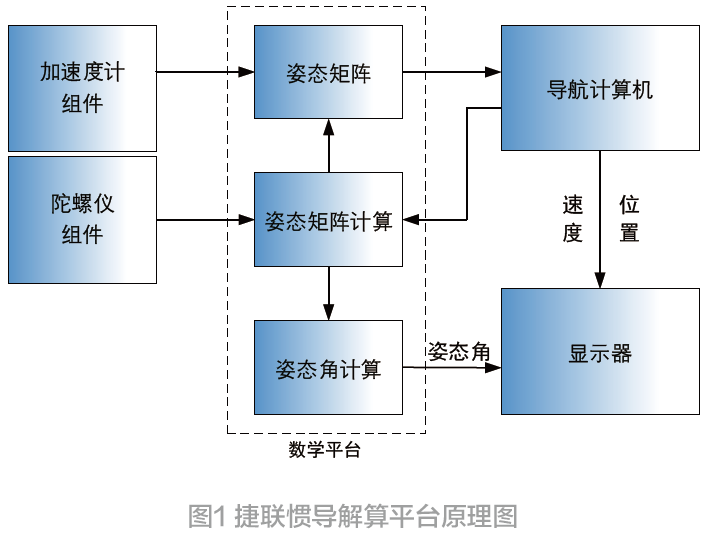

慣性導(dǎo)航系統(tǒng)根據(jù)原理不同包含平臺(tái)和捷聯(lián)兩類。前者將慣性敏感器件安裝在機(jī)械平臺(tái)上,建立慣性坐標(biāo)系;而后者則將其直接安裝于載體本身,建立導(dǎo)航坐標(biāo)系。前者的結(jié)構(gòu)一般較復(fù)雜,體積龐大,低靈活性大大限制了應(yīng)用場景,后者利用數(shù)學(xué)計(jì)算平臺(tái)取代了傳統(tǒng)的機(jī)械結(jié)構(gòu)物理平臺(tái),大大簡化了系統(tǒng)結(jié)構(gòu)。體積小、成本低、便于安裝、靈活更新的諸多優(yōu)點(diǎn)使得捷聯(lián)慣導(dǎo)系統(tǒng)脫穎而出,在21 世紀(jì)后廣泛取代了平臺(tái)慣導(dǎo)系統(tǒng)。

第二次世界大戰(zhàn)時(shí)期,德國人VonBraun 率先設(shè)計(jì)出了V-2 型火箭,它的成功發(fā)射揭開了“慣性導(dǎo)航技術(shù)”這一新興的領(lǐng)域。1970 年4 月,美國宇航局的“阿波羅13 號(hào)”載人飛船在任務(wù)過程中發(fā)生嚴(yán)重爆炸后,憑借備用的捷聯(lián)導(dǎo)航系統(tǒng),得以安全返回地面,至此慣性導(dǎo)航技術(shù)的發(fā)展邁上了新的臺(tái)階并愈發(fā)成熟[6]。國內(nèi)的慣性技術(shù)依賴蘇聯(lián)進(jìn)行艱難起步,篳路藍(lán)縷。在進(jìn)入2000年后,以我國的“神舟”飛船為首的航天事業(yè)廣泛應(yīng)用了捷聯(lián)慣導(dǎo)技術(shù),在戰(zhàn)略武器和運(yùn)載火箭等國防領(lǐng)域成為了中堅(jiān)力量。本文將重點(diǎn)聚焦于捷聯(lián)慣導(dǎo)系統(tǒng)的核心計(jì)算機(jī)架構(gòu)及其硬件平臺(tái),通過分析捷聯(lián)慣導(dǎo)計(jì)算機(jī)的不同架構(gòu)、系統(tǒng)組成,對(duì)其硬件架構(gòu)的發(fā)展迭代情況進(jìn)行總結(jié)歸納,并結(jié)合時(shí)下的新技術(shù)對(duì)其未來發(fā)展方向提出預(yù)測。

1 導(dǎo)航計(jì)算機(jī)的任務(wù)分析

不管導(dǎo)航計(jì)算機(jī)安裝在何種類型的物體上,它的基本工作內(nèi)容都可以總結(jié)提煉出3 個(gè)基本方面:采集、解算、通信。

1.1 數(shù)據(jù)采集

通過特定串口采集陀螺儀和加速度計(jì)的輸出數(shù)據(jù)[7]。由于輸出的信號(hào)類型會(huì)含有模擬信號(hào),所以要設(shè)計(jì)信號(hào)的A/D 轉(zhuǎn)換,把模擬信號(hào)轉(zhuǎn)換成為可以被處理的數(shù)字信號(hào),這個(gè)過程中往往還伴有調(diào)理濾波等。部分場景還要考慮到溫度對(duì)慣性敏感元件的影響,進(jìn)行溫度信號(hào)的采樣處理。

1.2 數(shù)據(jù)解算

數(shù)據(jù)解算的實(shí)質(zhì)就是利用上個(gè)時(shí)刻的導(dǎo)航信息,計(jì)算出這個(gè)時(shí)刻的導(dǎo)航信息,包括姿態(tài)、速度、位置[8]。

1.3 和PC通信

前兩步產(chǎn)生的數(shù)據(jù)要傳輸給PC 機(jī),進(jìn)行輸入數(shù)據(jù)和導(dǎo)航數(shù)據(jù)的存儲(chǔ)。同時(shí)需要考慮到程序錯(cuò)誤、內(nèi)存溢出等常見故障的報(bào)警和檢測功能[9]。

2 導(dǎo)航計(jì)算機(jī)發(fā)展現(xiàn)狀

導(dǎo)航計(jì)算機(jī)誕生之初,直接采用的是體積和重量都十分龐大,且運(yùn)行功耗很高的PC 機(jī),但由于其過于得不夠靈活已經(jīng)被淘汰[10]。之后人們開始考慮研制專用的平臺(tái)來完成這一特定的任務(wù)。1980 年前后,研究人員開始使用PC/104 導(dǎo)航計(jì)算機(jī),它通過單獨(dú)開發(fā)主板及插卡的架構(gòu),大幅度削減了體積和功耗。同時(shí)為了提高適用性采用了更為通用的電源供電。其處理器通用配置是Intel公司的 8086,運(yùn)行在Linux 和DOS 操作系統(tǒng)下。但是PC/104 要擴(kuò)展多串行口和外接AD 采樣卡,進(jìn)而降低了其靈活性,使其幾乎無法應(yīng)用在較小型運(yùn)載體上,因此降低功耗和縮減體積的目標(biāo)還是迫在眉睫[11]。

隨著半導(dǎo)體和電子產(chǎn)業(yè)的革命性發(fā)展,通用CPU、微控制器MCU 和DSP 處理器的優(yōu)勢逐步展露[12]。伴隨嵌入式編程的興起,科研機(jī)構(gòu)開始研究使用各種嵌入式處理器作為核心的導(dǎo)航計(jì)算機(jī)。本文將聚焦國內(nèi)科研單位和高校對(duì)導(dǎo)航計(jì)算機(jī)的研究,通過梳理大量的文獻(xiàn),針對(duì)常見的導(dǎo)航計(jì)算機(jī)的體系結(jié)構(gòu)進(jìn)行了分類總結(jié),并指出不同體系結(jié)構(gòu)的優(yōu)勢和不足。

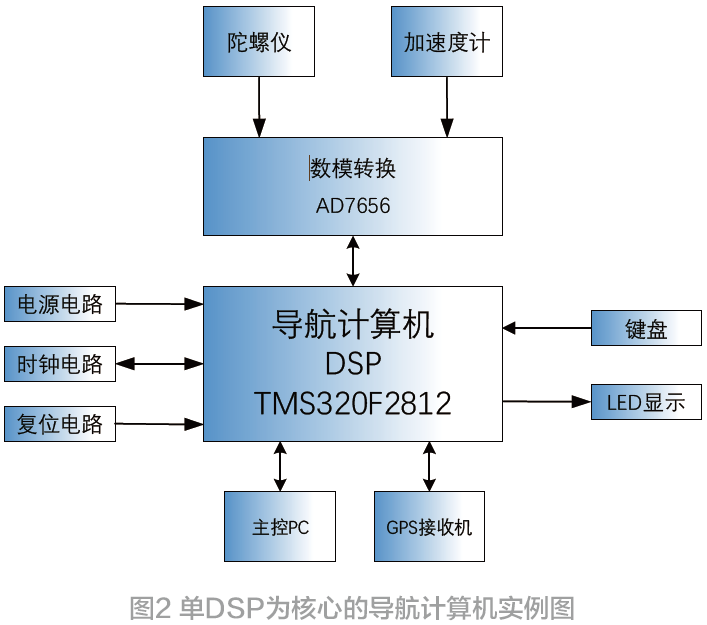

2.1 以DSP、ARM或單片機(jī)作為單獨(dú)的核心處理器

電子科技大學(xué)的紀(jì)杭辛選用了32 位TI 公司的DSP芯片TMS320F2812 作核心[13],負(fù)責(zé)主要的導(dǎo)航解算任務(wù)。同時(shí)為了克服隨時(shí)間積累的誤差,外掛了GPS 接收機(jī)構(gòu)成組合導(dǎo)航,進(jìn)一步成功實(shí)現(xiàn)了GPS/INS 位置和速度組合解算。

以浮點(diǎn)DSP 為核心的優(yōu)勢是精度高,對(duì)采集到的數(shù)據(jù),解算處理速率快,但其缺點(diǎn)是需要擴(kuò)展接口來克服外設(shè)接口比較少的弊端,但是外接擴(kuò)展反而會(huì)增大導(dǎo)航計(jì)算機(jī)的體積與功耗[14]。縱然ARM 擁有更完善的軟件生態(tài)系統(tǒng),在接口控制和數(shù)據(jù)傳輸方面勝過DSP,但是解算速度慢于高性能的DSP。因此單核心的導(dǎo)航計(jì)算機(jī)大多選擇DSP。

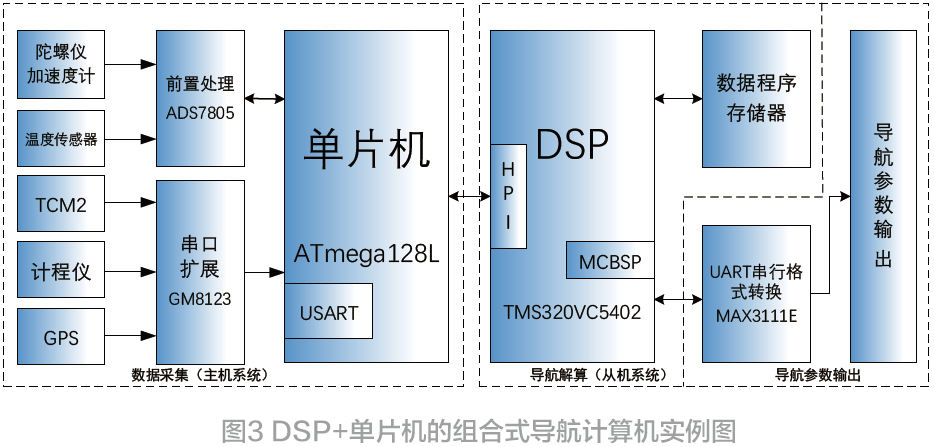

2.2 DSP 或ARM與單片機(jī)的雙機(jī)組合系統(tǒng)

哈爾濱工程大學(xué)的金紅新使用單片機(jī)ATmega128L和DSP TMS320VC5402 進(jìn)行組合設(shè)計(jì)了導(dǎo)航計(jì)算機(jī)[15]。擁有豐富的外設(shè)接口的單片機(jī)作為主機(jī),負(fù)責(zé)數(shù)據(jù)采集任務(wù),預(yù)處理任務(wù)和系統(tǒng)控制任務(wù),DSP 則擔(dān)任從機(jī)的角色,專注于導(dǎo)航解算等任務(wù),繞開了自身較為薄弱的數(shù)據(jù)交換和外設(shè)控制。這種“主機(jī)+ 從機(jī)”的主從式、緊藕合的導(dǎo)航計(jì)算機(jī)的優(yōu)勢明顯成為主流選擇。

雙機(jī)組合的主從結(jié)構(gòu)系統(tǒng)面臨的一大困難,便是雙芯之間的數(shù)據(jù)交換和共享。對(duì)數(shù)據(jù)的實(shí)時(shí)性要求很高,采集的導(dǎo)航數(shù)據(jù)和DSP 每次接收到的數(shù)據(jù)都要確保是最新的。在整個(gè)軟件的設(shè)計(jì)流程中,如何避免單片機(jī)和DSP 在同一時(shí)間,對(duì)同一數(shù)據(jù)存儲(chǔ)區(qū)進(jìn)行同時(shí)操作而產(chǎn)生讀寫沖突成了必須要重視的問題。因此雙機(jī)主從結(jié)構(gòu)的導(dǎo)航計(jì)算機(jī)的通信編程常常十分復(fù)雜,從而降低整個(gè)系統(tǒng)可靠性、穩(wěn)定性,提升了開發(fā)設(shè)計(jì)難度。

2.3 DSP和ARM組合

為了攻克雙處理器主從結(jié)構(gòu)在數(shù)據(jù)交換上的難題,DSP+ARM 的思路也應(yīng)運(yùn)而生。高性能、低功耗的ARM控制接口豐富,數(shù)據(jù)采集和系統(tǒng)控制的能力強(qiáng)悍,十分適合和DSP 組合設(shè)計(jì)捷聯(lián)導(dǎo)航計(jì)算機(jī),便于控制體積和功耗,保證性能等同時(shí)不失適用性[16]。但弊端在于系統(tǒng)硬件結(jié)構(gòu)基本固定后,擴(kuò)展性受到大大的限制。特別是后續(xù)如果計(jì)劃針對(duì)系統(tǒng)的功能進(jìn)行附加和軟硬件升級(jí),則十分不方便。因此,這種結(jié)構(gòu)的慣導(dǎo)計(jì)算機(jī)并沒有大規(guī)模應(yīng)用到實(shí)際工程和設(shè)計(jì)任務(wù)當(dāng)中。

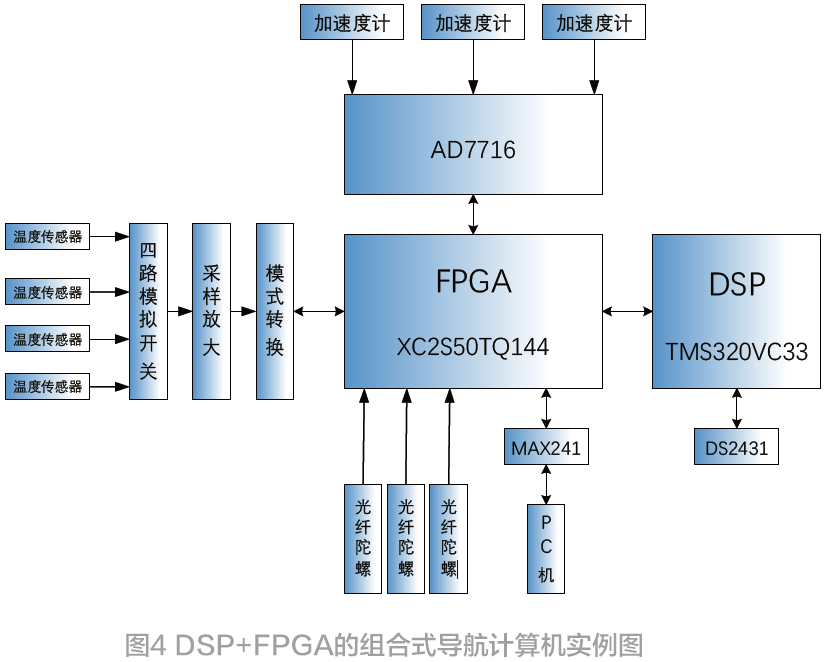

2.4 DSP和FPGA的組合

進(jìn)入21 世紀(jì)人們希望將導(dǎo)航計(jì)算機(jī)部署應(yīng)用在更多的場景中。這種需求對(duì)導(dǎo)航計(jì)算機(jī)進(jìn)一步提出了體積更小、成本更低、維護(hù)更方便等新發(fā)展方向和要求[17]。特別是半導(dǎo)體芯片革命性的迭代發(fā)展使得迷你捷聯(lián)導(dǎo)航系統(tǒng)成為了可能。FPGA 擁有豐富的邏輯資源、強(qiáng)大的邏輯控制和時(shí)序控制能力,讓人們看到了應(yīng)用的可能。特別是它還有足夠的擴(kuò)展IO 接口,并且在數(shù)字信號(hào)處理方面的不俗能力,使得利用FPGA 設(shè)計(jì)捷聯(lián)導(dǎo)航計(jì)算機(jī)成為現(xiàn)實(shí)。

哈爾濱工程大學(xué)的楊梟以“DSP+FPGA”作為雙核心的硬件架構(gòu),設(shè)計(jì)了基于光纖陀螺的捷聯(lián)導(dǎo)航數(shù)據(jù)處理系統(tǒng)[18]。由FPGA 完成數(shù)據(jù)采集后,用多余的資源代替DSP 進(jìn)行濾波工作,DSP 只承擔(dān)接收數(shù)據(jù)后的解算。由于光纖陀螺零漂、標(biāo)度因子的性能指標(biāo)對(duì)溫度變化十分敏感,必須引入溫度采集模塊來進(jìn)行溫度補(bǔ)償。整個(gè)系統(tǒng)工作過程中,可以通過引入中斷響應(yīng)來給FPGA濾波時(shí)間,完成任務(wù)后向DSP 提出中斷請(qǐng)求,再由DSP 來讀取數(shù)據(jù)[19]。特別的是,光纖捷聯(lián)慣導(dǎo)系統(tǒng)數(shù)據(jù)采集模塊含有模擬電路,而慣導(dǎo)核心解算模塊為數(shù)字電路,應(yīng)使用光電耦合器,隔離數(shù)據(jù)采集模塊和導(dǎo)航計(jì)算機(jī)模塊,從而提高電路可靠性和性能指標(biāo)。

DSP 滿足導(dǎo)航計(jì)算機(jī)對(duì)解算算法的高精度要求,且FPGA 眾多的接口便于實(shí)現(xiàn)功能自定義,即使有外接擴(kuò)展其他設(shè)備的需求也能十分靈活地應(yīng)對(duì)。DSP+FPGA這一對(duì)組合在保證了高性能、高可靠性的核心要求前提下,也符合了小體積、低功耗的新發(fā)展要求。最重要的是,整個(gè)系統(tǒng)后期的升級(jí)維護(hù)方便,確定的硬件不需要升級(jí)和改變,只需要對(duì)相應(yīng)的軟件算法進(jìn)行升級(jí)迭代就可以設(shè)計(jì)定制化極強(qiáng)的導(dǎo)航計(jì)算機(jī)。因此這種結(jié)構(gòu)的導(dǎo)航計(jì)算機(jī)迅速成為了當(dāng)下最主流的選擇。

2.5 SOC和SOPC結(jié)構(gòu)

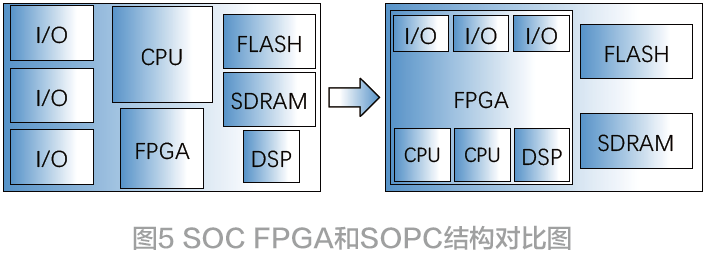

SOC(System On Chip,片上系統(tǒng))是由中央處理器控制存儲(chǔ)器件和其他功能模塊并將他們統(tǒng)一集成在一枚芯片上的片上系統(tǒng)。將傳統(tǒng)的DSP 或ARM 硬核處理器系統(tǒng)和FPGA 再進(jìn)行進(jìn)一步集成,就是SOC FPGA。當(dāng)前十分成熟產(chǎn)品有Intel 公司的 Cyclone V SOCFPGA。如圖所示,它在ARM 和FPGA 之間進(jìn)行大帶寬高速連接,同時(shí)擁有兩者的優(yōu)勢:既可以靈活地運(yùn)行圖形化Linux,又可靈活定制豐富的IO。SOC FPGA 在導(dǎo)航解算方面有很大的應(yīng)用空間和前景,可以最大化利用FPGA 的可編程優(yōu)勢,完成導(dǎo)航數(shù)據(jù)采集和處理,進(jìn)而輔助協(xié)同ARM 進(jìn)行導(dǎo)航數(shù)據(jù)的解算。

進(jìn)一步來說,SOPC(System On a Programmable Chip,可編程片上系統(tǒng))是一種特殊的SOC FPGA,最大不同在于FPGA 利用集成好的資源實(shí)現(xiàn)軟核CPU 而非使用硬核CPU[20]。硬核處理器在不使用時(shí)仍要占用FPGA 資源,而人為搭建的軟核處理器(NIOS II)在不使用時(shí)全部的硬件資源可給FPGA 當(dāng)作資源來使用[21]。SOPC 設(shè)計(jì)方式是依據(jù)目標(biāo)需求進(jìn)行增加和刪減,極為靈活。它的軟件和硬件都可在系統(tǒng)級(jí)上進(jìn)行定制化編程,是目前導(dǎo)航計(jì)算機(jī)研究的一大熱點(diǎn)[22]。

3 結(jié)束語

通過梳理分析不同的慣導(dǎo)計(jì)算機(jī)系統(tǒng)架構(gòu)可以看出,捷聯(lián)導(dǎo)航計(jì)算機(jī)的架構(gòu)和硬件方案在過去的20 年間始終在變化、更新,其重要的現(xiàn)實(shí)原因就是半導(dǎo)體技術(shù)不斷進(jìn)步所誕生的更為優(yōu)秀的核心處理器在不斷變化。這里對(duì)捷聯(lián)慣性導(dǎo)航計(jì)算機(jī)未來的發(fā)展方向做出進(jìn)一步的展望和預(yù)測:

1)進(jìn)一步實(shí)現(xiàn)更低成本、更小體積和更低功耗仍然是迫切的發(fā)展愿景;

2)充分利用半導(dǎo)體電子設(shè)計(jì)行業(yè)的自動(dòng)化設(shè)計(jì)技術(shù),進(jìn)一步進(jìn)行硬件系統(tǒng)可編程的開發(fā),設(shè)計(jì)出以SOCFPGA 和SOPC 架構(gòu)為代表的擴(kuò)展性更強(qiáng)、自定義程度更高的定制化導(dǎo)航計(jì)算機(jī)系統(tǒng);

3)針對(duì)嵌入式操作系統(tǒng)更廣泛的挖掘和迭代,通過軟件設(shè)計(jì)提升系統(tǒng)核心算法的可靠性。

參考文獻(xiàn):

[1] 陳哲.捷聯(lián)慣導(dǎo)系統(tǒng)原理[M].北京:宇航出版社,1986.

[2] 惠欣.基于虛擬儀器技術(shù)的捷聯(lián)慣性導(dǎo)航系統(tǒng)仿真研究[D].哈爾濱:哈爾濱工程大學(xué),2008.

[3] 徐銳.船用光纖陀螺捷聯(lián)慣導(dǎo)系統(tǒng)初始對(duì)準(zhǔn)技術(shù)研究[D].哈爾濱:哈爾濱工業(yè)大學(xué),2013.

[4] 陸元九.陀螺儀及慣性技術(shù)導(dǎo)航原理[M].北京:科學(xué)出版社,1964.

[ 5 ] KAZUSUKE M . Cur r e n t MEMS t e c h n o l o g y a n d MEMS sensors focusing on inertial sensors[C]. ICSICT,

Beijing,2008, IEEE:2008:2371-2374.

[6] D.H.TITTERTON, J.L.WESTON. Strap down inertial navigation technology[M]. London United Kingdom, The Institution of Electrical Engineers,1997.

[7] 尹德進(jìn).捷聯(lián)慣導(dǎo)系統(tǒng)六加速度計(jì)配置方案研究[J].中國慣性技術(shù)學(xué)報(bào),2003,11(2):48-51.

[8] 杜海龍.捷聯(lián)慣導(dǎo)系統(tǒng)姿態(tài)解算模塊的實(shí)現(xiàn)[J].光學(xué)精密工程,2008(10):1956-1962.

[9] 高梅國,劉國滿,田黎育.高速數(shù)字信號(hào)處理器結(jié)構(gòu)與系統(tǒng)[M].北京:清華大學(xué)出版社,2009.

[10] 李濤,練軍想,曹聚亮,等.GNSS與慣性及多傳感器組合導(dǎo)航系統(tǒng)原理[J]. 北京:國防工業(yè)出版社, 2011(11)78-135.

[11] 張復(fù)宜. SINS/GPS組合導(dǎo)航雙DSP硬件平臺(tái)的設(shè)計(jì)研究[D].哈爾濱:哈爾濱工程大學(xué),2012.

[12] 彭啟琮,李玉柏,管慶. DSP技術(shù)的發(fā)展與應(yīng)用[M].北京:高等教育出版社,2007.

[13] 紀(jì)杭辛.基于DSP的某型衛(wèi)星導(dǎo)航計(jì)算機(jī)信息處理系統(tǒng)設(shè)計(jì)[D].成都:電子科技大學(xué),2013.

[14] 李莎.捷聯(lián)慣性導(dǎo)航計(jì)算機(jī)小型化設(shè)計(jì)[J].導(dǎo)航與控制,2014(4):11-16.

[15] 金紅新.基于DSP的導(dǎo)航計(jì)算機(jī)研究[D].哈爾濱:哈爾濱工程大學(xué),2006.

[16] 孫光民.SINS/GPS組合導(dǎo)航系統(tǒng)設(shè)計(jì)與DSP實(shí)現(xiàn)[J].微計(jì)算機(jī)信息,2008(31):227-229.

[17] 汪振國.捷聯(lián)導(dǎo)航計(jì)算機(jī)的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)[D].哈爾濱:哈爾濱工程大學(xué),2013.

[18] 楊梟.光纖陀螺捷聯(lián)導(dǎo)航數(shù)據(jù)處理系統(tǒng)軟硬件設(shè)計(jì)與實(shí)現(xiàn)[D].哈爾濱:哈爾濱工程大學(xué),2007.

[19] Texas Incorporated.TMS320C6000 系列 DSP 的 CPU與外設(shè)[M].北京:清華大學(xué)出版社,2007.

[20] 羅陽.微慣性組合導(dǎo)航芯片體系結(jié)構(gòu)及其關(guān)鍵技術(shù)研究[D].長沙:國防科技大學(xué),2009.

[21] 李耀,崔燕.基于 Nios II 的導(dǎo)航系統(tǒng)平臺(tái)的設(shè)計(jì)[J].微計(jì)算機(jī)信息, 2006(32)2-3.

[22] LONG Da-feng.FPGA在組合導(dǎo)航系統(tǒng)中的應(yīng)用研究[J].機(jī)械工程與自動(dòng)化,2008(4):126-128.

(本文來源于《電子產(chǎn)品世界》雜志2023年2月期)

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<