對(duì)于系統(tǒng)設(shè)計(jì)工程師來(lái)說(shuō),時(shí)序問(wèn)題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫(xiě)窗口越來(lái)越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整地傳送到接收端,就必須進(jìn)行精確的時(shí)序計(jì)算和分析。同時(shí),時(shí)序和信號(hào)完整性也是密不可分的,良好的信號(hào)質(zhì)量是確保穩(wěn)定的時(shí)序的關(guān)鍵,由于反射,串?dāng)_造成的信號(hào)質(zhì)量問(wèn)題都很可能帶來(lái)時(shí)序的偏移和紊亂。因此,對(duì)于一個(gè)信號(hào)完整性工程師來(lái)說(shuō),如果不懂得系統(tǒng)時(shí)序的理論,那肯定是不稱職的。本章我們就普通時(shí)序(共同時(shí)鐘)和源同步系統(tǒng)時(shí)序等方面對(duì)系統(tǒng)時(shí)序的基礎(chǔ)知識(shí)作一些簡(jiǎn)單的介紹。

普通時(shí)序系統(tǒng)(共同時(shí)鐘系統(tǒng))

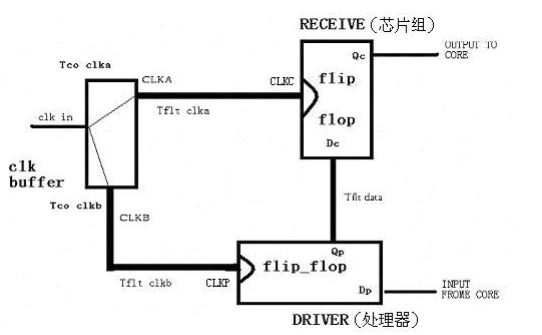

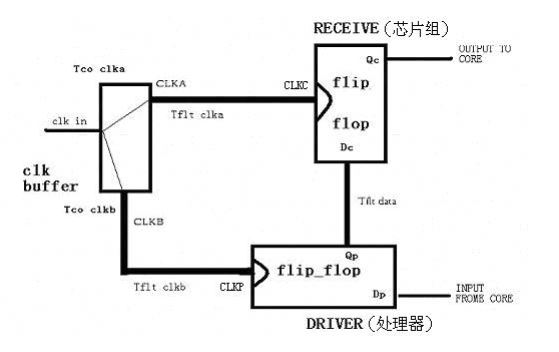

所謂普通時(shí)序系統(tǒng)就是指驅(qū)動(dòng)端和接收端的同步時(shí)鐘信號(hào)都是由一個(gè)系統(tǒng)時(shí)鐘發(fā)生器提供。下圖就是一個(gè)典型的普通時(shí)鐘系統(tǒng)的示意圖,表示的是計(jì)算機(jī)系統(tǒng)的前端總線的時(shí)序結(jié)構(gòu),即處理器(CPU)和芯片組(Chipset)之間的連接。

在這個(gè)例子中,驅(qū)動(dòng)端(處理器)向接收端(芯片組)傳送數(shù)據(jù),我們可以將整個(gè)數(shù)據(jù)傳送的過(guò)程考慮為三個(gè)步驟:

1.核心處理器提供數(shù)據(jù);

2.在第一個(gè)系統(tǒng)時(shí)鐘的上升沿到達(dá)時(shí),處理器將數(shù)據(jù)Dp鎖存至Qp輸出;

3.Qp沿傳輸線傳送到接收端觸發(fā)器的Dc,并在第二個(gè)時(shí)鐘上升沿到達(dá)時(shí),將數(shù)據(jù)傳送到芯片組內(nèi)部。一般來(lái)說(shuō),標(biāo)準(zhǔn)普通時(shí)鐘系統(tǒng)的時(shí)鐘信號(hào)到各個(gè)模塊是同步的,即圖中的Tflt clka和Tflt clkb延時(shí)相同。通過(guò)分析不難看出,整個(gè)數(shù)據(jù)從發(fā)送到接收的過(guò)程需要經(jīng)歷連續(xù)的兩個(gè)時(shí)鐘沿,也就是說(shuō),如果要使系統(tǒng)能正常工作,就必須在一個(gè)時(shí)鐘周期內(nèi)讓信號(hào)從發(fā)送端傳輸?shù)浇邮斩恕H绻盘?hào)的傳輸延遲大于一個(gè)時(shí)鐘周期,那么當(dāng)接收端的第二個(gè)時(shí)鐘沿觸發(fā)時(shí),就會(huì)造成數(shù)據(jù)的錯(cuò)誤讀取,因?yàn)檎_的數(shù)據(jù)還在傳輸?shù)倪^(guò)程中,這就是建立時(shí)間不足帶來(lái)的時(shí)序問(wèn)題。

目前普通時(shí)序系統(tǒng)的頻率無(wú)法得到進(jìn)一步提升的原因就在于此,頻率越高,時(shí)鐘周期越短,允許在傳輸線上的延時(shí)也就越小,200-300MHz已經(jīng)幾乎成為普通時(shí)序系統(tǒng)的頻率極限。那么,是不是傳輸延時(shí)保持越小就越好呢?當(dāng)然也不是的,因?yàn)樗€必須要滿足一定的保持時(shí)間。在接下來(lái)幾節(jié)里,我們就建立和保持時(shí)間來(lái)分析一下時(shí)序設(shè)計(jì)需要考慮的一些問(wèn)題以及正確的系統(tǒng)時(shí)序所必須滿足的條件。

時(shí)序參數(shù)的確定

對(duì)于時(shí)序問(wèn)題的分析,我們首先要清楚地理解相關(guān)的一些時(shí)序參數(shù)的具體含義,比如Tco,緩沖延時(shí),傳播延遲,最大/小飛行時(shí)間,建立時(shí)間,保持時(shí)間,建立時(shí)間裕量,保持時(shí)間裕量,時(shí)鐘抖動(dòng),時(shí)鐘偏移等等,如果對(duì)這些參數(shù)的概念理解不深刻,就很容易造成時(shí)序設(shè)計(jì)上的失誤。

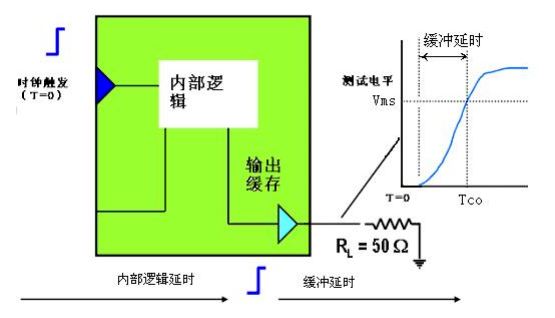

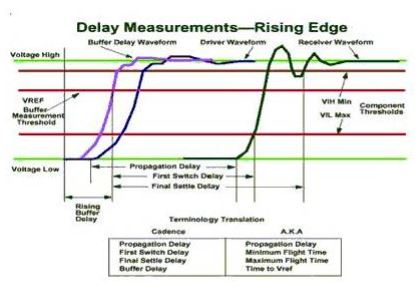

首先要闡明的是Tco和緩沖延時(shí)(buffer delay)的區(qū)別。從定義上來(lái)說(shuō),Tco是指時(shí)鐘觸發(fā)開(kāi)始到有效數(shù)據(jù)輸出的器件內(nèi)部所有延時(shí)的總和;而緩沖延時(shí)是指信號(hào)經(jīng)過(guò)緩沖器達(dá)到有效的電壓輸出所需要的時(shí)間。可以看出,Tco除了包含緩沖延時(shí),還包括邏輯延時(shí)。通常,確定Tco的方法是在緩沖輸出的末端直接相連一個(gè)測(cè)量負(fù)載,最常見(jiàn)的是50歐姆的電阻或者30pF的電容,然后測(cè)量負(fù)載上的信號(hào)電壓達(dá)到一定電平的時(shí)間,這個(gè)電平稱為測(cè)量電壓(Vms),一般是信號(hào)高電平的一半。如Tco和緩沖延時(shí)的確定如下圖所示:

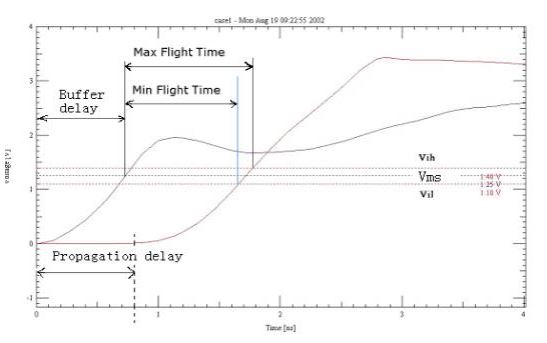

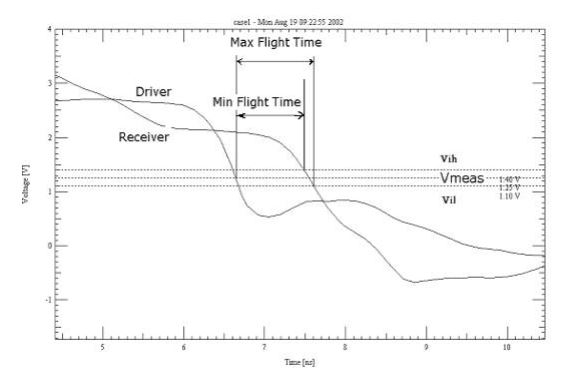

信號(hào)從緩沖器出來(lái)之后,就要經(jīng)過(guò)傳輸線到接收終端,信號(hào)在傳輸線上的傳輸?shù)难訒r(shí)我們稱為傳播延遲(propagationdelay),它只和信號(hào)的傳播速度和線長(zhǎng)有關(guān)。然而我們?cè)诖蠖鄶?shù)時(shí)序設(shè)計(jì)里面,最關(guān)鍵的卻不是傳播延遲這個(gè)參數(shù),而是飛行時(shí)間(Flight Time)參數(shù),包括最大飛行時(shí)間(Max Flight Time)和最小飛行時(shí)間(Min Flight Time)。飛行時(shí)間包含了傳播延遲和信號(hào)上升沿變化這兩部分因素,從下圖中可以很容易看出兩者的區(qū)別。

在較輕的負(fù)載(如單負(fù)載)情況下,驅(qū)動(dòng)端的上升沿幾乎和接收端的信號(hào)的上升沿平行,所以這時(shí)候平均飛行時(shí)間和傳播延遲相差不大;但如果在重負(fù)載(如多負(fù)載)的情況下,接收信號(hào)的上升沿明顯變緩,這時(shí)候平均飛行時(shí)間就會(huì)遠(yuǎn)遠(yuǎn)大于信號(hào)的傳播延遲。這里說(shuō)的平均飛行時(shí)間是指Buffer波形的Vms到接收端波形Vms之間的延時(shí),這個(gè)參數(shù)只能用于時(shí)序的估算,準(zhǔn)確的時(shí)序分析一定要通過(guò)仿真測(cè)量最大/最小飛行時(shí)間來(lái)計(jì)算。

上面只是對(duì)信號(hào)上升沿的分析,對(duì)于下降沿來(lái)說(shuō),同樣存在著最大/最小飛行時(shí)間的參數(shù),如下圖。在時(shí)序計(jì)算時(shí)我們實(shí)際取的最大飛行時(shí)間是在上升沿和下降沿中取最長(zhǎng)的那個(gè)飛行時(shí)間,而最小飛行時(shí)間則是取上升和下降沿中最短的那個(gè)飛行時(shí)間。

也有些時(shí)候,人們對(duì)信號(hào)的最大/最小飛行時(shí)間還有其它稱謂,比如在Cadence軟件中,就將最大飛行時(shí)間稱為最終穩(wěn)定延時(shí)(Final Settle Delay),而將最小飛行時(shí)間稱為最早開(kāi)關(guān)延時(shí)

(First SwitchDelay),如下圖。

信號(hào)經(jīng)過(guò)傳輸線到達(dá)接收端之后,就牽涉到建立時(shí)間和保持時(shí)間這兩個(gè)時(shí)序參數(shù),它們是接收器本身的特性,表征了時(shí)鐘邊沿觸發(fā)時(shí)數(shù)據(jù)需要在鎖存器的輸入端持續(xù)的時(shí)間。通俗地說(shuō),時(shí)鐘信號(hào)來(lái)的時(shí)候,要求數(shù)據(jù)必須已經(jīng)存在一段時(shí)間,這就是器件需要的建立時(shí)間(Setup Time);而時(shí)鐘邊沿觸發(fā)之后,數(shù)據(jù)還必須要繼續(xù)保持一段時(shí)間,以便能穩(wěn)定的讀取,這就是器件需要的保持時(shí)間(Hold Time)。如果數(shù)據(jù)信號(hào)在時(shí)鐘沿觸發(fā)前后持續(xù)的時(shí)間均超過(guò)建立和保持時(shí)間,那么超過(guò)量就分別被稱為建立時(shí)間裕量和保持時(shí)間裕量。見(jiàn)下圖,其中還考慮了時(shí)鐘誤差的因素。

每個(gè)器件的建立和保持時(shí)間參數(shù),一般都可以在相應(yīng)的DataSheet查到,對(duì)于設(shè)計(jì)者來(lái)說(shuō)最大的目的是提高時(shí)序的裕量,這樣即使信號(hào)完整性上出現(xiàn)一點(diǎn)問(wèn)題,或者外界環(huán)境發(fā)生一定的變化,系統(tǒng)仍然能正常工作,這就是一個(gè)設(shè)計(jì)優(yōu)良的系統(tǒng)應(yīng)該體現(xiàn)出的超強(qiáng)的穩(wěn)定性。

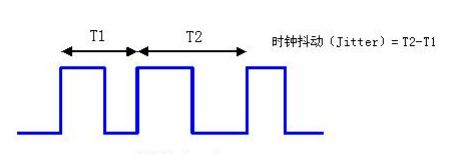

系統(tǒng)時(shí)序設(shè)計(jì)中對(duì)時(shí)鐘信號(hào)的要求是非常嚴(yán)格的,因?yàn)槲覀兯械臅r(shí)序計(jì)算都是以恒定的時(shí)鐘信號(hào)為基準(zhǔn)。但實(shí)際中時(shí)鐘信號(hào)往往不可能總是那么完美,會(huì)出現(xiàn)抖動(dòng)(Jitter)和偏移(Skew)問(wèn)題。所謂抖動(dòng),就是指兩個(gè)時(shí)鐘周期之間存在的差值,這個(gè)誤差是在時(shí)鐘發(fā)生器內(nèi)部產(chǎn)生的,和晶振或者PLL內(nèi)部電路有關(guān),布線對(duì)其沒(méi)有影響,如下圖。除此之外,還有一種由于周期內(nèi)信號(hào)的占空比發(fā)生變化而引起的抖動(dòng),稱之為半周期抖動(dòng)。總的來(lái)說(shuō),jitter可以認(rèn)為在時(shí)鐘信號(hào)本身在傳輸過(guò)程中的一些偶然和不定的變化之總和。

時(shí)鐘偏移(skew)是指兩個(gè)相同的系統(tǒng)時(shí)鐘之間的偏移。它表現(xiàn)的形式是多種多樣的,既包含了時(shí)鐘驅(qū)動(dòng)器的多個(gè)輸出之間的偏移,也包含了由于PCB走線誤差造成的接收端和驅(qū)動(dòng)端時(shí)鐘信號(hào)之間的偏移,比如在下圖中所示,CLKA和CLKB之間的差異,CLKC和CLKP之間的差異均為時(shí)鐘偏移,這些偏移量在時(shí)序計(jì)算中需要全部考慮。

除了上面提到的這些概念,還有一點(diǎn)要注意的是,時(shí)刻不能忽略信號(hào)完整性對(duì)時(shí)序的影響,比如串?dāng)_會(huì)影響微帶線傳播延遲;反射會(huì)造成數(shù)據(jù)信號(hào)在邏輯門(mén)限附近波動(dòng),從而影響最大/最小飛行時(shí)間;時(shí)鐘走線的干擾會(huì)造成一定的時(shí)鐘偏移。有些誤差或不確定因素是仿真中無(wú)法預(yù)見(jiàn)的,設(shè)計(jì)者只有通過(guò)周密的思考和實(shí)際經(jīng)驗(yàn)的積累來(lái)逐步提高系統(tǒng)設(shè)計(jì)的水平。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<