縱觀整個制造業(yè),,芯片的制造流程可以說是最復雜的之一,,這項點石成金術可分為八個大步驟,如下圖所示,,這些步驟又可細分為上百道工序。

制造硅晶圓

制造硅晶圓的原料是我們最常見的沙子,,沙子的主要成分是二氧化硅,,將沙子進行提純得到單質(zhì)硅,然后再通過直拉法得到單晶硅錠,,先將硅錠兩端切去,,再切成幾段,進行滾磨,,目的是使單晶硅棒達到標準直徑,。接下來采用X射線法確定單晶硅的晶向,切除參考面,,再以參考面為基準進行切割得到硅晶圓,,如下圖所示。

得到初步的晶圓后,,要將切好的硅晶圓進行倒角,、研磨處理,讓其表面變得平整光滑,,否則難以在上面刻制正確的電路,。研磨過后還要用化學腐蝕液去除研磨過程中的損傷,最后用拋光液進行拋光,,經(jīng)檢驗合格后,,即可交給產(chǎn)線進行制造了。

薄膜沉積

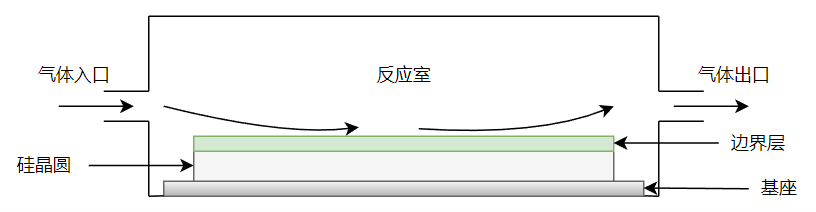

第二步到第六步是需要多次重復的過程,。薄膜沉積(deposition)是將材料薄膜沉積到晶圓表面上,,沉積材料可能是導體、半導體和絕緣體,,常見的薄膜有二氧化硅薄膜,、多晶硅薄膜、氮化硅薄膜,、金屬及化合物薄膜等,。常用的沉積方法有化學氣相沉積(Chemical Vapor Deposition,CVD) 和物理氣相沉積(Physical Vapor Deposition,,PVD),。CVD是把構成薄膜物質(zhì)的氣態(tài)反應劑或液態(tài)反應劑的蒸汽以合理的流速引入反應室,在襯底表面發(fā)生化學反應,沉積成膜的工藝方法,,如下圖所示,。

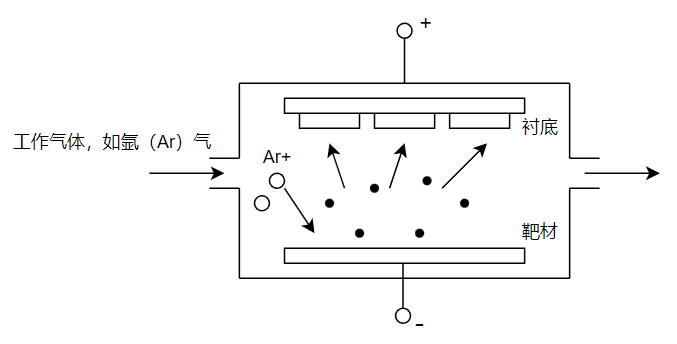

物理氣相沉積是指在真空條件下,采用物理方法,,將材料源(固體或液體)氣化成氣態(tài)原子或分子,,或部分電離成離子,轉(zhuǎn)移到硅襯底表面形成薄膜的過程,,如圖3-5所示,。PVD相比CVD而言,優(yōu)點是工藝原理簡單,、工藝所需溫度低,,能用于制備各種薄膜。缺點是臺階覆蓋(step-coverage)性,、附著性,、致密性不如CVD薄膜。

PVD的常見種類包括濺射鍍膜,、真空蒸鍍、等離子體鍍膜等,。以濺射鍍膜為例,,是指在一定真空度下,使氣體等離子化,,其中的離子轟擊靶材表面,,靶材表面的原子等粒子氣相轉(zhuǎn)移到達襯底,在襯底表面沉積成膜的過程,,如下圖所示,。

光刻

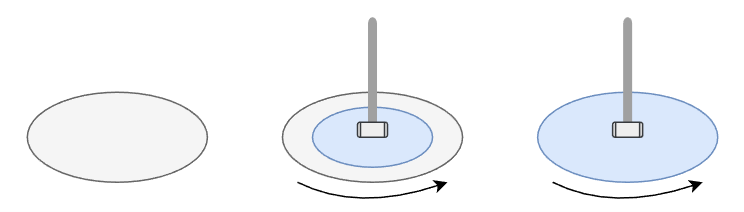

光刻是整個制造中最核心的一步。光刻前要在晶圓上均勻的涂上光刻膠(photoresist),,通常光刻膠采用旋涂的方式,,即邊旋轉(zhuǎn),邊涂抹,,保證光刻膠的均勻性,,如下圖所示。

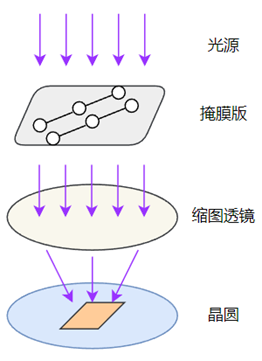

將涂光刻膠后的晶圓放入光刻機中,,光刻機的光源發(fā)出的深紫外(DUV)或極紫外(EUV)光透過掩模版(也稱作光罩),,將掩膜版上的電路結(jié)構圖案縮小并聚焦到光刻膠圖層上,光刻膠在受光后,,受光區(qū)域會發(fā)生化學變化,,掩膜版上的電路圖形就會印刻到光刻膠圖層上,此步驟稱為曝光,,如下圖所示,。曝光之后的步驟是烘烤和顯影,,目的是去除圖形未覆蓋區(qū)域的光刻膠,從而讓印刷好的電路圖案顯現(xiàn)出來,,永久固定,。

刻蝕

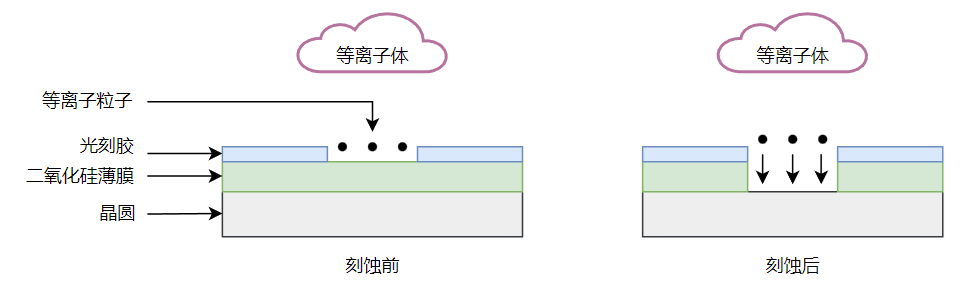

刻蝕(etch)是在光刻步驟完成后,用化學或物理方法有選擇地從硅片表面去除不需要的材料,,從而只留下3D電路圖的過程,。刻蝕方法主要包括濕法刻蝕(wet etching)和干法刻蝕(dry etching),,濕法刻蝕是指利用化學溶液與預刻蝕材料之間的化學反應來去除未被掩蔽膜材料掩蔽的部分而達到刻蝕目的,。干法刻蝕是用等離子體化學活性較強的性質(zhì)進薄膜刻蝕的技術,干法刻蝕又包括濺射刻蝕(Supptter Etching),、等離子體刻蝕(Plasma Etching),、反應離子刻蝕(Reactive Ion Etching,RIE),??涛g過程以等離子體刻蝕為例,利用等離子體中的粒子,,撞擊二氧化硅薄膜層,,達到去除多余氧化層的目的,如下圖所示,。

計量和檢測

刻蝕結(jié)束后要對晶圓計量和檢測,,確保沒有誤差。如果檢測結(jié)果不符合預期,,則應反饋至光刻或者刻蝕步驟,,做進一步的優(yōu)化及調(diào)整。事實上,,計量和檢測可以貫穿整個制造流程,。

離子注入

離子注入就是將要摻雜的原子(如Ⅲ、Ⅴ族元素),,在強電場的作用下,,被加速射入到晶圓的特定區(qū)域,再進行退火,、激活雜質(zhì),、修復晶格損傷等步驟,從而獲得所需的雜質(zhì)濃度,,最終形成N區(qū)或者P區(qū),。

互聯(lián)

互連就是講同一芯片內(nèi)各個獨立的元器件,通過一定的方式,連接成具有一定功能的電路模塊的技術,。用于互連工藝的金屬材料需具備低電阻率,、熱化學穩(wěn)定性好、抗電遷移特性佳,、易于沉積和刻蝕,、價格低廉等特征。集成電路發(fā)展早期主要使用鋁互連工藝,,但因為銅具有比鋁更低的電阻率,,和更好的抗電遷移特定,而被廣泛采用,。

從薄膜沉積到互連這六個步驟,,在整個制造流程中會重復幾十次甚至上百次,每一次重復,,都會在晶圓上刻制一層電路,,最終形成完整的芯片。以上所有步驟完成后,,對晶圓整體進行打磨,、拋光等,再進行測試及封裝,,合格的芯片就可以出廠交付了,!

更多信息可以來這里獲取==>>電子技術應用-AET<<