在很多網(wǎng)友的心目中,要提升芯片性能,就要推動(dòng)芯片工藝的進(jìn)步,比如從7nm到5nm,再到3nm,再到2nm。

而過(guò)去的這些年,芯片廠(chǎng)商、晶圓廠(chǎng)商都是這么教育市場(chǎng)、教育消費(fèi)者的,手機(jī)芯片、電腦從10nmn進(jìn)步到7nm,再進(jìn)步到5nm,再接著進(jìn)入3nm……

事實(shí)上,當(dāng)芯片進(jìn)入到3nm后,要再提升工藝到2nm,甚至到埃米級(jí)(1埃米=0.1nm)是非常困難的,因?yàn)槌杀咎吡耍愿鞔笮酒瑥S(chǎng)商們,也一直在探索不靠提升芯片工藝,來(lái)提升芯片性能。

前幾天臺(tái)積電、ARM、英特爾等10大芯片廠(chǎng)商成立的Chiplet聯(lián)盟,其實(shí)也是這個(gè)目的,通過(guò)封裝各和種不同工藝,不同廠(chǎng)商的小芯片粒,達(dá)到工藝不變,性能提升的目的。

而在Chiplet聯(lián)盟成立之外,臺(tái)積電也辦了另外一件事,那就是利用先進(jìn)的3D封裝技術(shù),讓7nm的芯片,比5nm還要強(qiáng)。

3月3日,英國(guó)的AI芯片公司Graphcore發(fā)布了一款I(lǐng)PU產(chǎn)品Bow,采用的就是臺(tái)積電7納米的3D封裝技術(shù),也是全球首顆3D封裝的芯片。

這顆芯片的性能較上代提升了40%、功耗提升了16%,而單個(gè)封裝中的晶體管數(shù)量超過(guò)了600億晶體管。

按照業(yè)內(nèi)人士的說(shuō)法,如果這顆芯片采用5nm工藝,未必比現(xiàn)在強(qiáng),也就是說(shuō)在采用了3D封裝技術(shù)后,7nm其實(shí)比5nm更強(qiáng)了。

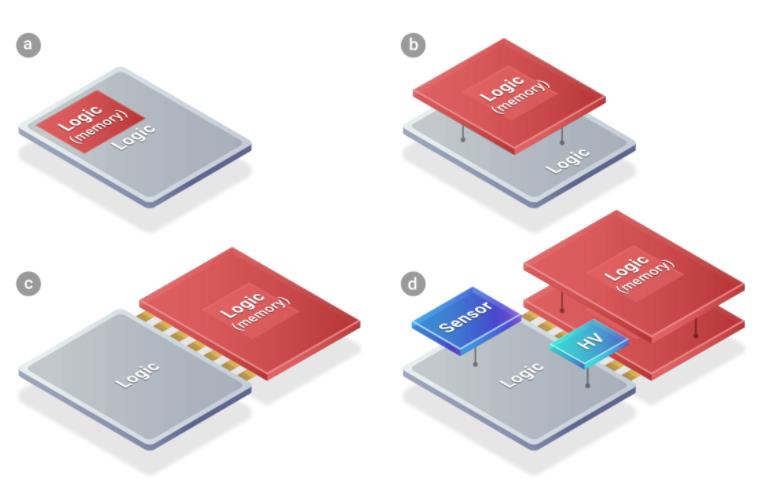

3D封裝技術(shù)究竟是什么技術(shù)?我們知道以前的芯片封裝時(shí),都是單個(gè)Die(硅片)進(jìn)行封裝,要想芯片性能好, 要么Die(硅片)的面積更大,要么工藝再提升。

而3D封裝技術(shù)不一樣,采用的是幾塊Die(硅片)垂直疊加在一起,搞幾層一起封裝成一顆芯片,這樣減少了面積,減輕了重量,還提升了性能,因?yàn)閱挝幻娣e內(nèi),Die的面積呈幾倍增加,自然晶體管的數(shù)量也是成倍增加了。

事實(shí)上,這也有一點(diǎn)像之前網(wǎng)上曝光的所謂的華為雙芯片疊加技術(shù),用兩塊14nm的芯片疊加起來(lái),實(shí)現(xiàn)7nm芯片的性能。

但這個(gè)更徹底一點(diǎn),不是兩顆芯片疊加,而是兩塊沒(méi)封裝的Die疊加,實(shí)現(xiàn)更強(qiáng)的性能,這遠(yuǎn)比封裝成芯片后再疊加,強(qiáng)大的多,成本更低,性能更好,功耗也可控得多。

而這顆芯片的誕生,也證明了芯片性能的提升并不一定要提升工藝,也可以升級(jí)封裝技術(shù),向先進(jìn)封裝轉(zhuǎn)移。

這無(wú)疑也是當(dāng)前眾多芯片廠(chǎng)商需要考慮和選擇的另外一個(gè)方面了,特別是國(guó)內(nèi)芯片工藝無(wú)法進(jìn)步時(shí),這種封裝技術(shù),更加重要。