如果說(shuō)在過(guò)去五年左右的芯片設(shè)計(jì)中有一個(gè)突出的,、全行業(yè)的趨勢(shì),那五一就是小芯片(chiplet)的使用越來(lái)越多,。隨著芯片制造商希望它們能解決從芯片制造成本到設(shè)計(jì)的整體可擴(kuò)展性等方方面面的問(wèn)題,,微型裸片已成為越來(lái)越普遍的特征,。無(wú)論是簡(jiǎn)單地將以前的單片 CPU 拆分成幾塊,還是將47 個(gè)小芯片放在一個(gè)封裝上,,小芯片已經(jīng)在今天的芯片設(shè)計(jì)中發(fā)揮著重要作用,,芯片制造商已經(jīng)明確表示它只是將來(lái)會(huì)成長(zhǎng)。

與此同時(shí),,經(jīng)過(guò) 5 年多的認(rèn)真,、大批量使用,小芯片和支撐它們的技術(shù)似乎終于在設(shè)計(jì)方面達(dá)到了一個(gè)拐點(diǎn),。芯片制造商已經(jīng)對(duì)小芯片的好處(和壞處)有了更充分的了解,,封裝供應(yīng)商已經(jīng)改進(jìn)了放置小芯片所需的超精確方法,工程團(tuán)隊(duì)已經(jīng)解決了用于讓小芯片相互通信的通信協(xié)議其他,。

簡(jiǎn)而言之,,小芯片不再是需要驗(yàn)證的實(shí)驗(yàn)性設(shè)計(jì),而是已成為芯片制造商可以依賴的經(jīng)過(guò)驗(yàn)證的設(shè)計(jì),。隨著對(duì)小芯片技術(shù)的日益依賴,,對(duì)設(shè)計(jì)路線圖和穩(wěn)定性的需求也隨之而來(lái)——對(duì)設(shè)計(jì)標(biāo)準(zhǔn)的需求也順勢(shì)而至。

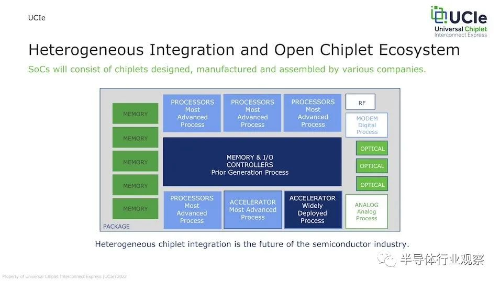

為此,,今天英特爾,、AMD、Arm 和所有三個(gè)領(lǐng)先的代工廠商齊聚一堂,,宣布他們正在為小芯片互連制定一個(gè)新的開(kāi)放標(biāo)準(zhǔn),,該標(biāo)準(zhǔn)被恰當(dāng)?shù)孛麨?a class="innerlink" href="http://wldgj.com/tags/UCIe" target="_blank">UCIe(Universal Chiplet Interconnect Express,). 這個(gè)名字從非常成功的 PCI-Express 不愛(ài)準(zhǔn)中汲取靈感,相關(guān)公司正在與 UCIe 一起創(chuàng)建連接小芯片的標(biāo)準(zhǔn),,目標(biāo)是制定一套標(biāo)準(zhǔn),,不僅簡(jiǎn)化所有相關(guān)參與者的流程,而且引領(lǐng)走向來(lái)自不同制造商的小芯片之間的完全互操作性,,允許芯片在芯片制造商認(rèn)為合適的情況下混合和匹配小芯片,。

換句話說(shuō),要從小芯片中構(gòu)建一個(gè)完整且兼容的生態(tài)系統(tǒng),就像今天的基于 PCIe 的擴(kuò)展卡的生態(tài)系統(tǒng)一樣,。

與 PCIe 的比較適用于多個(gè)層面,,這可能是快速了解 UCIe 小組目標(biāo)的最佳方式,。不僅新標(biāo)準(zhǔn)以開(kāi)放的方式提供,,相關(guān)公司還將在今年晚些時(shí)候建立一個(gè)正式的聯(lián)盟組來(lái)管理 UCIe 并進(jìn)一步開(kāi)發(fā)它。同時(shí),,從一般技術(shù)的角度來(lái)看,,小芯片的使用是集成電路不斷整合的最新舉措,因?yàn)樵絹?lái)越小的晶體管允許越來(lái)越多的功能被集成到芯片上,。從本質(zhì)上講,,到目前為止,一直在擴(kuò)展卡或單獨(dú)芯片上的功能正在開(kāi)始進(jìn)入芯片/SoC 本身,。所以就像 PCIe 調(diào)節(jié)這些部件如何作為擴(kuò)展卡一起工作一樣,,

最終,UCIe 背后的團(tuán)隊(duì)的既定目標(biāo)是為小芯片建立一個(gè)開(kāi)放且無(wú)處不在的生態(tài)系統(tǒng),。無(wú)論這意味著簡(jiǎn)單地將某些物理方面標(biāo)準(zhǔn)化以簡(jiǎn)化制造,,還是實(shí)現(xiàn)真正的混合匹配設(shè)置,客戶可以從多個(gè)芯片(let)制造商處請(qǐng)求使用小芯片構(gòu)建的芯片,,這些都需要一個(gè)強(qiáng)大的基礎(chǔ)標(biāo)準(zhǔn)來(lái)實(shí)現(xiàn)這,。芯片制造行業(yè)的主要參與者都在支持 UCIe 以實(shí)現(xiàn)這一目標(biāo)。

為什么是小芯片,?

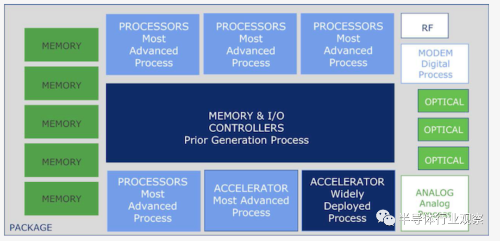

反過(guò)來(lái),,發(fā)生所有這一切的原因是Chiplet被越來(lái)越多地使用——在某些情況下更是唯一選擇。小芯片已經(jīng)被用于混合來(lái)自多個(gè)芯片制造商或來(lái)自多個(gè)工藝節(jié)點(diǎn)的裸片,,并且它們被用于構(gòu)建由于標(biāo)線限制而無(wú)法實(shí)現(xiàn)的大型芯片,。所有這些都是由某種方式的經(jīng)濟(jì)驅(qū)動(dòng)(如不是為芯片的每個(gè)部分使用昂貴的尖端節(jié)點(diǎn)),或者是希望以一種比花費(fèi)數(shù)年時(shí)間流片單片芯片更方便的方式結(jié)合不同制造商的 IP,??梢钥隙ǖ氖牵瑔纹酒鳛橐粋€(gè)整體并沒(méi)有完全消失(移動(dòng)數(shù)據(jù)仍然很昂貴),,但芯片設(shè)計(jì)的經(jīng)濟(jì)性正在無(wú)情地推動(dòng)芯片在更多情況下的使用,。

與此同時(shí),對(duì)性能和效率的推動(dòng)也推動(dòng)了對(duì)小芯片的持續(xù)興趣,?;蛘吒唧w地說(shuō),推動(dòng)了將更多功能集成到單個(gè)芯片封裝上的愿望,。PCIe 盡管速度很快,,但按照芯片標(biāo)準(zhǔn)來(lái)看仍然很慢;從 CPU 到控制器(然后再返回)的長(zhǎng)走線長(zhǎng)度會(huì)增加很多延遲,并且將數(shù)據(jù)推送到那么遠(yuǎn)的地方在功率方面相對(duì)昂貴,。因此,,芯片制造商越來(lái)越希望將這些功能集成到芯片上,以降低延遲并降低功耗,。對(duì)于小芯片(以及 UCIe),,這意味著能夠?qū)⑿阅芴岣?20 倍以上,并將功耗降低大致相同的數(shù)量,。

UCIe 1.0:新的 Die-To-Die 規(guī)范,,頂部有 PCIe 和 CXL,今日上市

深入研究 UCIe 規(guī)范的第一個(gè)修訂版,,我們發(fā)現(xiàn)一些非常簡(jiǎn)單的東西,,以及圍繞當(dāng)今封裝技術(shù)的功能非常明確地設(shè)計(jì)的東西。今天,,UCIe 帶來(lái)的不是新技術(shù),,而是當(dāng)前技術(shù)的不同實(shí)現(xiàn)之間的標(biāo)準(zhǔn)化,以便每個(gè)人都有共同的基礎(chǔ)來(lái)工作,。

不足為奇的是,,這個(gè)初始版本的 UCIe 來(lái)自英特爾,英特爾將規(guī)范貢獻(xiàn)給業(yè)界,,并將成為 UCIe 聯(lián)盟,。幾十年來(lái),英特爾一直負(fù)責(zé)多項(xiàng)備受矚目的開(kāi)放式互連技術(shù)的初步開(kāi)發(fā)——其中最重要的是 USB,、PCIe 和 Thunderbolt 3,。單即使如此,在他們看中的下一波計(jì)算浪潮技術(shù)的基礎(chǔ)上,,看到他們捐贈(zèng)另差距互連技術(shù)來(lái)幫助行業(yè)發(fā)展依然會(huì)讓人有少許震驚,。不過(guò),請(qǐng)不要誤會(huì),,這不是英特爾獨(dú)有的舉措,,支持新標(biāo)準(zhǔn)的公司以及即將組建的聯(lián)盟就是明證。(只要你看到有來(lái)自英特爾和 AMD 的高級(jí)研究員在同一個(gè)簡(jiǎn)報(bào)電話中,,你就知道發(fā)生了大事)

UCIe 借鑒了英特爾早期的高級(jí)接口總線 (AIB) 技術(shù),。英特爾此前曾在 2020 年將該技術(shù)捐贈(zèng)給 CHIPS 聯(lián)盟,因此這不是英特爾第一次以開(kāi)放的方式發(fā)布該技術(shù)的一個(gè)版本,。但 UCIe 是迄今為止規(guī)模最大(也是最專注于小芯片)的努力,,英特爾的晶圓廠競(jìng)爭(zhēng)對(duì)手以及 CPU 設(shè)計(jì)競(jìng)爭(zhēng)對(duì)手的支持就是明證。

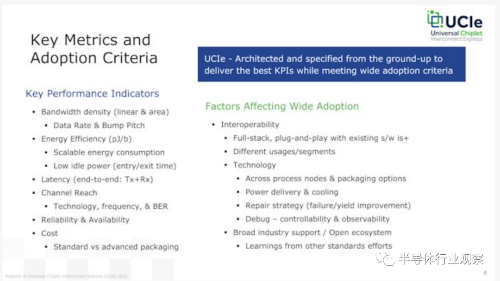

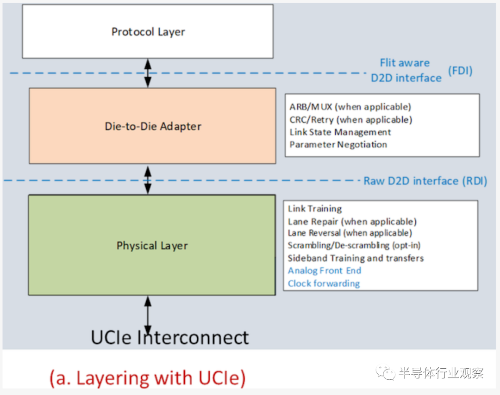

至于UCIe規(guī)范本身,,我們來(lái)談?wù)勊隽耸裁?,不包括什么,。該?guī)范涵蓋了物理層,列出了小芯片相互通信的電氣信號(hào)標(biāo)準(zhǔn),,以及物理通道的數(shù)量和支持的凸塊間距,。該規(guī)范涵蓋了協(xié)議層,定義了覆蓋在這些信號(hào)上的更高級(jí)別的協(xié)議,,以了解所有內(nèi)容并提供必要的功能集,。

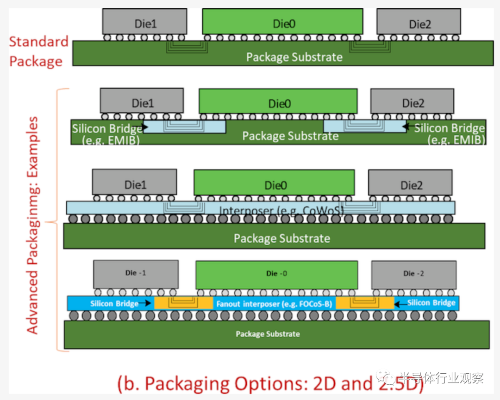

然而,規(guī)范沒(méi)有涵蓋的是用于在小芯片之間提供物理鏈接的封裝/橋接技術(shù),。例如,,這不是英特爾放棄 EMIB 或 Foveros,。相反,,UCIe 與橋接無(wú)關(guān)。小芯片可以通過(guò)扇出橋,、硅中介層,、EMIB 連接,甚至在帶寬較低的設(shè)備的情況下,,甚至只是一個(gè)普通的舊有機(jī)基板,。UCIe 旨在與所有這些一起工作,因?yàn)闃虮旧肀举|(zhì)上是一個(gè)dumb pipe ,,用于在小芯片之間傳輸電信號(hào),。只要一個(gè)小芯片符合標(biāo)準(zhǔn)(包括凸塊間距),它就可以與另一個(gè) UCIe 小芯片通信,。

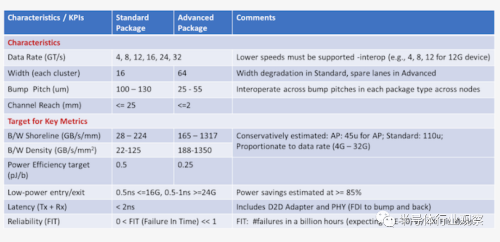

關(guān)于這一點(diǎn),,UCIe 1.0 基本上具有兩個(gè)性能/復(fù)雜性標(biāo)準(zhǔn)級(jí)別。恰當(dāng)命名的“標(biāo)準(zhǔn)封裝”級(jí)別的規(guī)格是為使用傳統(tǒng)有機(jī)基板的低帶寬設(shè)備設(shè)計(jì)的,。這些部件將使用多達(dá) 16 條數(shù)據(jù)通道,、100μm + 凸塊間距和擴(kuò)展通道長(zhǎng)度。在高層次上,,這就像通過(guò)現(xiàn)代 PCIe 鏈路連接兩個(gè)設(shè)備,,但將它們放置得更近了。

同時(shí),,第二套規(guī)范涵蓋了 UCIe 小組看似“高級(jí)封裝”的內(nèi)容,,涵蓋了所有基于高密度硅橋的技術(shù),如 EMIB 和 InFO,。先進(jìn)的封裝規(guī)格要求更小的凸塊間距(大約 25μm 到 55μm)以及由于更高的密度和小于 2mm 的非常短的通道范圍,,每個(gè)集群的通道數(shù)是 4 倍。UCIe 推廣者采用最全面的配置,,相信采用當(dāng)今 45μm 凸點(diǎn)間距技術(shù)的先進(jìn)封裝設(shè)置將能夠提供高達(dá) 1.3TB/s/mm 的“ shoreline”(線性)帶寬,。也就是說(shuō),,每秒1.3TB的數(shù)據(jù)可以從芯片的1mm邊緣通過(guò)。

我不會(huì)在這里對(duì)每一個(gè)數(shù)字都詳細(xì)解讀,,但可以肯定的是,,所有這些都是為了強(qiáng)調(diào) UCIe 是如何設(shè)置為滿足性能范圍兩端的小芯片需求的。對(duì)于只需要以具有成本效益的方式將兩個(gè)小芯片組合在一個(gè)封裝上的芯片制造商來(lái)說(shuō),,有標(biāo)準(zhǔn)封裝方法,。對(duì)于需要使兩個(gè)小芯片的性能盡可能接近單個(gè)單片芯片的芯片制造商來(lái)說(shuō),先進(jìn)的封裝規(guī)范允許大量通道,,從而提供大量帶寬,。

同時(shí),有趣的是要注意發(fā)起人在延遲和能源效率方面的期望,。對(duì)于所有封裝類型,,延遲預(yù)計(jì)將低于 2ns,這在拆分以前單片芯片設(shè)計(jì)的小芯片設(shè)計(jì)中尤其重要,。同時(shí),,電源效率范圍從標(biāo)準(zhǔn)封裝的低 0.5 pJ/bit 到高級(jí)封裝的更低 0.25 pJ/b。這有助于說(shuō)明為什么一些芯片制造商渴望加入小芯片,,因?yàn)閷?duì)離散 PCIe/CXL 卡的改進(jìn)可能是顯著的,。

反過(guò)來(lái),連接小芯片的物理層對(duì)于 UCIe 來(lái)說(shuō)是新的,。英特爾和其他推動(dòng)者并沒(méi)有深入探討其工作原理,,但在較高級(jí)別上,物理層標(biāo)準(zhǔn)提供了電信號(hào),、時(shí)鐘,、鏈路訓(xùn)練和邊帶信號(hào)。一個(gè) 256 字節(jié)的流控制單元 (FLIT) 依次處理實(shí)際的數(shù)據(jù)傳輸,。

在此之上是一個(gè)中間層,,該組織稱之為 Die-to-Die Adapter。D2D 為小芯片之間的鏈路狀態(tài)管理和參數(shù)協(xié)商提供了基礎(chǔ),。D2D 還負(fù)責(zé)通過(guò) CRC 和鏈路級(jí)重試為額外的數(shù)據(jù)可靠性保護(hù)提供可選支持,。

最后,在協(xié)議層,,小芯片制造商有幾個(gè)不同的選擇,。UCIe 的官方標(biāo)準(zhǔn)化協(xié)議是 PCI-Express 及其緩存一致的“表親”,Compute Express Link,,它本身構(gòu)建在 PCIe 之上,。在這里討論他們的選擇時(shí),UCIe 的推動(dòng)者選擇了務(wù)實(shí)的方法:PCIe 和 CXL 已經(jīng)得到了全行業(yè)的支持,,因此他們不會(huì)自己重新發(fā)明輪子,,而是要利用協(xié)議層的現(xiàn)有生態(tài)系統(tǒng),。這意味著 UCIe 正在以一個(gè)完全充實(shí)且經(jīng)過(guò)充分驗(yàn)證的協(xié)議層開(kāi)始運(yùn)行,該協(xié)議層可以提供可靠的數(shù)據(jù)傳輸和鏈路管理,,以及緩存一致性等額外的定制功能,。也許同樣重要的是,這意味著客戶和芯片制造商都可以利用他們現(xiàn)有的 PCIe/CXL 軟件投資,,

在實(shí)踐中,,如果 UCIe沒(méi)有以這種方式利用 PCIe/CXL ,我會(huì)感到更加驚訝,。PCIe 技術(shù)已成為其他各種技術(shù)的支柱,,整個(gè)行業(yè)已經(jīng)不再試圖在基本設(shè)備互連需求方面超越 PCIe。

也就是說(shuō),,發(fā)起人已經(jīng)明確表示,,UCIe 并不僅限于 PCIe/CXL。如果出現(xiàn)某些問(wèn)題并且所有者愿意將其捐贈(zèng)給該標(biāo)準(zhǔn),,則該標(biāo)準(zhǔn)的未來(lái)版本可能會(huì)添加其他協(xié)議,。

最后,,芯片制造商也可以自由使用他們自己的定制/定制協(xié)議,;它們不僅限于使用PCIe /CXL。UCIe 支持允許使用任何其他協(xié)議的原始/流式協(xié)議選項(xiàng),。當(dāng)然,,兩個(gè)小芯片都需要支持這種自定義協(xié)議才能建立連接,但即使在這種情況下,,這也將允許芯片制造商利用 UCIe 標(biāo)準(zhǔn)的物理方面來(lái)簡(jiǎn)化他們自己的設(shè)計(jì)/生產(chǎn),。

這也意味著現(xiàn)有的互連協(xié)議,例如 AMD 的 Infinity Fabric,,即使引入了 UCIe,,也不太可能出現(xiàn)在任何地方。像 IF 這樣的協(xié)議仍然比 PCIe/CXL 的能力要復(fù)雜和專業(yè)得多,,考慮到連接 CPU 內(nèi)核和 I/O 芯片的非常具體的一致性要求,,這是有道理的。換句話說(shuō),,chiplet 設(shè)計(jì)的最前沿仍然領(lǐng)先于 UCIe 1.0 的起點(diǎn),。

長(zhǎng)期發(fā)展:UCIe 也適用于外部互連?,!

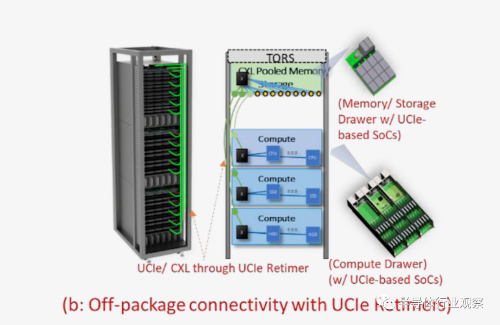

盡管 UCIe 的首要重點(diǎn)是為小芯片提供片上互連,,但該標(biāo)準(zhǔn)實(shí)際上包含了片外的規(guī)定。芯片外的方式,。

如果芯片/系統(tǒng)制造商愿意,,該規(guī)范允許使用重定時(shí)器在協(xié)議級(jí)別傳輸更遠(yuǎn)距離的 UCIe,。誠(chéng)然,這確實(shí)通過(guò)增加(很多)距離而犧牲了延遲和功率優(yōu)勢(shì),。但是 UCIe 推廣者設(shè)想服務(wù)器客戶使用它在機(jī)架或 pod 級(jí)別提供 UCIe 連接,,即使在長(zhǎng)距離上也能提供直接的小芯片到小芯片的連接。

這種設(shè)置最有趣和最明顯的用例是硅光子學(xué),。在那里擴(kuò)展小芯片概念,,芯片制造商可以在封裝邊緣構(gòu)建一個(gè)共同封裝的光收發(fā)器,然后使用 UCIe 將其連接到另一個(gè)小芯片,。這將允許直接從芯片進(jìn)行光學(xué)互連,,繞過(guò)使用片外收發(fā)器的需求(和電力成本)。

發(fā)起人還展示了基于外部存儲(chǔ)器/存儲(chǔ)設(shè)備的概念,。以及帶有更多 SoC 的外部機(jī)架/繪圖,。

UCIe 1.0 只是一個(gè)開(kāi)始

雖然今天發(fā)布了 UCIe 1.0 規(guī)范,但該標(biāo)準(zhǔn)的推動(dòng)者已經(jīng)將目光投向了該技術(shù)以及聯(lián)盟本身的未來(lái),。

UCIe 1.0 在很大程度上是一個(gè)“起點(diǎn)”標(biāo)準(zhǔn),,它最初是在英特爾內(nèi)部以單獨(dú)的方式開(kāi)發(fā)的。如前所述,,該聯(lián)盟將研究其他可能的協(xié)議以添加到標(biāo)準(zhǔn)中,。到目前為止,該標(biāo)準(zhǔn)只定義了他們認(rèn)為是小芯片設(shè)計(jì)的四個(gè)方面中的兩個(gè):物理層和通信協(xié)議,。該小組希望通過(guò)定義標(biāo)準(zhǔn)化的小芯片形狀因素,,甚至管理其他小芯片,進(jìn)一步使混合搭配的小芯片生態(tài)系統(tǒng)成為現(xiàn)實(shí),。

這是在芯片封裝技術(shù)不斷變化的基礎(chǔ)上,,這些技術(shù)仍在進(jìn)步。UCIe 1.0 標(biāo)準(zhǔn)基本上只針對(duì) 2D 和 2.5D 芯片封裝定義,,而不是像即將推出的 Foveros Direct 這樣的 3D 直接芯片對(duì)芯片技術(shù),。隨著 3D 芯片封裝的推出,標(biāo)準(zhǔn)將需要更新以考慮提供的新功能以及更高的密度,。

但為此,,UCIe 將需要一個(gè)合適的聯(lián)盟來(lái)支持它,這就是為什么今天的公告既是對(duì)新標(biāo)準(zhǔn)的啟示,,也是對(duì)其他公司加入并幫助開(kāi)發(fā)標(biāo)準(zhǔn)的未來(lái)迭代的宣傳,。UCIe 發(fā)起人團(tuán)體已經(jīng)是一個(gè)非常龐大的名單,其中包括芯片/IP 設(shè)計(jì)師 AMD,、Arm,、英特爾和高通、芯片工廠臺(tái)積電和三星(和英特爾),、芯片封裝公司 Advanced Semiconductor Engineering 和云計(jì)算提供商谷歌,、微軟和 Meta的支持,,。

簡(jiǎn)而言之,,它是芯片行業(yè)許多大玩家(無(wú)論是生產(chǎn)者還是消費(fèi)者)的名人錄,,但發(fā)起人正在尋找更多成員。務(wù)實(shí)地說(shuō),,該標(biāo)準(zhǔn)得到的認(rèn)可越多,,它就越有效和被廣泛采用,但該小組也受益于其他公司的意見(jiàn),,并了解他們的計(jì)算需求是什么,。