1.什么是DPU

DPU(Data Processing Unit)是以數(shù)據(jù)為中心構(gòu)造的專用處理器,采用軟件 定義技術(shù)路線支撐基礎(chǔ)設(shè)施層資源虛擬化,支持存儲、安全、服務(wù)質(zhì)量管理等 基礎(chǔ)設(shè)施層服務(wù)。2020年NVIDIA公司發(fā)布的DPU產(chǎn)品戰(zhàn)略中將其定位為數(shù)據(jù)中 心繼CPU和GPU之后的“第三顆主力芯片”,掀起了一波行業(yè)熱潮。DPU的出 現(xiàn)是異構(gòu)計算的一個階段性標(biāo)志。與GPU的發(fā)展類似,DPU是應(yīng)用驅(qū)動的體系 結(jié)構(gòu)設(shè)計的又一典型案例;但與GPU不同的是,DPU面向的應(yīng)用更加底層。DPU要解決的核心問題是基礎(chǔ)設(shè)施的“降本增效”,即將“CPU處理效率低 下、GPU處理不了”的負載卸載到專用DPU,提升整個計算系統(tǒng)的效率、降低 整體系統(tǒng)的總體擁有成本(TCO)。DPU的出現(xiàn)也許是體系結(jié)構(gòu)朝著專用化路 線發(fā)展的又一個里程碑。

關(guān)于DPU中“D”的解釋

DPU中的“D”有三種解釋:

(1)Data Processing Unit,即數(shù)據(jù)處理器。這種解釋把“數(shù)據(jù)”放在核心 位置,區(qū)別于信號處理器、基帶處理器等通信相關(guān)的處理器對應(yīng)的“信號”, 也區(qū)別于GPU對應(yīng)的圖形圖像類數(shù)據(jù),這里的“數(shù)據(jù)”主要指數(shù)字化以后的各 種信息,特別是各種時序化、結(jié)構(gòu)化的數(shù)據(jù),比如大型的結(jié)構(gòu)化表格,網(wǎng)絡(luò)流 中的數(shù)據(jù)包,海量的文本等等。DPU就是處理這類數(shù)據(jù)的專用引擎。

(2)Datacenter Processing Unit,即數(shù)據(jù)中心處理器。這種解釋把數(shù)據(jù)中心 作為DPU的應(yīng)用場景,特別是隨著WSC(Warehouse-scale Computer)的興起, 不同規(guī)模的數(shù)據(jù)中心成為了IT核心基礎(chǔ)設(shè)施。目前來看,DPU確實在數(shù)據(jù)中心 中使用前景非常廣闊。但是計算中心的三大部分:計算、網(wǎng)絡(luò)、存儲,計算部分是CPU占主導(dǎo),GPU輔助;網(wǎng)絡(luò)部分是路由器和交換機,存儲部分是高密度 磁盤構(gòu)成的的RAID系統(tǒng)和SSD為代表非易失性存儲系統(tǒng)。在計算和網(wǎng)絡(luò)中扮演 數(shù)據(jù)處理的芯片都可以稱之為Datacenter Processing Unit,所以這種說法相對比 較片面。

(3)Data-centric Processing Unit,即以數(shù)據(jù)為中心的處理器。Data-centric, 即數(shù)據(jù)為中心,是處理器設(shè)計的一種理念,相對于“Control-centric”即控制為 中心。經(jīng)典的馮諾依曼體系結(jié)構(gòu)就是典型的控制為中心的結(jié)構(gòu),在馮諾依曼經(jīng) 典計算模型中有控制器、計算器、存儲器、輸入和輸出,在指令系統(tǒng)中的表現(xiàn) 是具有一系列非常復(fù)雜的條件跳轉(zhuǎn)和尋址指令。而數(shù)據(jù)為中心的理念與數(shù)據(jù)流 (Data Flow)計算一脈相承,是一種實現(xiàn)高效計算的方法。同時,現(xiàn)在試圖打 破訪存墻(Memory Wall)的各種近存(Near-memory)計算、存內(nèi)(Inmemory)計算、存算一體等技術(shù)路線,也符合數(shù)據(jù)為中心的設(shè)計理念。

以上三種關(guān)于“D”的解釋,從不同角度反映DPU的特征,都有一定的可 取之處,筆者認為可以作為不同的三個維度來理解DPU的內(nèi)涵。

DPU的作用

DPU最直接的作用是作為CPU的卸載引擎,接管網(wǎng)絡(luò)虛擬化、硬件資源池 化等基礎(chǔ)設(shè)施層服務(wù),釋放CPU的算力到上層應(yīng)用。以網(wǎng)絡(luò)協(xié)議處理為例,要 線速處理10G的網(wǎng)絡(luò)需要的大約4個Xeon CPU的核,也就是說,單是做網(wǎng)絡(luò)數(shù)據(jù) 包處理,就可以占去一個8核高端CPU一半的算力。如果考慮40G、100G的高速 網(wǎng)絡(luò),性能的 開銷就 更 加 難 以 承 受 了。A m a z o n 把這些開銷都稱 之 為 “Datacenter Tax”,即還未運行業(yè)務(wù)程序,先接入網(wǎng)絡(luò)數(shù)據(jù)就要占去的計算資 源。AWS Nitro產(chǎn)品家族旨在將數(shù)據(jù)中心開銷(為虛擬機提供遠程資源,加密解 密,故障跟蹤,安全策略等服務(wù)程序)全部從CPU卸載到Nitro加速卡上,將給 上層應(yīng)用釋放30%的原本用于支付“Tax” 的算力!

DPU可以成為新的數(shù)據(jù)網(wǎng)關(guān),將安全隱私提升到一個新的高度。在網(wǎng)絡(luò)環(huán) 境下,網(wǎng)絡(luò)接口是理想的隱私的邊界,但是加密、解密算法開銷都很大,例如 國密標(biāo)準(zhǔn)的非對稱加密算法SM2、哈希算法SM3和對稱分組密碼算法SM4。如果 用CPU來處理,就只能做少部分數(shù)據(jù)量的加密。在未來,隨著區(qū)塊鏈承載的業(yè) 務(wù)的逐漸成熟,運行共識算法POW,驗簽等也會消耗掉大量的CPU算力。而這 些都可以通過將其固化在DPU中來實現(xiàn),甚至DPU將成為一個可信根。

DPU也可以成為存儲的入口,將分布式的存儲和遠程訪問本地化。隨著 SSD性價比逐漸可接受,部分存儲遷移到SSD器件上已經(jīng)成為可能,傳統(tǒng)的面向 機械硬盤的SATA協(xié)議并不適用于SSD存儲,所以,將SSD通過本地PCIe或高速 網(wǎng)絡(luò)接入系統(tǒng)就成為必選的技術(shù)路線。NVMe(Non Volatile Memory Express) 就是用于接入SSD存儲的高速接口標(biāo)準(zhǔn)協(xié)議,可以通過PCIe作為底層傳輸協(xié) 議,將SSD的帶寬優(yōu)勢充分發(fā)揮出來。同時,在分布式系統(tǒng)中,還可通過 NVMe over Fabrics(NVMe-oF)協(xié)議擴展到InfiniBand、Ethernet、或Fibre channel節(jié)點中,以RDMA的形式實現(xiàn)存儲的共享和遠程訪問。這些新的協(xié)議處 理都可以集成在DPU中以實現(xiàn)對CPU的透明處理。進而,DPU將可能承接各種 互連協(xié)議控制器的角色,在靈活性和性能方面達到一個更優(yōu)的平衡點。

DPU將成為算法加速的沙盒,成為最靈活的加速器載體。DPU不完全是一 顆固化的ASIC,在CXL、CCIX等標(biāo)準(zhǔn)組織所倡導(dǎo)CPU、GPU與DPU等數(shù)據(jù)一致 性訪問協(xié)議的鋪墊下,將更進一步掃清DPU編程障礙,結(jié)合FPGA等可編程器 件,可定制硬件將有更大的發(fā)揮空間,“軟件硬件化”將成為常態(tài),異構(gòu)計算 的潛能將因各種DPU的普及而徹底發(fā)揮出來。在出現(xiàn)“Killer Application”的領(lǐng) 域都有可能出現(xiàn)與之相對應(yīng)的DPU,諸如傳統(tǒng)數(shù)據(jù)庫應(yīng)用如OLAP、OLTP, 5G 邊緣計算,智能駕駛V2X等等。

2.DPU的發(fā)展背景

DPU的出現(xiàn)是異構(gòu)計算的又一個階段性標(biāo)志。摩爾定律放緩使得通用CPU 性能增長的邊際成本迅速上升,數(shù)據(jù)表明現(xiàn)在CPU的性能年化增長(面積歸一 化之后)僅有3%左右1,但計算需求卻是爆發(fā)性增長,這幾乎是所有專用計算芯 片得以發(fā)展的重要背景因素。以AI芯片為例,最新的GPT-3等千億級參數(shù)的超 大型模型的出現(xiàn),將算力需求推向了一個新的高度。DPU也不例外。隨著2019 年我國以信息網(wǎng)絡(luò)等新型基礎(chǔ)設(shè)施為代表的“新基建”戰(zhàn)略帷幕的拉開,5G、 千兆光纖網(wǎng)絡(luò)建設(shè)發(fā)展迅速,移動互聯(lián)網(wǎng)、工業(yè)互聯(lián)網(wǎng)、車聯(lián)網(wǎng)等領(lǐng)域發(fā)展日 新月異。云計算、數(shù)據(jù)中心、智算中心等基礎(chǔ)設(shè)施快速擴容。網(wǎng)絡(luò)帶寬從主流 10G朝著25G、40G、100G、200G甚至400G發(fā)展。網(wǎng)絡(luò)帶寬和連接數(shù)的劇增使得 數(shù)據(jù)的通路更寬、更密,直接將處于端、邊、云各處的計算節(jié)點暴露在了劇增 的數(shù)據(jù)量下,而CPU的性能增長率與數(shù)據(jù)量增長率出現(xiàn)了顯著的“剪刀差”現(xiàn) 象。所以,尋求效率更高的計算芯片就成為了業(yè)界的共識。DPU芯片就是在這 樣的趨勢下提出的。

帶寬性能增速比(RBP)失調(diào)

摩爾定律的放緩與全球數(shù)據(jù)量的爆發(fā)這個正在迅速激化的矛盾通常被作為 處理器專用化的大背景,正所謂硅的摩爾定律雖然已經(jīng)明顯放緩,但“數(shù)據(jù)摩 爾定律”已然到來。IDC的數(shù)據(jù)顯示,全球數(shù)據(jù)量在過去10年年均復(fù)合增長率 接近50%,并進一步預(yù)測每四個月對于算力的需求就會翻一倍。因此必須要找 到新的可以比通用處理器帶來更快算力增長的計算芯片,DPU于是應(yīng)運而生。這個大背景雖然有一定的合理性,但是還是過于模糊,并沒有回答DPU之所以 新的原因是什么,是什么“量變”導(dǎo)致了“質(zhì)變”?

從現(xiàn)在已經(jīng)公布的各個廠商的DPU架構(gòu)來看,雖然結(jié)構(gòu)有所差異,但都不 約而同強調(diào)網(wǎng)絡(luò)處理能力。從這個角度看,DPU是一個強IO型的芯片,這也是 DPU與CPU最大的區(qū)別。CPU的IO性能主要體現(xiàn)在高速前端總線(在Intel的體 系里稱之為FSB,F(xiàn)ront Side Bus),CPU通過FSB連接北橋芯片組,然后連接到 主存系統(tǒng)和其他高速外設(shè)(主要是PCIe設(shè)備)。目前更新的CPU雖然通過集成 存儲控制器等手段弱化了北橋芯片的作用,但本質(zhì)是不變的。CPU對于處理網(wǎng) 絡(luò)處理的能力體現(xiàn)在網(wǎng)卡接入鏈路層數(shù)據(jù)幀,然后通過操作系統(tǒng)(OS)內(nèi)核 態(tài),發(fā)起DMA中斷響應(yīng),調(diào)用相應(yīng)的協(xié)議解析程序,獲得網(wǎng)絡(luò)傳輸?shù)臄?shù)據(jù)(雖 然也有不通過內(nèi)核態(tài)中斷,直接在用戶態(tài)通過輪詢獲得網(wǎng)絡(luò)數(shù)據(jù)的技術(shù),如 Intel的DPDK,Xilinx的Onload等,但目的是降低中斷的開銷,降低內(nèi)核態(tài)到用 戶態(tài)的切換開銷,并沒有從根本上增強IO性能)。可見,CPU是通過非常間接 的手段來支持網(wǎng)絡(luò)IO,CPU的前端總線帶寬也主要是要匹配主存(特別是 DDR)的帶寬,而不是網(wǎng)絡(luò)IO的帶寬。

相較而言,DPU的IO帶寬幾乎可以與網(wǎng)絡(luò)帶寬等同,例如,網(wǎng)絡(luò)支持 25G,那么DPU就要支持25G。從這個意義上看,DPU繼承了網(wǎng)卡芯片的一些特 征,但是不同于網(wǎng)卡芯片,DPU不僅僅是為了解析鏈路層的數(shù)據(jù)幀,而是要做 直接的數(shù)據(jù)內(nèi)容的處理,進行復(fù)雜的計算。所以,DPU是在支持強IO基礎(chǔ)上的 具備強算力的芯片。簡言之,DPU是一個IO密集型的芯片;相較而言,DPU還 是一個計算密集型芯片。

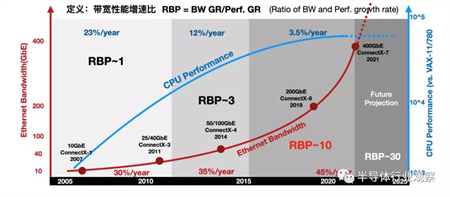

進一步地,通過比較網(wǎng)絡(luò)帶寬的增長趨勢和通用CPU性能增長趨勢,能發(fā) 現(xiàn)一個有趣的現(xiàn)象:帶寬性能增速比(RBP,Ratio of Bandwidth and Performance growth rate)失調(diào)。RBP定義為網(wǎng)絡(luò)帶寬的增速比上CPU性能增速, 即RBP=BW GR/Perf. GR如圖1-1所示,以Mellanox的ConnectX系列網(wǎng)卡帶寬作為 網(wǎng)絡(luò)IO的案例,以Intel的系列產(chǎn)品性能作為CPU的案例,定義一個新指標(biāo)“帶 寬性能增速比”來反應(yīng)趨勢的變化。

圖1-1 帶寬性能增速?(RBP)失調(diào)

2010年前,網(wǎng)絡(luò)的帶寬年化增長大約是30%,到2015年微增到35%,然后在 近年達到45%。相對應(yīng)的,CPU的性能增長從10年前的23%,下降到12%,并在 近年直接降低到3%。在這三個時間段內(nèi),RBP指標(biāo)從1附近,上升到3,并在近 年超過了10!如果在網(wǎng)絡(luò)帶寬增速與CPU性能增速近乎持平,RGR~1,IO壓力 尚未顯現(xiàn)出來,那么當(dāng)目前RBP達到10倍的情形下,CPU幾乎已經(jīng)無法直接應(yīng)對 網(wǎng)絡(luò)帶寬的增速。RBP指標(biāo)在近幾年劇增也許是DPU終于等到機會“橫空出 世”的重要原因之一。

異構(gòu)計算發(fā)展趨勢的助?

DPU首先作為計算卸載的引擎,直接效果是給CPU“減負”。DPU的部分 功能可以在早期的TOE(TCP/IP Offloading Engine)中看到。正如其名,TOE 就是將CPU的處理TCP協(xié)議的任務(wù)“卸載”到網(wǎng)卡上。傳統(tǒng)的TCP軟件處理方式 雖然層次清晰,但也逐漸成為網(wǎng)絡(luò)帶寬和延遲的瓶頸。軟件處理方式對CPU的 占用,也影響了CPU處理其他應(yīng)用的性能。TCP卸載引擎(TOE)技術(shù),通過 將TCP協(xié)議和IP協(xié)議的處理進程交由網(wǎng)絡(luò)接口控制器進行處理,在利用硬件加 速為網(wǎng)絡(luò)時延和帶寬帶來提升的同時,顯著降低了 CPU 處理協(xié)議的壓力。具體 有三個方面的優(yōu)化:1)隔離網(wǎng)絡(luò)中斷,2)降低內(nèi)存數(shù)據(jù)拷貝量,3)協(xié)議解析硬件化。這三個技術(shù)點逐漸發(fā)展成為現(xiàn)在數(shù)據(jù)平面計算的三個技術(shù),也是DPU 普遍需要支持的技術(shù)點。例如,NVMe協(xié)議,將中斷策略替換為輪詢策略,更 充分的開發(fā)高速存儲介質(zhì)的帶寬優(yōu)勢;DPDK采用用戶態(tài)調(diào)用,開發(fā)“Kernelbypassing”機制,實現(xiàn)零拷貝(Zeor-Copy);在DPU中的面向特定應(yīng)用的專用 核,例如各種復(fù)雜的校驗和計算、數(shù)據(jù)包格式解析、查找表、IP安全(IPSec) 的支持等,都可以視為協(xié)議處理的硬件化支持。所以,TOE基本可以被視為 DPU的雛形。

延續(xù)TOE的思想,將更多的計算任務(wù)卸載至網(wǎng)卡側(cè)來處理,促進了智能網(wǎng) 卡(SmartNIC)技術(shù)的發(fā)展。常見的智能網(wǎng)卡的基本結(jié)構(gòu)是以高速網(wǎng)卡為基本 功能,外加一顆高性能的FPGA芯片作為計算的擴展,來實現(xiàn)用戶自定義的計算 邏輯,達到計算加速的目的。然而,這種“網(wǎng)卡+FPGA”的模式并沒有將智能 網(wǎng)卡變成一個絕對主流的計算設(shè)備,很多智能網(wǎng)卡產(chǎn)品被當(dāng)作單純的FPGA加速 卡來使用,在利用FPGA優(yōu)勢的同時,也繼承了所有FPGA的局限性。DPU是對 現(xiàn)有的SmartNIC的一個整合,能看到很多以往SmartNIC的影子,但明顯高于之 前任何一個SmartNIC的定位。

Amazon的AWS在2013研發(fā)了Nitro產(chǎn)品,將數(shù)據(jù)中心開銷(為虛機提供遠程 資源,加密解密,故障跟蹤,安全策略等服務(wù)程序)全部放到專用加速器上執(zhí) 行。Nitro架構(gòu)采用輕量化Hypervisor配合定制化的硬件,將虛擬機的計算(主要 是CPU和內(nèi)存)和I/O(主要是網(wǎng)絡(luò)和存儲)子系統(tǒng)分離開來,通過PCIe總線連 接,節(jié)省了30%的CPU資源。阿里云提出的X-Dragon系統(tǒng)架構(gòu),核心是MOC 卡,有比較豐富的對外接口,也包括了計算資源、存儲資源和網(wǎng)絡(luò)資源。MOC 卡的核心X-Dragon SOC,統(tǒng)一支持網(wǎng)絡(luò),IO、存儲和外設(shè)的虛擬化,為虛擬 機、裸金屬、容器云提供統(tǒng)一的資源池。

可見,DPU其實在行業(yè)內(nèi)已經(jīng)孕育已久,從早期的網(wǎng)絡(luò)協(xié)議處理卸載,到 后續(xù)的網(wǎng)絡(luò)、存儲、虛擬化卸載,其帶來的作用還是非常顯著的,只不過在此 之前DPU“有實無名”,現(xiàn)在是時候邁上一個新的臺階了。

3.DPU發(fā)展歷程

隨著云平臺虛擬化技術(shù)的發(fā)展,智能網(wǎng)卡的發(fā)展基本可以分為三個階段 (如圖1-2所示):

圖1-2 智能?卡發(fā)展的三個階段

第?階段:基礎(chǔ)功能?卡

基礎(chǔ)功能網(wǎng)卡(即普通網(wǎng)卡)提供2x10G或2x25G帶寬吞吐,具有較少的硬 件卸載能力,主要是Checksum,LRO/LSO等,支持SR-IOV,以及有限的多隊列 能力。在云平臺虛擬化網(wǎng)絡(luò)中,基礎(chǔ)功能網(wǎng)卡向虛擬機(VM)提供網(wǎng)絡(luò)接入的 方式主要是有三種:由操作系統(tǒng)內(nèi)核驅(qū)動接管網(wǎng)卡并向虛擬機(VM)分發(fā)網(wǎng)絡(luò) 流量;由OVS-DPDK接管網(wǎng)卡并向虛擬機(VM)分發(fā)網(wǎng)絡(luò)流量;以及高性能場 景下通過SR-IOV的方式向虛擬機(VM)提供網(wǎng)絡(luò)接入能力。

第?階段:硬件卸載?卡

可以認為是第一代智能網(wǎng)卡,具有豐富的硬件卸載能力,比較典型的有 OVS Fastpath硬件卸載,基于RoCEv1和RoCEv2的RDMA網(wǎng)絡(luò)硬件卸載,融合網(wǎng) 絡(luò)中無損網(wǎng)絡(luò)能力(PFC,ECN,ETS等)的硬件卸載,存儲領(lǐng)域NVMe-oF的硬 件卸載,以及安全傳輸?shù)臄?shù)據(jù)面卸載等。這個時期的智能網(wǎng)卡以數(shù)據(jù)平面的卸 載為主。

第三階段:DPU智能?卡

可以認為是第二代智能網(wǎng)卡,在第一代智能網(wǎng)卡基礎(chǔ)上加入CPU,可以用 來卸載控制平面的任務(wù)和一些靈活復(fù)雜的數(shù)據(jù)平面任務(wù)。目前DPU智能網(wǎng)卡的 特點首先是支持PCIe Root Complex模式和Endpoint模式,在配置為PCIe Root Complex模式時,可以實現(xiàn)NVMe存儲控制器,與NVMe SSD磁盤一起構(gòu)建存儲 服務(wù)器;另外,由于大規(guī)模的數(shù)據(jù)中心網(wǎng)絡(luò)的需要,對無損網(wǎng)絡(luò)的要求更加嚴 格,需要解決數(shù)據(jù)中心網(wǎng)絡(luò)中Incast流量、“大象”流等帶來的網(wǎng)絡(luò)擁塞和時延 問題,各大公有云廠商紛紛提出自己的應(yīng)對方法,比如阿里云的高精度擁塞控 制(HPCC,High Precision Congestion Control),AWS的可擴展可靠數(shù)據(jù)報 (SRD,Scalable Reliable Datagram)等。DPU智能網(wǎng)卡在解決這類問題時將會引 入更為先進的方法,如Fungible的TrueFabric,就是在DPU智能網(wǎng)卡上的新式解 決方案。還有,業(yè)界提出了Hypervisor中的網(wǎng)絡(luò),存儲和安全全棧卸載的發(fā)展方向,以Intel為代表提出了IPU,將基礎(chǔ)設(shè)施的功能全部卸載到智能網(wǎng)卡中,可以 全面釋放之前用于Hypervisor管理的CPU算力。

未來的DPU智能?卡硬件形態(tài)

隨著越來越多的功能加入到智能網(wǎng)卡中,其功率將很難限制在75W之內(nèi), 這樣就需要獨立的供電系統(tǒng)。所以,未來的智能網(wǎng)卡形態(tài)可能有三種形態(tài):

(1)獨立供電的智能網(wǎng)卡,需要考慮網(wǎng)卡狀態(tài)與計算服務(wù)之間低層信號識 別,在計算系統(tǒng)啟動的過程中或者啟動之后,智能網(wǎng)卡是否已經(jīng)是進入服務(wù)狀 態(tài),這些都需要探索和解決。

(2)沒有PCIe接口的DPU智能網(wǎng)卡,可以組成DPU資源池,專門負責(zé)網(wǎng)絡(luò) 功能,例如負載均衡,訪問控制,防火墻設(shè)備等。管理軟件可以直接通過智能 網(wǎng)卡管理接口定義對應(yīng)的網(wǎng)絡(luò)功能,并作為虛擬化網(wǎng)絡(luò)功能集群提供對應(yīng)網(wǎng)絡(luò) 能力,無需PCIe接口。

(3)多PCIe接口,多網(wǎng)口的DPU芯片。例如Fungible F1芯片,支持16個雙 模PCIe控制器,可以配置為Root Complex模式或Endpoint模式,以及8x100G網(wǎng)絡(luò) 接口。通過PCIe Gen3 x8接口可以支撐8個Dual-Socket計算服務(wù)器,網(wǎng)絡(luò)側(cè)提供 8x100G帶寬的網(wǎng)口。

圖1-3 未來智能?卡的硬件形態(tài)

DPU作為一種新型的專用處理器,隨著需求側(cè)的變化,必將在未來計算系 統(tǒng)中成為一個重要組成部分,對于支撐下一代數(shù)據(jù)中心起到至關(guān)重要的作用。

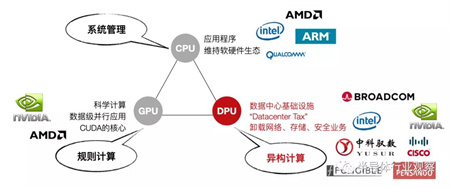

4.DPU與CPU、GPU的關(guān)系

CPU是整個IT生態(tài)的定義者,無論是服務(wù)器端的x86還是移動端的ARM,都 各自是構(gòu)建了穩(wěn)固的生態(tài)系統(tǒng),不僅形成技術(shù)生態(tài)圈,還形成了閉合價值鏈。

GPU是執(zhí)行規(guī)則計算的主力芯片,如圖形渲染。經(jīng)過NVIDIA對通用GPU (GPGPU)和CUDA編程框架的推廣,GPU在數(shù)據(jù)并行的任務(wù)如圖形圖像、深 度學(xué)習(xí)、矩陣運算等方面成為了主力算力引擎,并且成為了高性能計算最重要 的輔助計算單元。2021年6月公布的Top500高性能計算機(超級計算機)的前10 名中,有六臺(第2、3、5、6、8、9名)都部署有NVIDIA的GPU。

圖1-4 未來算??態(tài)(相關(guān)?商為不完全列舉,僅做為?意參考)

數(shù)據(jù)中心與超極計算機不同,后者主要面向科學(xué)計算,如大飛機研制,石 油勘探、新藥物研發(fā)、氣象預(yù)報、電磁環(huán)境計算等應(yīng)用,性能是主要指標(biāo),對 接入帶寬要求不高;但數(shù)據(jù)中心面向云計算商業(yè)化應(yīng)用,對接入帶寬,可靠 性、災(zāi)備、彈性擴展等要求更高,與之相適應(yīng)發(fā)展起來的虛擬機、容器云、并行編程框、內(nèi)容分發(fā)網(wǎng)等等技術(shù),都是為了更好的支撐上層商業(yè)應(yīng)用如電商、 支付、視頻流、網(wǎng)盤、辦公OA等。但是這些IaaS和PaaS層的服務(wù)開銷極大, Amazon曾公布AWS的系統(tǒng)開銷在30%以上。如果需要實現(xiàn)更好的QoS,在網(wǎng) 絡(luò)、存儲、安全等基礎(chǔ)設(shè)施服務(wù)上的開銷還會更高。

這些基礎(chǔ)層應(yīng)用類型與CPU架構(gòu)匹配程度不高導(dǎo)致計算效率低下。現(xiàn)有的 CPU的架構(gòu)有兩個大類:多核架構(gòu)(數(shù)個或數(shù)十幾個核)和眾核架構(gòu)(數(shù)百個 核以上),每種架構(gòu)支持唯一的規(guī)范通用指令集之一,如x86、ARM等。以指令 集為界,軟件和硬件被劃分開來分別獨立發(fā)展,迅速的催生了軟件產(chǎn)業(yè)和微處 理器產(chǎn)業(yè)的協(xié)同發(fā)展。但是,隨著軟 件復(fù)雜度的上升,軟件的生產(chǎn) 率 (Productivity)得到更多的重視,軟件工程學(xué)科也更加關(guān)注如何高效地構(gòu)建大 型軟件系統(tǒng),而非如何用更少的硬件資源獲得盡可能高的執(zhí)行性能。業(yè)界有個 被戲稱的“安迪比爾定律”,其內(nèi)容是“What Andy gives, Bill takes away”,安 迪(Andy)指英特爾前CEO安迪·格魯夫,比爾(Bill)指微軟前任CEO比爾· 蓋茨,意為硬件提高的性能,很快被軟件消耗掉了。

正如CPU在處理圖像處理時不夠高效一樣,現(xiàn)在有大量的基礎(chǔ)層應(yīng)用CPU 處理起來也比較低效,例如網(wǎng)絡(luò)協(xié)議處理,交換路由計算,加密解密,數(shù)據(jù)壓 縮等這類計算密集的任務(wù),還有支持分布式處理的數(shù)據(jù)一致性協(xié)議如RAFT等。這些數(shù)據(jù)或者通過從網(wǎng)絡(luò)IO接入系統(tǒng),或者通過板級高速PCIe總線接入系統(tǒng), 再通過共享主存經(jīng)由DMA機制將數(shù)據(jù)提供給CPU或GPU來處理。既要處理大量 的上層應(yīng)用,又要維持底層軟件的基礎(chǔ)設(shè)施,還要處理各種特殊的IO類協(xié)議, 復(fù)雜的計算任務(wù)讓CPU不堪重負。

這些基礎(chǔ)層負載給“異構(gòu)計算”提供了一個廣闊的發(fā)展空間。將這些基礎(chǔ) 層負載從CPU上卸載下來,短期內(nèi)可以“提質(zhì)增效”,長遠來看還為新的業(yè)務(wù) 增長提供技術(shù)保障。DPU將有望成為承接這些負載的代表性芯片,與CPU和 GPU優(yōu)勢互補,建立起一個更加高效的算力平臺。可以預(yù)測,用于數(shù)據(jù)中心的DPU的量將達到和數(shù)據(jù)中心服務(wù)器等量的級別,每年千萬級新增,算上存量的 替代,估算五年總體的需求量將突破兩億顆,超過獨立GPU卡的需求量。每臺 服務(wù)器可能沒有GPU,但必須有DPU,好比每臺服務(wù)器都必須配網(wǎng)卡一樣。

5.DPU的產(chǎn)業(yè)化機遇

數(shù)據(jù)中心作為IT基礎(chǔ)設(shè)施最重要的組成部分在過去10年成為了各大高端芯 片廠商關(guān)注的焦點。各大廠商都將原有的產(chǎn)品和技術(shù),用全新的DPU的理念重 新封裝后,推向了市場。

NVIDIA收購Mellanox后,憑借原有的ConnectX系列高速網(wǎng)卡技術(shù),推出其 BlueField系列DPU,成為DPU賽道的標(biāo)桿。作為算法加速芯片頭部廠商的Xilinx 在2018年還將“數(shù)據(jù)中心優(yōu)先(Datacenter First)”作為其全新發(fā)展戰(zhàn)略。發(fā)布 了Alveo系列加速卡產(chǎn)品,旨在大幅提升云端和本地數(shù)據(jù)中心服務(wù)器性能。2019 年4月,Xilinx宣布收購Solarflare通信公司,將領(lǐng)先的FPGA、MPSoC和ACAP解 決方案與 Solarflare 的超低時延網(wǎng)絡(luò)接口卡( NIC )技術(shù)以及應(yīng)用加速軟件相結(jié) 合,從而實現(xiàn)全新的融合SmartNIC解決方案。Intel 2015年底收購了Xilinx的競爭 對手——Altera,在通用處理器的基礎(chǔ)上,進一步完善硬件加速能力。Intel 2021 年6月新發(fā)布的IPU產(chǎn)品(可以被視為Intel版本的DPU),將FPGA與Xeon D系列 處理器集成,成為了DPU賽道有力的競爭者。IPU是具有強化的加速器和以太網(wǎng) 連接的高級網(wǎng)絡(luò)設(shè)備,它使用緊密耦合、專用的可編程內(nèi)核加速和管理基礎(chǔ)架 構(gòu)功能。IPU提供全面的基礎(chǔ)架構(gòu)分載,并可作為運行基礎(chǔ)架構(gòu)應(yīng)用的主機的控 制點,從而提供一層額外防護。幾乎同一時間,Marvall發(fā)布了OCTEON 10 DPU產(chǎn)品,不僅具備強大的轉(zhuǎn)發(fā)能力,還具有突出的AI處理能力。

在同 一時期, 一些傳統(tǒng)并不涉足芯片設(shè)計的互聯(lián)網(wǎng)廠商,如海外的 Google、Amazon,國內(nèi)的阿里巴巴等巨頭紛紛啟動了自研芯片的計劃,而且研 發(fā)重點都是面向數(shù)據(jù)處理器的高性能專用處理器芯片,希望以此改善云端的服務(wù)器的成本結(jié)構(gòu),提高單位能耗的性能水平。數(shù)據(jù)研究預(yù)測DPU在云計算市場 的應(yīng)用需求最大,且市場規(guī)模隨著云計算數(shù)據(jù)中心的迭代而增長,到2025年單 中國的市場容量都將達到40億美元的規(guī)模。