問(wèn)題:

如何為ADC增加隔離而不損害其性能?

答案:

對(duì)于隔離式高性能ADC,一方面要注意隔離時(shí)鐘,另一方面要注意隔離電源。

SAR ADC傳統(tǒng)上被用于較低采樣速率和較低分辨率的應(yīng)用。如今已有1 MSPS采樣速率的快速、高精度、20位SAR ADC,例如LTC2378-20 ,以及具有32位分辨率的過(guò)采樣SAR ADC,例如LTC2500-32。將ADC用于高性能設(shè)計(jì)時(shí),整個(gè)信號(hào)鏈都需要非常低的噪聲。當(dāng)信號(hào)鏈需要額外的隔離時(shí),性能會(huì)受到影響。

關(guān)于隔離,有三方面需要考慮:

·確保熱端有電的隔離電源

·確保數(shù)據(jù)路徑得到隔離的隔離數(shù)據(jù)

·ADC(采樣時(shí)鐘或轉(zhuǎn)換信號(hào))的時(shí)鐘隔離,以防熱端不產(chǎn)生時(shí)鐘

隔離電源(反激拓?fù)渑c推挽拓?fù)涞谋容^)

對(duì)于傳感器應(yīng)用,隔離電源通常在10 W以下范圍內(nèi)。

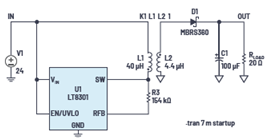

反激式轉(zhuǎn)換器被廣泛用于隔離電源。圖1顯示了反激式轉(zhuǎn)換器簡(jiǎn)單可行的特點(diǎn)。該拓?fù)涞膬?yōu)勢(shì)是只需要很少的外部元件。反激式轉(zhuǎn)換器只有一個(gè)集成開(kāi)關(guān)。該開(kāi)關(guān)可能是影響信號(hào)鏈性能的主噪聲源。對(duì)于高性能模擬設(shè)計(jì),反激式轉(zhuǎn)換器會(huì)帶來(lái)很多斷點(diǎn),引起電磁輻射(稱為EMI),這可能會(huì)限制電路的性能。

圖1.典型的反激式轉(zhuǎn)換器拓?fù)?/p>

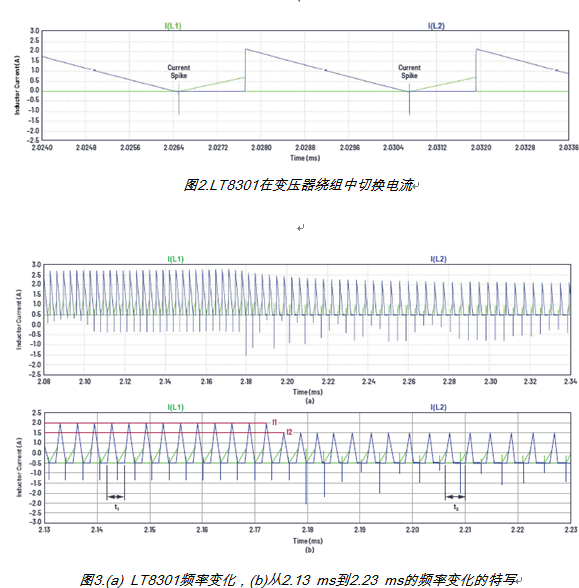

圖2顯示了變壓器L1和L2中的電流。在初級(jí)(L1)和次級(jí)(L2)繞組中,電流在短時(shí)間內(nèi)從高值跳變?yōu)榱恪k娏骷夥蹇梢栽趫D3的I(L1)/I(L2)跡線中看到。電流和能量在初級(jí)電感中累積,當(dāng)開(kāi)關(guān)斷開(kāi)時(shí),它們被傳輸?shù)酱渭?jí)電感,產(chǎn)生瞬變。需要降低開(kāi)關(guān)噪聲效應(yīng)導(dǎo)致的瞬變,因此,設(shè)計(jì)中必須插入緩沖器和濾波器。除了額外的濾波器之外,反激拓?fù)涞牧硪粋€(gè)缺點(diǎn)是磁性材料的利用率低,而所需的電感較高,因此變壓器較大。此外,反激式轉(zhuǎn)換器的熱環(huán)路也很大,不易管理。有關(guān)熱環(huán)路的背景信息,請(qǐng)參閱應(yīng)用筆記AN139。

反激式轉(zhuǎn)換器的另一個(gè)挑戰(zhàn)涉及開(kāi)關(guān)頻率變化。圖3顯示了負(fù)載變化引起的頻率變化。如圖3a所示,t1 < t2。這意味著fSWITCH隨著負(fù)載電流從較高負(fù)載電流I1減小到較低負(fù)載電流I2而變化。頻率的變化會(huì)在不可預(yù)測(cè)的時(shí)間產(chǎn)生內(nèi)部噪聲。此外,頻率也會(huì)因器件不同而異,這使得更難以對(duì)其進(jìn)行濾波,因?yàn)槊總€(gè)PCB都需要調(diào)整濾波。對(duì)于一款5 V輸入范圍的20位SAR ADC,1 LSB相當(dāng)于大約5μV。EMI噪聲引入的誤差應(yīng)低于5μV,這意味著為精密系統(tǒng)隔離電源時(shí),不應(yīng)選擇反激拓?fù)洹?/p>

還有其他電磁輻射騷擾較低的隔離電源架構(gòu)。就輻射而言,推挽式轉(zhuǎn)換器比反激式轉(zhuǎn)換器更合適。像LT3999這樣的推挽式穩(wěn)壓器提供了與ADC時(shí)鐘同步的可能性,有助于實(shí)現(xiàn)高性能。圖4顯示了隔離電源電路中的LT3999與ADC采樣時(shí)鐘同步的情況。請(qǐng)記住,初級(jí)到次級(jí)電容為開(kāi)關(guān)噪聲提供了一個(gè)避免共模噪聲效應(yīng)的返回路徑。該電容可以在PCB設(shè)計(jì)中利用重疊的頂層平面和第二層平面實(shí)現(xiàn),以及/或者利用實(shí)際電容實(shí)現(xiàn)。

圖5顯示了變壓器處的電流波形(初級(jí)側(cè)和次級(jí)側(cè)電流),它更好地利用了變壓器,提供更好的EMI行為。

圖6顯示了與外部時(shí)鐘信號(hào)的同步。采集階段的末端與同步引腳的正邊沿對(duì)齊。因此,將有一個(gè)大約4μs的較長(zhǎng)安靜時(shí)間。這使得轉(zhuǎn)換器可以在該時(shí)間范圍內(nèi)對(duì)輸入信號(hào)進(jìn)行采樣,并將隔離電源的瞬變效應(yīng)降至最小。LTC2378-20的采集時(shí)間為312 ns,非常適合<1μs的安靜窗口。

數(shù)據(jù)隔離

數(shù)據(jù)隔離可以使用數(shù)字隔離器實(shí)現(xiàn),例如ADuMx系列數(shù)字隔離器。這些數(shù)字隔離器可用于SPI、I2C、CAN等許多標(biāo)準(zhǔn)接口,例如ADuM140 可用于SPI隔離。 為了實(shí)現(xiàn)數(shù)據(jù)隔離,只需將SPI信號(hào)SPI時(shí)鐘、SDO、SCK和Busy連接到數(shù)據(jù)隔離器。在數(shù)據(jù)隔離中,電能通過(guò)感性隔離柵從初級(jí)側(cè)傳輸?shù)酱渭?jí)側(cè)。需要添加電流返回路徑,這由電容來(lái)完成。該電容可以在PCB中利用重疊平面實(shí)現(xiàn)。

時(shí)鐘隔離

時(shí)鐘隔離是另一項(xiàng)重要任務(wù)。如果使用1 MHz采樣速率的20位高性能ADC,例如LTC2378-20,可以實(shí)現(xiàn)104 dB的信噪比(SNR)。為了實(shí)現(xiàn)高性能,需要無(wú)抖動(dòng)時(shí)鐘。為什么不應(yīng)使用像ADuM14x系列這樣的標(biāo)準(zhǔn)隔離器?標(biāo)準(zhǔn)隔離器會(huì)增加時(shí)鐘抖動(dòng),從而限制ADC的性能。更多詳細(xì)信息請(qǐng)參見(jiàn)設(shè)計(jì)筆記DN1013。

圖7顯示了不同頻率、不同類型時(shí)鐘抖動(dòng)下SNR的理論極限。像LTC2378這樣的高性能ADC的孔徑時(shí)鐘抖動(dòng)為4 ps,在200 kHz輸入下理論限值為106 dB。

圖8顯示的標(biāo)準(zhǔn)時(shí)鐘隔離器概念包括:

像ADuM250N這樣良好的標(biāo)準(zhǔn)數(shù)字隔離器的抖動(dòng)為70 ps rms。對(duì)于100 dB SNR目標(biāo),由于時(shí)鐘抖動(dòng),信號(hào)采樣速率限制為20 kHz。

像LTM2893這樣優(yōu)化的時(shí)鐘隔離器提供30 ps rms的低抖動(dòng)。對(duì)于100 dB SNR目標(biāo),現(xiàn)在的信號(hào)采樣速率為50 kHz,在全部SNR性能下可提供更多帶寬。

圖9:對(duì)于更高的輸入頻率,應(yīng)使用LVDS隔離器。ADN4654提供2.6 ps抖動(dòng),接近ADC的最佳性能。在100 kHz輸入時(shí),時(shí)鐘抖動(dòng)導(dǎo)致的SNR限值將是110 dB。

圖10:使用PLL凈化時(shí)鐘。 ADF4360-9可以幫助減少時(shí)鐘抖動(dòng)。

圖11顯示了使用PLL凈化時(shí)鐘的更詳細(xì)框圖。您可以將ADF4360-9用作時(shí)鐘凈化器,并在輸出端增加一個(gè)2分頻器。AD7760額定支持1.1 MHz。

因此,不能直接支持LTC2378等1 MSPS SAR ADC。在這種情況下,低抖動(dòng)觸發(fā)器會(huì)有幫助。它將時(shí)鐘2分頻。

圖13:本地產(chǎn)生時(shí)鐘是獲得具有所需抖動(dòng)性能的時(shí)鐘的另一個(gè)方案。本地時(shí)鐘生成會(huì)使時(shí)鐘架構(gòu)更加復(fù)雜,因?yàn)樗鼘惒綍r(shí)鐘域引入系統(tǒng)。例如,若要使用兩個(gè)單獨(dú)的隔離ADC,則時(shí)鐘的絕對(duì)頻率將會(huì)不同,必須增加采樣速率轉(zhuǎn)換以重新匹配時(shí)鐘。有關(guān)采樣速率轉(zhuǎn)換的一些細(xì)節(jié),請(qǐng)參閱工程師對(duì)話筆記EE-268。

高性能Sigma-Delta ADC的時(shí)鐘

時(shí)鐘的類似問(wèn)題也適用于高性能Sigma-Delta ADC,如AD7760。這里,重要的時(shí)鐘信號(hào)是無(wú)抖動(dòng)過(guò)采樣時(shí)鐘,例如40 MHz。這種情況下不需要額外的分頻器。

結(jié)論

隔離式高性能ADC需要仔細(xì)設(shè)計(jì)隔離方案并選擇隔離技術(shù),以實(shí)現(xiàn)高于100 dB的高性能SNR。應(yīng)特別重視隔離時(shí)鐘,因?yàn)闀r(shí)鐘抖動(dòng)的影響可能會(huì)破壞性能。其次應(yīng)注意隔離電源。簡(jiǎn)單的隔離拓?fù)洌ㄈ绶醇ぃ?huì)引入高EMI瞬變。

為了獲得更好的性能,應(yīng)使用推挽式轉(zhuǎn)換器。還需要關(guān)注數(shù)據(jù)隔離(盡管不太重要),可用標(biāo)準(zhǔn)器件能提供良好性能,對(duì)整體系統(tǒng)性能的影響較小。介紹這三個(gè)隔離主題有助于設(shè)計(jì)人員提出高性能隔離系統(tǒng)解決方案。

作者簡(jiǎn)介

Wilfried Platzer曾在德國(guó)卡爾斯魯厄?qū)W習(xí)信息技術(shù),側(cè)重于射頻技術(shù)。他1997年開(kāi)始在ITT工作,后來(lái)在TDK-Micronas工作。Wilfried擔(dān)任過(guò)多種職位,從現(xiàn)場(chǎng)應(yīng)用工程師開(kāi)始,然后專注于混合信號(hào)IC的概念和系統(tǒng)架構(gòu)工程設(shè)計(jì)。11年后,他跳到Auma從事電子預(yù)開(kāi)發(fā)工作。2015年,他加入凌力爾特公司(現(xiàn)為ADI公司的一部分)。目前,Wilfried是ADI公司的高級(jí)現(xiàn)場(chǎng)應(yīng)用工程師,負(fù)責(zé)為瑞士提供區(qū)域支持。