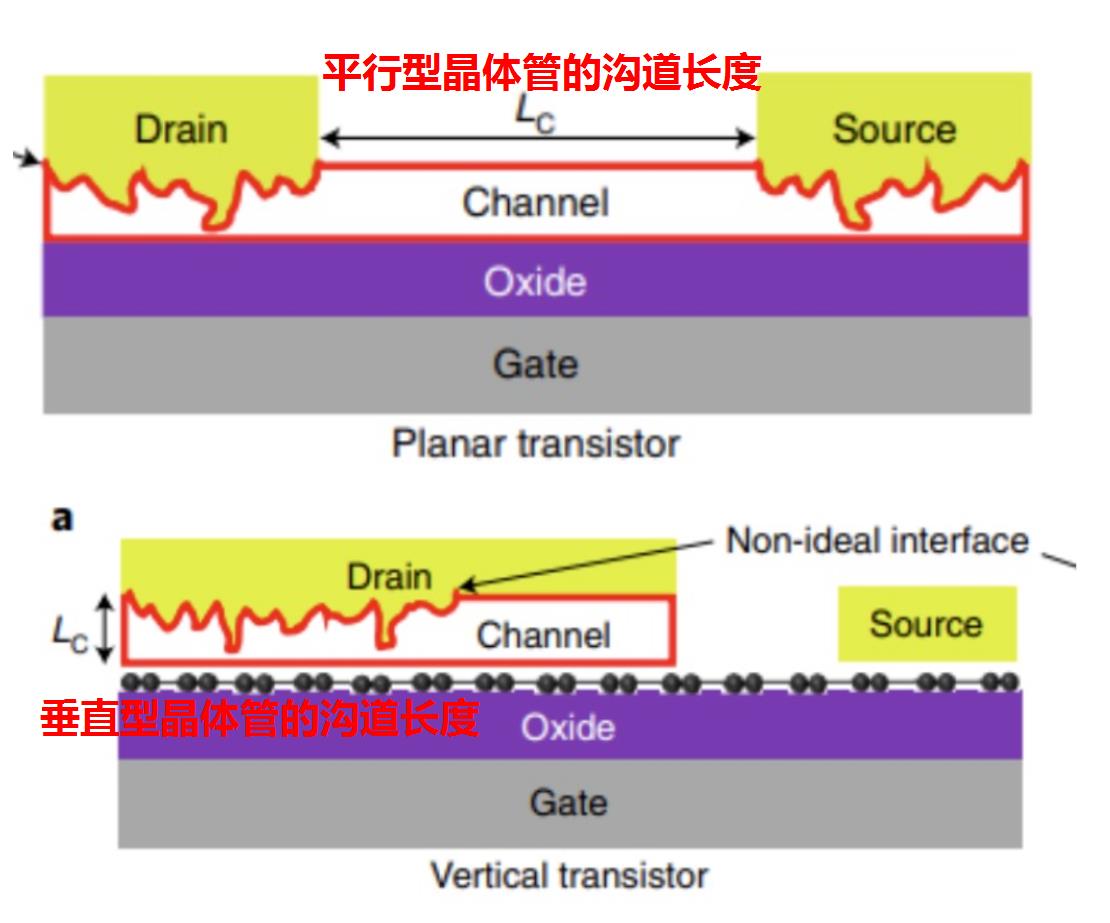

芯片是由晶體管組成的,同樣的面積之下,,晶體管越密集,,意味著芯片工藝越先進(jìn),所以每一代的芯片工藝提升,,都是以縮短晶體管導(dǎo)電溝道的長(zhǎng)度為目標(biāo)的,。

這個(gè)晶體管導(dǎo)電溝道的長(zhǎng)度,簡(jiǎn)稱(chēng)溝道長(zhǎng)度,,也就是指芯片的工藝,比如溝道長(zhǎng)度為5nm,,代表著芯片是5nm芯片,。

而為了縮短這個(gè)溝道長(zhǎng)度,,就需要高精度的光刻機(jī),光刻機(jī)精度越高,,越能夠讓溝道長(zhǎng)度變短,。

但不可否認(rèn)的是,由于目前的晶體管基本上都是平行型結(jié)構(gòu)(晶體管之間是平行擺放的),,當(dāng)芯片達(dá)到3nm工藝時(shí),,要縮短溝道長(zhǎng)度越來(lái)越難,因?yàn)闀?huì)帶來(lái)嚴(yán)重的短溝道效應(yīng),,同時(shí)對(duì)光刻機(jī)的精度也是要求太高了,。

所以后來(lái),科學(xué)家們研究另外一種晶體管結(jié)構(gòu),,就是垂直型結(jié)構(gòu)(晶體管之間是垂直擺放的),,垂直型晶體管的溝道長(zhǎng)度,僅由材料厚度決定,,這樣可在大幅度的縮短溝道長(zhǎng)度,,從而使晶體管更密集,實(shí)現(xiàn)更先進(jìn)的工藝,,并且不用依賴(lài)于傳統(tǒng)的高精度光刻技術(shù),。

但這種垂直型晶體管,理論很美好,,現(xiàn)實(shí)卻很?chē)?yán)峻,,因?yàn)榻饘伲雽?dǎo)體間之間會(huì)形成非常不理想的接觸界面,從而破壞整個(gè)器件的溝道,,增加垂直隧穿電流,,使器件不受柵極調(diào)控。

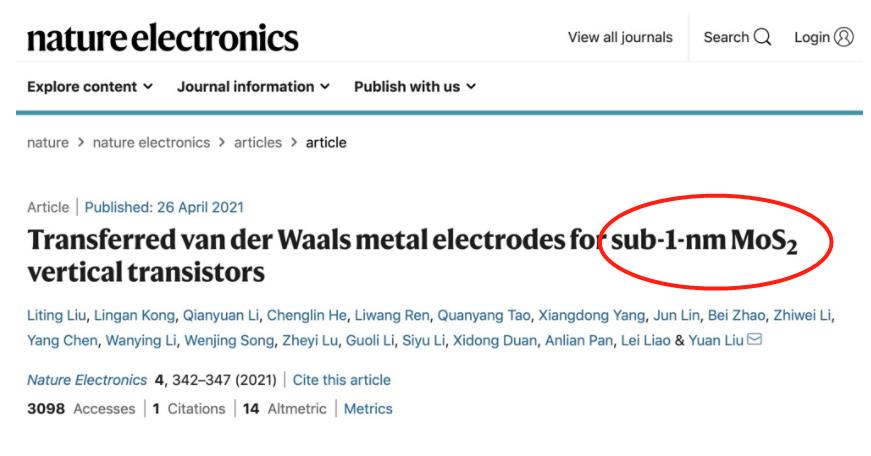

但在近日,,湖南大學(xué)的研究團(tuán)隊(duì),,采用低能量的范德華電極集成方式,實(shí)現(xiàn)了以二硫化鉬作為半導(dǎo)體溝道的薄層甚至單原子層的短溝道垂直器件,,減小了隧穿電流,,使得這種垂直晶體管技術(shù),進(jìn)入到了一個(gè)新的階段,。

在測(cè)試中,,垂直型晶體管在實(shí)現(xiàn)0.65nm的溝道長(zhǎng)度的同時(shí),同樣保持著較好的特性,,也就意味著芯片工藝,,能夠進(jìn)入到1nm級(jí)別。

更重要的是,,由于與平行型晶體管不同,,這種垂直型晶體管技術(shù),,能夠不依賴(lài)高精度光刻技術(shù)和刻蝕技術(shù)的限制,就可以生產(chǎn)出高制程的芯片來(lái),。

目前相關(guān)論文已發(fā)表在《自然·電子學(xué)》(Nature Electronics)雜志上,,湖南大學(xué)的官網(wǎng)上也有相關(guān)的詳細(xì)報(bào)道。

不過(guò),,大家也先別太激動(dòng),,目前這還只是研究,真正用到工廠生產(chǎn),,可能還需要很長(zhǎng)一段時(shí)間,,但也別吐槽,任何技術(shù)的量產(chǎn),,都是先有理論研究的,,沒(méi)有理論研究,哪來(lái)的量產(chǎn),。