從增強(qiáng)現(xiàn)實(shí)到人工智能、云計(jì)算再到物聯(lián)網(wǎng),5G正在燃爆新技術(shù)增長(zhǎng),同時(shí)也在燃爆它們生成的數(shù)據(jù)量。數(shù)據(jù)量越來(lái)越大,隨之而來(lái)的是存儲(chǔ)和快速訪問(wèn)需求,DDR5之類的技術(shù)變得空前重要。數(shù)據(jù)中心需要持續(xù)存儲(chǔ)、傳送和處理這些數(shù)據(jù),推動(dòng)著高速信令的極限,也給內(nèi)存帶來(lái)了前所未有的測(cè)試挑戰(zhàn)。

具體有哪些變化?DDR5與DDR4差別很大,實(shí)際上更像LPDDR4,DDR5帶來(lái)9個(gè)變化。

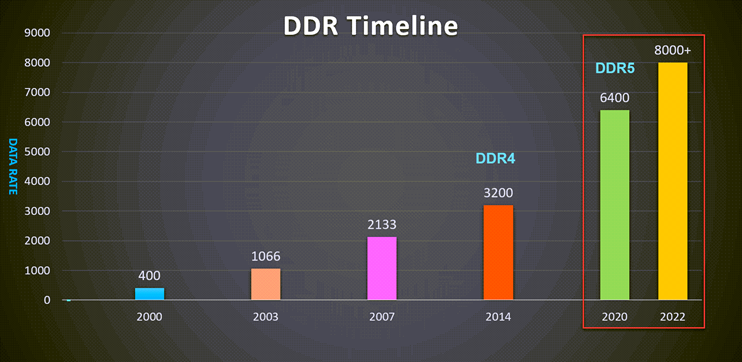

1. 速度更快!第一個(gè),也是最重要的一個(gè),數(shù)據(jù)速率達(dá)到6.4 Gbps,而DDR4最高只有3.2Gbps。規(guī)范中還有一條,在未來(lái)幾年內(nèi)把速度上限推高到8 Gbps以上。通道結(jié)構(gòu)與LPDDR4類似,ECC中也有兩條獨(dú)立的40位通道。還有更高的預(yù)讀取、更高的突發(fā)長(zhǎng)度和更高的行列組,這些都提高了效率,實(shí)現(xiàn)了高速模式。

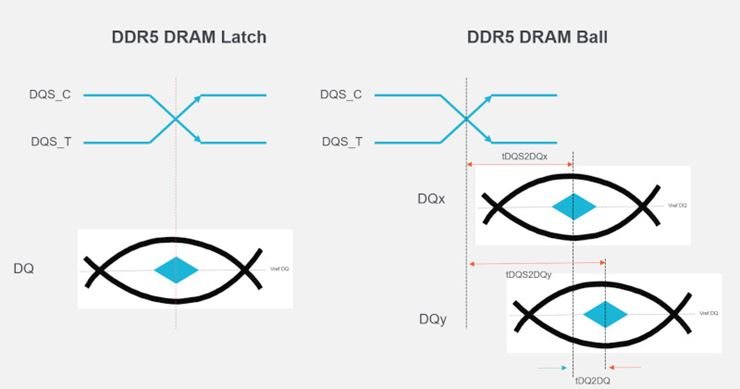

2. DDR5帶來(lái)的另一大變化是寫入不再居中。DQS和DQ之間有固定的偏置,因此我們不能只在示波器上測(cè)量DQS和DQ之間的延遲,以推算出是讀還是寫。不再這么容易了!讀寫突發(fā)分隔都將變得更加復(fù)雜。

3. 新的時(shí)鐘抖動(dòng)測(cè)量。DDR5引入了Rj、Dj和Tj測(cè)量,代替了周期和周期間抖動(dòng)測(cè)量。Rj指標(biāo)在最大數(shù)據(jù)速率下變得非常緊。優(yōu)秀的信號(hào)完整性對(duì)滿懷信心地測(cè)量這些參數(shù)變得至關(guān)重要。

4. 反嵌在更高的DDR5數(shù)據(jù)速率下將變得非常關(guān)鍵。反嵌是一種移除探頭和內(nèi)插器負(fù)載的技術(shù)。它還用來(lái)把探測(cè)點(diǎn)以虛擬方式從DRAM球移到DRAM芯片,以使反射達(dá)到最小。我們想看到Rx看到的是什么。為成功地創(chuàng)建反嵌濾波器文件或傳遞函數(shù),要求s-par文件,而且數(shù)量很多。想法是在SOC封裝、電路板模型、DRAM封裝、內(nèi)插器、探頭及IO設(shè)置中使用s-par模型,比如Tx驅(qū)動(dòng)強(qiáng)度和Rx ODT (如有),盡可能如實(shí)模擬DDR通道。如果沒(méi)有s-par模型,還可以使用簡(jiǎn)單的傳輸線參數(shù),如傳播延遲和特性阻抗,這通過(guò)在示波器屏幕上測(cè)量反射來(lái)實(shí)現(xiàn)。

5. 我們將第一次在接收機(jī)中有Rx均衡、4階DFE。DDR5提高了數(shù)據(jù)速率,而不用把DQ總線遷移到差分信令,也就是說(shuō),DQ總線仍是單端的,與DDR3/4相同。然而,內(nèi)存通道有大量的阻抗失配點(diǎn),由于反射而提高了整體ISI。在數(shù)據(jù)速率超過(guò)4800 Mbps時(shí),DRAM球的數(shù)據(jù)眼圖預(yù)計(jì)會(huì)閉合。DDR5 DRAM Rx實(shí)現(xiàn)了4階DFE,幫助均衡DQ信號(hào),在接收機(jī)鎖存數(shù)據(jù)后張開數(shù)據(jù)眼圖。此外,RCD的CA Rx還需要DFE,以確保可靠地捕獲信號(hào)。

6. DDR5另一個(gè)明顯變化是包括一條環(huán)回通道。看一下DDR5的引腳圖,您會(huì)發(fā)現(xiàn)專用的DQS/DQ環(huán)回引腳。其用來(lái)實(shí)現(xiàn)獨(dú)立DRAM RX/TX表征。環(huán)回通道至關(guān)重要。事實(shí)上,我們正是通過(guò)環(huán)回通道,才知道接收機(jī)真正實(shí)時(shí)做了哪些位決策。它是所有不同接收機(jī)之間共享的一條單線,由于信號(hào)完整性差及其他原因,我們只能發(fā)回每第四個(gè)位或每第二個(gè)位,所以有充足的時(shí)間,能夠確保外部接收機(jī)或誤碼檢測(cè)器能夠以100%準(zhǔn)確度校驗(yàn)片上Rx的質(zhì)量。

7. DDR5需要使用BERT和/或通用碼型發(fā)生器進(jìn)行獨(dú)立DRAM Rx/Tx測(cè)試。這要求一套全新測(cè)試,包括電壓和頻率靈敏度及壓力眼圖測(cè)試,DDR3/4中是沒(méi)有這些測(cè)試的。概念很簡(jiǎn)單,任何人都應(yīng)能夠使用標(biāo)準(zhǔn)化JEDEC夾具,根據(jù)JEDEC規(guī)定的測(cè)試程序,執(zhí)行標(biāo)準(zhǔn)測(cè)試,確定DRAM Rx/TX的健康狀況。

8. 準(zhǔn)確的壓力校準(zhǔn)將成為DDR5 RX測(cè)試中的大問(wèn)題,而且要獲得準(zhǔn)確的S參數(shù)模型,這兩者都必須進(jìn)行估算并測(cè)量,包括所有段。另一個(gè)關(guān)鍵特性是能夠準(zhǔn)確地或很好地猜出測(cè)量深度及示波器記錄長(zhǎng)度,這樣就不會(huì)浪費(fèi)太多的時(shí)間。

9. DRAM Rx/Tx測(cè)試將面臨巨大的數(shù)據(jù)庫(kù)管理問(wèn)題。數(shù)量龐大的s-par文件、反嵌模型和測(cè)量結(jié)果的自動(dòng)化和管理,將變成一個(gè)噩夢(mèng)。想象一下,不同廠商多種DIMM配置,以不同速度等級(jí)測(cè)試80多個(gè)引腳,這將非常非常困難。

與DDR3/4相比,DDR5改善了帶寬、密度和通道效率。但數(shù)據(jù)傳送速率越高,信號(hào)速度越快,要求一致性測(cè)試、調(diào)試和驗(yàn)證的測(cè)量性能越高。泰克科技去年7月推出TekExpress DDR5發(fā)射機(jī)解決方案,其改善了自動(dòng)化程度,工程師可以克服各種DFE所帶來(lái)的分析挑戰(zhàn),采用用戶自定義采集和DDR5去嵌技術(shù)及串行數(shù)據(jù)鏈路分析(SDLA)技術(shù),滿懷信心地、高效地驗(yàn)證和調(diào)試DDR5設(shè)計(jì)。了解DDR5固有的差異有助于高效檢驗(yàn)和調(diào)試。