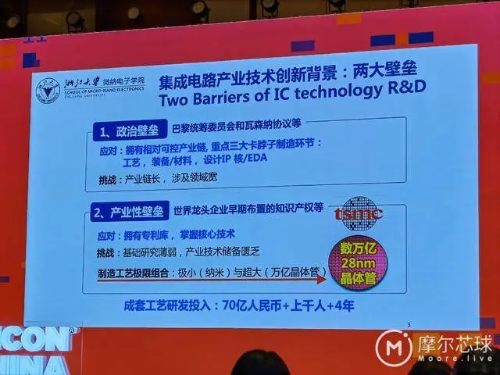

早前,SEMICON China在上海隆重舉行,在同期高峰論壇上,中國工程院院士、浙江大學(xué)微納電子學(xué)院院長吳漢明發(fā)表了題為《關(guān)于我國芯片制造的一些思考》的演講。他首先指出,集成電路產(chǎn)業(yè)正在面臨兩大壁壘,分別是政策壁壘和產(chǎn)業(yè)性壁壘,其中政治壁壘包括大家都知道的巴統(tǒng)和瓦森納協(xié)議,而產(chǎn)業(yè)性壁壘則體現(xiàn)在世界的半導(dǎo)體龍頭得益于早期布局,所積累的豐富知識(shí)產(chǎn)權(quán),這些都給中國半導(dǎo)體提出了巨大的挑戰(zhàn)。他舉例說道,一個(gè)成套工藝研發(fā),要投入70億人民幣,要上千人工作四年,才能完成,由此可以看到集成電路行業(yè)的難。

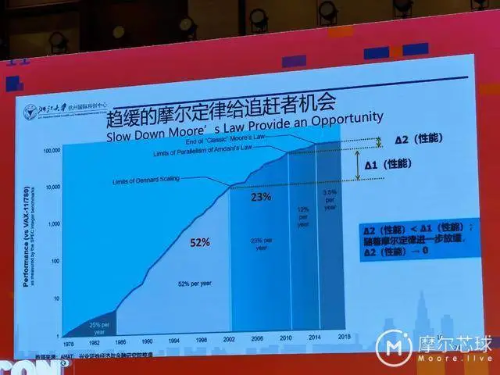

吳漢明院士進(jìn)一步指出,進(jìn)入這些年,集成電路產(chǎn)業(yè)發(fā)生了一些新的變化,他以20nm為例講述了當(dāng)中的轉(zhuǎn)變。從他提供的數(shù)據(jù)我們可以看到,從28nm推進(jìn)到20nm,單個(gè)晶體管的成本提高了。這就讓我們進(jìn)入了所謂的后摩爾時(shí)代,為此芯片行業(yè)需要去尋找新的技術(shù)去支撐芯片繼續(xù)前進(jìn)。

他強(qiáng)調(diào),如下圖所示,在后摩爾時(shí)代,在高性能計(jì)算、移動(dòng)計(jì)算和自主感知等應(yīng)用的推動(dòng)下,我們應(yīng)該增加對(duì)邏輯技術(shù)、基本規(guī)則縮放、性能助推器、PPA縮放、3D集成、內(nèi)存技術(shù)、DRAM技術(shù)、Flash技術(shù)和新興非易失存儲(chǔ)技術(shù)的關(guān)注,已達(dá)到如下圖所示的PPAC目標(biāo)。

而具體到芯片制造方面,我們則面臨包括精密圖形、新材料和提升良率在內(nèi)的三大挑戰(zhàn)。

“除了技術(shù)以外,晶圓廠、研發(fā)和設(shè)計(jì)成本也是芯片產(chǎn)業(yè)面臨的另一重大挑戰(zhàn)”,吳漢明說。他指出,如下圖所示,假設(shè)一個(gè)能生產(chǎn)32nm芯片的產(chǎn)線,需要的成本高達(dá)45億美元,研發(fā)成本則高達(dá)9億美金,設(shè)計(jì)成本也需要1億美金。到了16nm,晶圓廠的建設(shè)成本取到了90億美元,研發(fā)成本增加到18億美元,設(shè)計(jì)成本也漲到了22億美元,整體成本較之32億美元翻了一番,由此可見芯片持續(xù)微縮帶來的成本巨大挑戰(zhàn)。

“雖然芯片的難道和成本一直增加,但趨緩的摩爾定律給追趕者帶來機(jī)會(huì)”,吳漢明接著說。

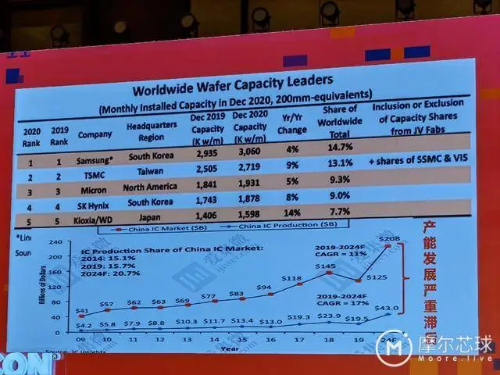

但吳漢明院士也強(qiáng)調(diào),即使如此,我國的集成電路產(chǎn)業(yè)還需要重視一個(gè)關(guān)鍵問題,那就是產(chǎn)能問題。據(jù)統(tǒng)計(jì),產(chǎn)能排名前五的晶圓廠包括三星、臺(tái)積電、美光、SK海力士和鎧俠,中國大陸并沒有任何一家企業(yè)位列其中。隨著科技的發(fā)展,芯片的產(chǎn)能需求會(huì)越來越高,為此我們必須加倍重視產(chǎn)能。

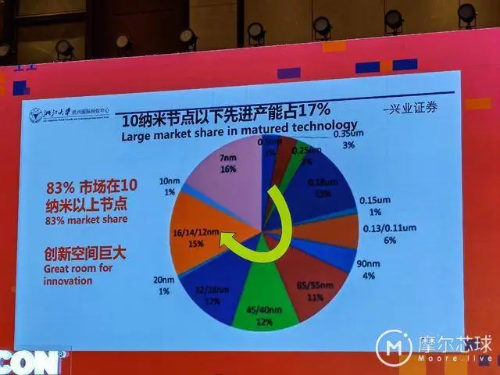

吳漢明院士同時(shí)還指出,如下圖所示,現(xiàn)在83%以上的芯片產(chǎn)能集中在10納米以上節(jié)點(diǎn),為此在他看來,在這些所謂的舊節(jié)點(diǎn)上,還有很大的創(chuàng)新空間。

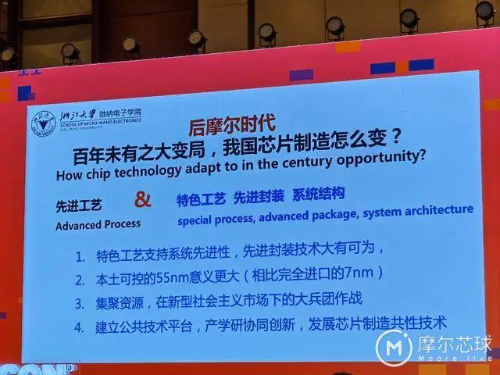

為此吳漢明院士指出,在后摩爾時(shí)代,我們正在面臨百年未有的大變局,我們應(yīng)該在關(guān)注先進(jìn)工藝的同時(shí),還要關(guān)注特色工藝、先進(jìn)封裝和系統(tǒng)結(jié)構(gòu),這對(duì)于當(dāng)前的中國集成電路來說,擁有重要的意義。

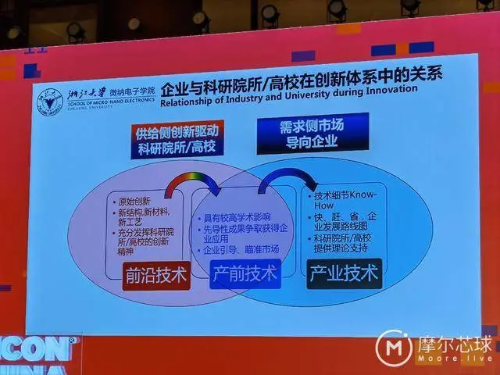

同時(shí),吳漢明院士對(duì)企業(yè)與科研院所/高校在創(chuàng)新體系中的關(guān)系給出了他的建議。

“與此同時(shí),浙江大學(xué)也會(huì)打造一個(gè)成套的工藝研發(fā)平臺(tái),為我國集成電路產(chǎn)業(yè)發(fā)展貢獻(xiàn)力量”,吳漢明最后表示。