包云崗,,中國科學院計算技術研究所研究員,、先進計算機系統(tǒng)研究中心主任,、中國科學院大學特聘教授,、中國開放指令生態(tài)(RISC-V)聯(lián)盟秘書長,,從事計算機體系結構和開源芯片方向前沿研究,,主持研制多款達到國際先進水平的原型系統(tǒng),相關技術在華為,、阿里等國內(nèi)外企業(yè)應用,。他曾獲「CCF-Intel 青年學者」獎、阿里巴巴最佳合作項目獎,、「CCF-IEEE CS」青年科學家獎等獎項,。

2020年底給某大廠做過一個報告,包含兩部分內(nèi)容:一部分是關于計算機體系結構,,尤其是CPU結構的演變,;另一部分關于處理器芯片設計方法。這里把第一部分內(nèi)容貼出來回答一下這個知乎問題,。

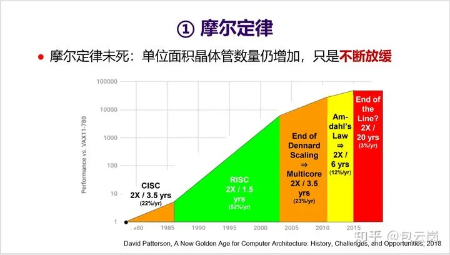

首先回顧一下計算機體系結構領域三個定律:摩爾定律,、牧本定律、貝爾定律,。摩爾定律就不用多說了,,但想表達一個觀點是摩爾定律未死,只是不斷放緩,。

2. 摩爾定律讓芯片上的晶體管數(shù)量不斷增加,,但一個問題是這些晶體管都被充分用起來了嗎?最近MIT團隊在《Science》上發(fā)表了一篇文章《There's plenty of room at the Top: What will drive computer performance after Moore's law?》,,給出他們的答案:顯然沒有,!

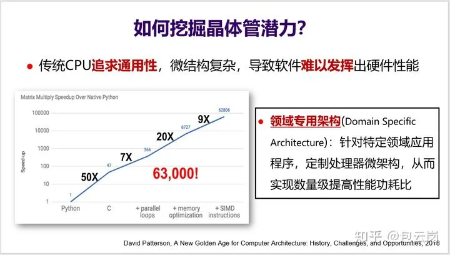

可以來看一下MIT團隊開展的一個小實驗(見下面PPT):假設用Python實現(xiàn)一個矩陣乘法的性能是1,那么用C語言重寫后性能可以提高50倍,,如果再充分挖掘體系結構特性(如循環(huán)并行化,、訪存優(yōu)化、SIMD等),,那么性能甚至可以提高63000倍,。然而,真正能如此深入理解體系結構,、寫出這種極致性能的程序員絕對是鳳毛麟角,。

問題是這么大的性能差異到底算好還是壞?從軟件開發(fā)角度來看,這顯然不是好事,。這意味著大多數(shù)程序員無法充分發(fā)揮CPU的性能,,無法充分利用好晶體管。這不能怪程序員,,更主要還是因為CPU微結構太復雜了,,導致軟件難以發(fā)揮出硬件性能。

如何解決這個問題,?領域專用架構DSA(Domain-Specific Architecture)就是一個有效的方法,。DSA可以針對特定領域應用程序,定制微結構,,從而實現(xiàn)數(shù)量級提高性能功耗比,。這相當于是把頂尖程序員的知識直接實現(xiàn)到硬件上。

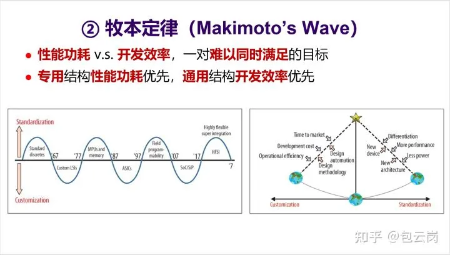

3. 第二個定律是牧本定律(也有稱”牧本波動“),。1987 年,, 原日立公司總工程師牧本次生(Tsugio Makimoto,也有翻譯為牧村次夫,,故稱為”牧村定律“) 提出,,半導體產(chǎn)品發(fā)展歷程總是在”標準化“與”定制化“之間交替擺動,大概每十年波動一次,。牧本定律背后是性能功耗和開發(fā)效率之間的平衡,。

對于處理器來說,就是專用結構和通用結構之間的平衡,。最近這一波開始轉向了追求性能功耗,,于是專用結構開始更受關注。

4. 第三個定律是貝爾定律,。這是Gordon Bell在1972年提出的一個觀察,,具體內(nèi)容如下面的PPT所述。值得一提的是超級計算機應用最高獎”戈登·貝爾獎“就是以他的名字命名,。

5. 貝爾定律指明了未來一個新的發(fā)展趨勢,,也就是AIoT時代的到來。這將會是一個處理器需求再度爆發(fā)的時代,,但同時也會是一個需求碎片化的時代,不同的領域,、不同行業(yè)對芯片需求會有所不同,,比如集成不同的傳感器、不同的加速器等等,。如何應對碎片化需求,?這又將會是一個挑戰(zhàn)。

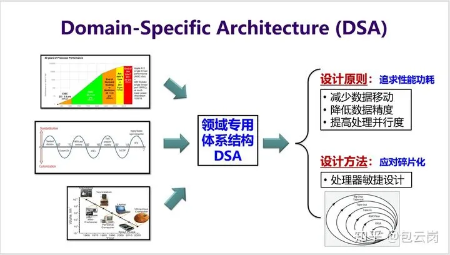

6. 這三個定律都驅動計算機體系結構向一個方向發(fā)展,那就是”DSA“,。如何實現(xiàn)DSA,,這又涉及到兩個方面:

為了追求性能功耗,有三條主要的設計原則(見下面PPT),;

為了應對碎片化需求,,則需要發(fā)展出處理器敏捷設計新方法。(這個回答就不介紹敏捷設計方法了)

7. 在談一些具體技術之前,,我們可以先總體看一下過去幾十年CPU性能是如何提升的,。下面這頁PPT列出了1995-2015這二十年Intel處理器的架構演進過程——這是一個不斷迭代優(yōu)化的過程,集成了上百個架構優(yōu)化技術,。

這些技術之間還存在很多耦合,,帶來很大的設計復雜度。比如2011年在Sandy Bridge上引入了大頁面技術,,要實現(xiàn)這個功能,,會涉及到超標量、亂序執(zhí)行,、大內(nèi)存,、SSE指令、多核,、硬件虛擬化,、uOP Fusion等等一系列CPU模塊和功能的修改,還涉及操作系統(tǒng),、編譯器,、函數(shù)庫等軟件層次修改,可謂是牽一發(fā)動全身,。(經(jīng)??吹接腥苏f芯片設計很簡單,也許是因為還沒有接觸過CPU芯片的設計,,不知道CPU設計的復雜度)

8. 處理器內(nèi)部有非常復雜的狀態(tài),,其狀態(tài)變化是由程序驅動的。也就是說,,處理器狀態(tài)取決于程序行為(見下面PPT),,而CPU體系結構層次的優(yōu)化思路就是發(fā)現(xiàn)程序行為中的共性特征并進行加速。

如何發(fā)現(xiàn)程序行為中的共性特征,,就是處理器優(yōu)化的關鍵點,,這需要對程序行為、操作系統(tǒng),、編程與編譯,、體系結構等多個層次都有很好的理解,,這也是計算機體系結構博士的基本要求。這也是為什么很多國外的計算機體系結構方向屬于Computer Science系,。

題外話:這兩天看到國內(nèi)成立集成電路一級學科,,這是一個好消息。不過要能培育CPU設計人才,,在課程設計上不要忽視了操作系統(tǒng),、編程與編譯這些傳統(tǒng)計算機科學的課程。

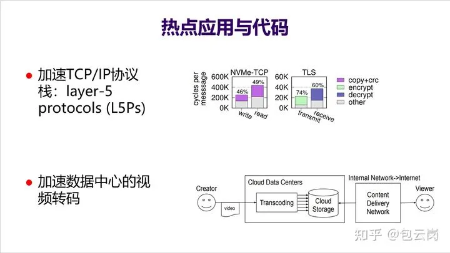

9. 舉兩個發(fā)現(xiàn)熱點應用和熱點代碼,、并在體系結構層次上優(yōu)化的例子,。一個例子是發(fā)現(xiàn)在不少領域TCP/IP協(xié)議棧五層協(xié)議(L5Ps)存在很多大量共性操作,比如加密解密等,,于是直接在網(wǎng)卡上實現(xiàn)了一個針對L5Ps的加速器,,大幅加速了網(wǎng)絡包處理能力。另一個例子是這次疫情導致云計算數(shù)據(jù)中心大量算力都用來做視頻轉碼,,于是設計了一個硬件加速器專門來加速視頻轉碼,,大幅提升了數(shù)據(jù)中心效率。

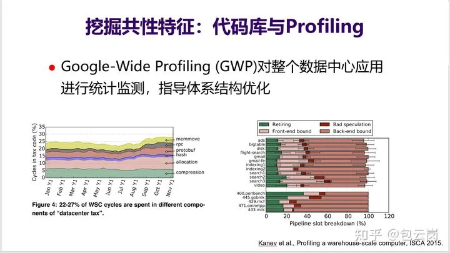

10. 發(fā)現(xiàn)和識別這種熱點應用和熱點代碼并不容易,,需要由很強大的基礎設施和分析設備,。比如Google在其數(shù)據(jù)中心內(nèi)部有一個GWP工具,能對整個數(shù)據(jù)中心應用在很低的開銷下進行監(jiān)測與統(tǒng)計,,找到算力被那些熱點程序/代碼消耗,,當前的CPU哪些部件是瓶頸。比如GWP顯示在Google數(shù)據(jù)中心內(nèi)部有5%的算力被用來做壓縮,。

正是得益于這些基礎工具,,Google很早就發(fā)現(xiàn)AI應用在數(shù)據(jù)中心中應用比例越來越高,于是開始專門設計TPU來加速AI應用,。

11. 下面分別從三個方面來介紹體系結構層面的常見優(yōu)化思路:減少數(shù)據(jù)移動,、降低數(shù)據(jù)精度、提高處理并行度,。

首先看一下如何減少數(shù)據(jù)移動,。第一個切入點是指令集——指令集是程序語義的一種表達方式。同一個算法可以用不同粒度的指令集來表達,,但執(zhí)行效率會有很大的差別,。一般而言,粒度越大,,表達能力變?nèi)?,但是?zhí)行效率會變高。

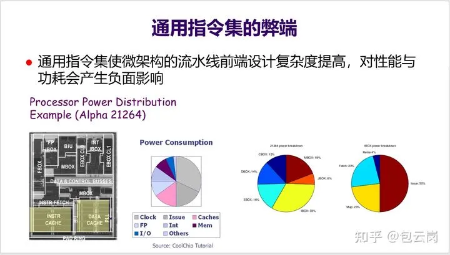

12. 通用指令集為了能覆蓋盡可能多的應用,,所以往往需要支持上千條指令,,導致流水線前端設計(取指、譯碼,、分支預測等)變得很復雜,,對性能與功耗都會產(chǎn)生負面影響。

13. 針對某一個領域設計專用指令集,,則可以大大減少指令數(shù)量,,并且可以增大操作粒度、融合訪存優(yōu)化,,實現(xiàn)數(shù)量級提高性能功耗比,。下面PPT的這組數(shù)據(jù)是斯坦福大學團隊曾經(jīng)做過的一項研究,從這個圖可以看出,,使用了”Magic Instruction“后,,性能功耗比大幅提升幾十倍。而這種Magic Instruction其實就是一個非常具體的表達式以及對應的電路實現(xiàn)(見PPT右下角),。

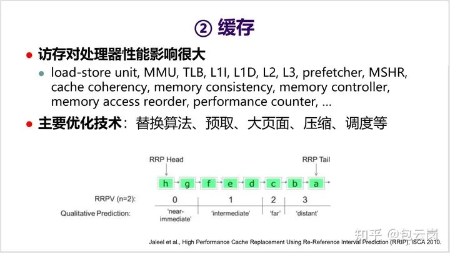

14. 第二個減少數(shù)據(jù)移動的常用方法就是充分發(fā)揮緩存的作用,。訪存部件其實是處理器最重要的部分了,涉及許多技術點(如下面PPT),。很多人都關注處理器的流水線多寬多深,,但其實大多數(shù)時候,訪存才是對處理器性能影響最大的,。

關于訪存優(yōu)化,,也有一系列技術,包括替換,、預取等等,。這些技術到今天也依然是體系結構研究的重點,這里就不展開細講了,。

15. 不再展開介紹訪存優(yōu)化技術,,就選最近比較熱的內(nèi)存壓縮方向介紹一下。

IBM在最新的Z15處理器中增加了一個內(nèi)存壓縮加速模塊,,比軟件壓縮效率提高388倍,,效果非常突出。

16. 英偉達也在研究如何在GPU中通過內(nèi)存壓縮技術來提升片上存儲的有效容量,,從而提高應用性能,。

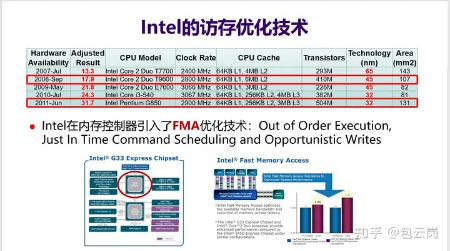

17. Intel在訪存優(yōu)化上很下功夫,可以通過對比兩款Intel CPU來一窺究竟,。Core 2 Due T9600和Pentium G850兩塊CPU,,工藝差一代,但頻率相近,,分別是2.8GHz和2.9GHz,,但性能差了77%——SPEC CPU分值G850是31.7分,,而T9600只有17.9分。

頻率相當,,為何性能會差這么多,?事實上,G850的Cache容量比T9600還要小——6MB L2 vs. 256KB L2 + 3MB L3,。

如果再仔細對比下去,,就會發(fā)現(xiàn)這兩款處理器最大的區(qū)別在于G850適配的內(nèi)存控制器中引入FMA(Fast Memory Access)優(yōu)化技術,大幅提高了訪存性能,。

18. 第二類體系結構優(yōu)化技術是降低數(shù)據(jù)精度,。這方面是這幾年研究的熱點,特別是在深度學習領域,,很多研究發(fā)現(xiàn)不需要64位浮點,,只需要16位甚至8位定點來運算,精度也沒有什么損失,,但性能卻得到數(shù)倍提升,。

很多AI處理器都在利用這個思路進行優(yōu)化,包括前段時間日本研制的世界最快的超級計算機”富岳“中的CPU中就采用了不同的運算精度,。因此其基于低精度的AI運算能力可以達到1.4EOPS,,比64位浮點運算性能(416PFLOPS)要高3.4倍。

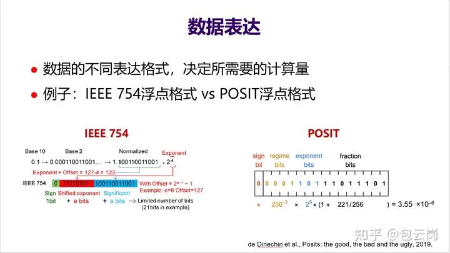

19. IEEE 754浮點格式的一個弊端是不容易進行不同精度之間的轉換,。近年來學術界提出一種新的浮點格式——POSIT,,更容易實現(xiàn)不同的精度,甚至有一些學者呼吁用POSIT替代IEEE 754(Posit: A Potential Replacement for IEEE 754),。

RISC-V社區(qū)一直在關注POSIT,,也有團隊實現(xiàn)了基于POSIT的浮點運算部件FPU,但是也還存在一些爭論(David Patterson和POSIT發(fā)明人John L. Gustafson之間還有一場精彩的辯論,,另外找機會再介紹),。

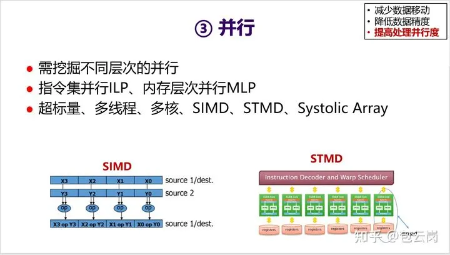

20. 體系結構層次的第三個優(yōu)化思路就是并行。這個題目中提到的”多核“,,就是這個思路中一個具體的技術,。除了多核,還有其他不同層次的并行度,,比如指令集并行,、線程級并行、請求級別并行,;除了指令級并行ILP,,還有訪存級并行MLP??傊?,提高處理并行度是一種很有效的優(yōu)化手段,。

以上是關于計算機體系結構尤其是CPU結構優(yōu)化思路的一個大致梳理,供大家參考,??偨Y來說就是兩點結論:

領域專用體系結構DSA是未來一段時間體系結構發(fā)展趨勢;

體系結構層面3條優(yōu)化路線——減少數(shù)據(jù)移動,、降低數(shù)據(jù)精度、提高處理并行度,。

文章來自知乎,,作者包云崗