硅基器件已經(jīng)成為我們行業(yè)60多年的基礎(chǔ),這非常令人驚訝,因?yàn)樽畛醯逆N基器件將難以大規(guī)模集成。(值得一提,GaAs器件還開發(fā)了一個(gè)獨(dú)特的微電子市場領(lǐng)域。)

最近,令人驚訝的是,通過引入諸如FinFETs之類的拓?fù)浣Y(jié)構(gòu)以及即將到來的納米片,硅場效應(yīng)器件獲得了新的生命。硅基互補(bǔ)FET的研究正在進(jìn)行中 (CFET)設(shè)計(jì)達(dá)到量產(chǎn)狀態(tài),其中nMOS和pMOS器件是垂直制造的,從而消除了當(dāng)前單元設(shè)計(jì)中的橫向n-p間距。

另外,材料工程學(xué)的進(jìn)步已經(jīng)將(拉伸和壓縮)應(yīng)力納入硅通道晶體結(jié)構(gòu)中,以增強(qiáng)自由載流子遷移率。

但是,硅設(shè)備收益遞減的點(diǎn)正在逼近:

由于高電場下的速度飽和,無硅載流子遷移率接近最大值

尺寸的持續(xù)縮小降低了硅半導(dǎo)體的導(dǎo)帶和價(jià)帶邊緣的“自由載流子態(tài)密度”(DoS)–填充更大范圍的載流子態(tài)需要更多的能量

與Fin圖案相關(guān)的統(tǒng)計(jì)過程變化很大

散熱片的熱傳導(dǎo)導(dǎo)致局部“自熱”溫度升高,從而影響了幾種可靠性機(jī)制(HCI,電遷移)

為解決以上問題,目前業(yè)界正在進(jìn)行大量研究,以評估與硅完全不同的場效應(yīng)晶體管材料的潛力,但這也與當(dāng)前的大批量制造操作相一致。一種選擇是探索 器件通道的單層二維半導(dǎo)體材料,例如二硫化鉬(MoS2)。

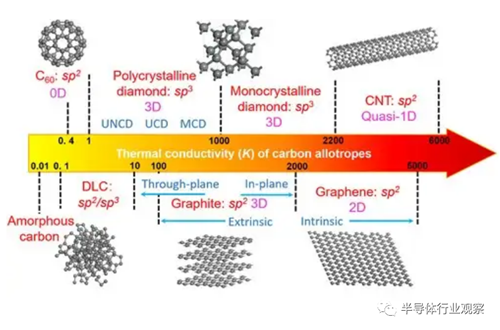

另一個(gè)有希望的選擇是從碳納米管(CNT)構(gòu)造設(shè)備溝道。下圖提供了碳鍵獨(dú)特性質(zhì)的簡單圖示。(我對化學(xué)反應(yīng)有些不熟悉,但我記得“ sp2”鍵是指原子核周圍亞軌道“ p殼”中相鄰碳原子的電子配對。沒有“懸掛鍵”,并且碳材料是惰性的。)

請注意,石墨,石墨烯和CNT的化學(xué)結(jié)構(gòu)相似-使用石墨進(jìn)行的實(shí)驗(yàn)材料分析更加容易,并且最終可以擴(kuò)展到CNT處理。

在最近的IEDM會議上,臺積電提供了有關(guān)CNT器件制造進(jìn)展的有趣更新。本文總結(jié)了該演講的重點(diǎn)。

CNT設(shè)備具有一些引人注目的功能:

極高的載流子遷移率(>3,000cm2在/V-sec,“彈道運(yùn)輸”(ballistic transport),散射最小)

非常薄的CNT主體尺寸(例如,直徑~1nm)

低寄生電容

優(yōu)良的導(dǎo)熱性

低溫(<400C)處理

最后一個(gè)功能特別有趣,因?yàn)樗€為基于硅的高溫制造與后續(xù)的CNT處理集成提供了潛力。

門介電(Gate Dielectric)

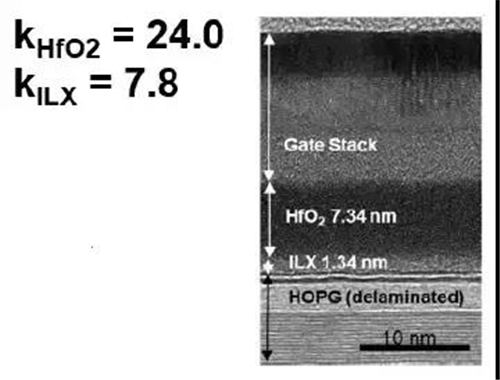

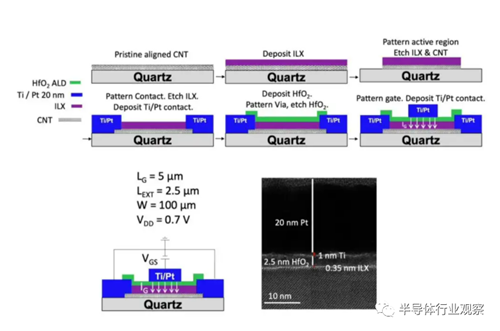

臺積電開發(fā)了獨(dú)特的工藝流程來為CNT器件提供“高K”電介質(zhì)等效柵極氧化物,類似于當(dāng)前硅FET的HKMG處理。

上面的TEM圖說明了CNT的橫截面。為了與獨(dú)特的碳表面兼容,需要沉積初始界面電介質(zhì)(Al2O3)–即需要在碳上對該薄層進(jìn)行適當(dāng)?shù)某珊撕驼稀?/p>

隨后,添加高K HfO2膜的原子級沉積(ALD)。(如前所述,這些關(guān)于材料性能的介電實(shí)驗(yàn)是在石墨基底上完成的。)

這些柵極電介質(zhì)層的最小厚度受到非常低的柵極泄漏電流(例如,柵極長度為10nm的<1 pA/CNT)的限制。下面說明用于測量柵極到CNT泄漏電流的測試結(jié)構(gòu)。(對于這些電測量,CNT結(jié)構(gòu)使用石英襯底。)

實(shí)驗(yàn)得出的“最佳”尺寸為t_Al2O3=0.35nm和t_HfO2=2.5nm。由于這些極薄的層,Cgate_ox非常高,從而改善了靜電控制。(請注意,這些層厚于CNT的直徑,其影響將在稍后討論。)

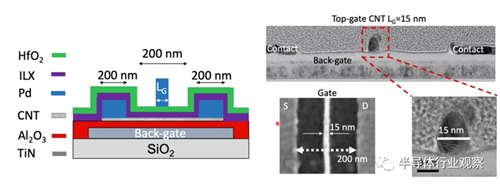

門方向(Gate Orientation)

臺積電評估的CNT器件采用了獨(dú)特的“頂柵加背柵”拓?fù)洹?/p>

頂柵提供常規(guī)的半導(dǎo)體場效應(yīng)器件輸入,而(較大的)背柵提供對S/D擴(kuò)展區(qū)域中載流子的靜電控制,以有效降低寄生電阻Rs和Rd。而且,背柵會影響CNT與鈀金屬之間的源極和漏極接觸電勢,從而降低肖特基二極管勢壘以及在該半導(dǎo)體-金屬界面處的相關(guān)電流行為。

設(shè)備電流

CNT pFET的IV曲線(線性和對數(shù)Ids(用于亞閾值斜率測量))如下所示。對于此實(shí)驗(yàn),Lg=100nm,S/D間距為200nm,CNT直徑=1nm,t_Al2O3= 1.25nm,t_HfO2=2.5nm。

對于此測試(制造在石英基板上),單個(gè)CNT支持超過10uA的Ids。接近上述目標(biāo)尺寸的更薄電介質(zhì)將實(shí)現(xiàn)進(jìn)一步的改進(jìn)。

最終將在生產(chǎn)制造中使用平行CNT-相關(guān)的制造指標(biāo)將是“每微米CNT的數(shù)量”。例如,4nm的CNT間距將被引用為“ 250CNTs/um”。

挑戰(zhàn)

規(guī)劃CNT生產(chǎn)時(shí)肯定要解決一些挑戰(zhàn)(僅舉幾例):

規(guī)則/均勻的CNT沉積,具有非常干凈的表面,用于介電成核

需要最小化柵極電介質(zhì)堆棧中的載流子“陷阱密度”

最佳S / D接觸電位材料工程

設(shè)備建模設(shè)計(jì)

上面的最后一個(gè)挑戰(zhàn)尤其值得注意,因?yàn)楫?dāng)前用于場效應(yīng)晶體管的緊湊型器件模型肯定不夠用。CNT柵氧化層拓?fù)渑c平面或FinFET硅通道完全不同。由于柵極到溝道的電場本質(zhì)上是徑向的,因此與平面器件一樣,“有效柵極氧化物”并不存在簡單的關(guān)系。

此外,S/D擴(kuò)展需要唯一的Rs和Rd模型。而且,CNT柵氧化層的厚度比CNT的直徑厚,從而導(dǎo)致從柵到S/D延伸以及到(小間距分隔)平行CNT的大量邊緣場。為基于CNT的設(shè)計(jì)開發(fā)合適的緊湊模型是一項(xiàng)持續(xù)的工作。

順便說一句,CNT“環(huán)繞柵極”氧化物(類似于納米片周圍的所有柵極)將比沉積的頂部柵極氧化物有所改進(jìn),但難以制造。

臺積電顯然正在投入大量研發(fā)資源,為“不可避免的”后硅器件技術(shù)的引入做準(zhǔn)備。CNT的制造和電學(xué)表征結(jié)果證明了該器件替代產(chǎn)品的巨大潛力。