蘋果9月推出 A14 仿生芯片,接著華為麒麟 9000 系列芯片也將隨Mate40 系列手機一起推出,而高通新一代驍龍 875也將在12月初發(fā)布,相同的是芯片都將是采用5nm 工藝,同時也意味著半導體工藝 5nm 的時代正在全面到來。

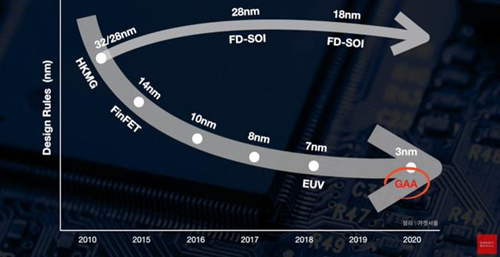

半導體的制程工藝,從 10nm 到 7nm 再到現(xiàn)在的 5nm,進化的幅度越來越小,但每進一步,都是整個行業(yè)付出巨大研發(fā)成本的結果。相信大家平時刷新聞時已經(jīng)有所了解,芯片的制程工藝越來越小,等于晶體管越做越小,當工藝越來越接近極限時,難度就會呈指數(shù)級上升。

最好的例子就是芯片巨頭英特爾在 14nm 節(jié)點長達 5 年的停滯,一度讓 “摩爾定律已死”的言論甚囂塵上。好在另一方面,臺積電和三星在制程技術上突飛猛進,從 10nm 到 7nm 再到今年的 5nm,一路順利推進,并超越了英特爾。

盡管后兩者在制程名稱上有玩 “數(shù)字游戲”的成分,但他們對推進半導體制程技術進化、延續(xù)摩爾定律所做的貢獻有目共睹。

這些年來,芯片制程工藝能夠不斷微縮,性能可以不斷增強,都有賴于整個半導體行業(yè)以及學術領域的勇敢創(chuàng)新和不懈努力。而當節(jié)點進一步微縮,5nm 之后的 3nm、2nm、1nm,新的問題又會出現(xiàn),甚至原來拯救摩爾定律的 3D FinFET 晶體管都將無法應對極限微觀世界的要求。

接下來,我們會越來越頻繁地聽到一個新名詞——GAA(環(huán)繞式柵極技術晶體管)。

什么是 GAA 環(huán)繞式柵極技術晶體管?

1、從 3D FinFET 到 GAA,5nm 之后就靠它了

作為取代 3D FinFET 晶體管的全新技術,其實 GAA 環(huán)繞式柵極技術晶體管和 3D FinFET 有著千絲萬縷的聯(lián)系,因此我們需要從 3D FinFET 晶體管說起。

在《臺積電 5 納米吊打英特爾 10 納米?別糾結了,這只是 “數(shù)字游戲”》一文中,其實IT之家已經(jīng)為大家介紹過 3D FinFET 晶體管,這里再簡單回顧一下。

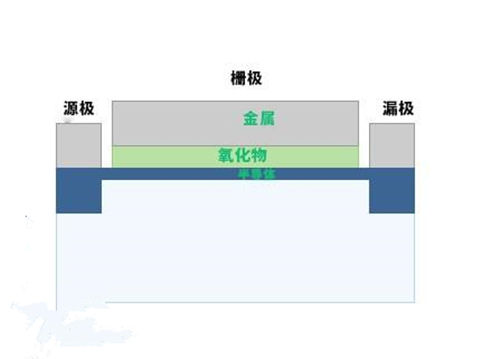

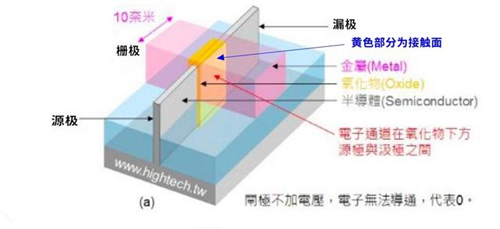

其實所謂晶體管,用通俗易懂的話來講,就是用半導體材料制作的電流開關結構。左邊一個源極(半導體),右邊一個漏極(半導體),中間加個柵極(金屬),讓柵極來控制電流從源極到漏極的通斷。

在過去,柵極和源極、漏極之間接觸的地方是一個平面,形狀差不多是一個矩形,柵極正是依靠這個接觸面來對源極和漏極的電流進行控制。

可是,晶體管越做越小,這個接觸面的寬度(其實就是柵極的寬度)也越來越窄,當窄到一定程度時(大概是 20nm 左右),柵極對電流的控制力就會大幅減弱。

控制力減弱,就會導致源極的電流穿透柵極,直接和漏極導通,這種情況叫漏電。很顯然,漏電不是個好事情,它會導致芯片發(fā)熱量急劇上升。

所以半導體工藝進化之路在 20nm 左右曾一度面臨停滯,摩爾定律遭受威脅。

怎么辦呢?其實只要柵極和源極、漏極之間的接觸面積足夠大,就能控制住電流。這個接觸面的寬度不能增加,那就只能增加長度了。

1999 年華人教授胡正明帶領加州大學伯克利分校的研究團隊發(fā)明了 FinFET 晶體管技術和 UTB-SOI 技術,解決了上面說的問題。

其中,F(xiàn)inFET 晶體管技術是我們聽過最多的。它的解決思路就是改造晶體管的結構,將源極和漏極做成像鰭片一樣直立的樣子,然后讓柵極三面包圍住鰭片,就像下面這樣。這樣,等于是讓柵極的寬度不變,通過巧妙地增加長度,來大大增加接觸面積,從提升對電流的控制。

換句話說,原來只有一個接觸面,現(xiàn)在有三個了,哪怕柵極寬度在進一步縮小,也不怕。

由于這種鰭片結構是立體的形態(tài),所以也叫做 3D FinFET。

3D FinFET 技術的出現(xiàn)解決了晶體管工藝縮小引發(fā)的漏電的問題,讓半導體的制程可以進一步推進。

隨后,經(jīng)過十多年的產(chǎn)業(yè)化推進,英特爾在 2011 年首先推出了使用 22nm FinFET 工藝的第三代 Core 處理器,這標志著摩爾定律的延續(xù)。

胡正明教授也被人們稱為 FinFET 教父,以及 “拯救摩爾定律的男人”。而 3D FinFET 技術也伴隨著半導體產(chǎn)業(yè)發(fā)展,一路走到今天的 7nm、5nm 時代。

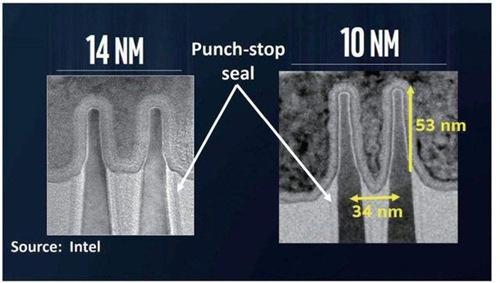

但是,隨著芯片制程的進一步微縮,到了 5nm 之后的 3nm、2nm 等等,3D FinFET 也將迎來它的極限,鰭片距離太近、漏電重新出現(xiàn),物理材料的極限都讓 3D FinFET 晶體管難以為繼。

還有隨著工藝微縮,假如原來一個 FinFET 晶體管上可以放三個鰭片,現(xiàn)在只能放一個,所以就得把鰭片增高。可是鰭片越來越高,到一定高度后,很難在內(nèi)部應力作用下保持直立,F(xiàn)inFET 結構就很難形成了。

總之就是,5nm 之后,3D FinFET 也不能用了。這時候,就輪到 GAA 環(huán)繞式柵極技術晶體管技術登場了。

GAA 全稱 Gate-All-Around ,是一種環(huán)繞式柵極技術晶體管,也叫做 GAAFET。它的概念的提出也很早,比利時 IMEC Cor Claeys 博士及其研究團隊于 1990 年發(fā)表文章中提出。

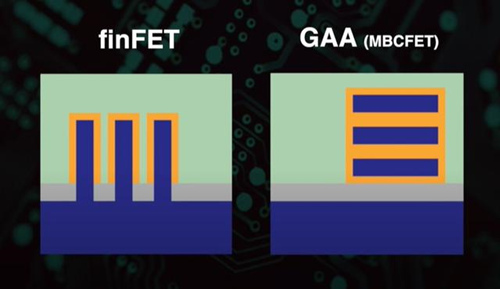

其實 GAAFET 相當于 3D FinFET 的改良版,這項技術下的晶體管結構又變了,柵極和漏極不再是鰭片的樣子,而是變成了一根根 “小棍子”,垂直穿過柵極,這樣,柵極就能實現(xiàn)對源極、漏極的四面包裹。

看起來,好像原來源極漏極半導體是鰭片,而現(xiàn)在柵極變成了鰭片。所以 GAAFET 和 3D FinFET 在實現(xiàn)原理和思路上有很多相似的地方。

不管怎么說,從三接觸面到四接觸面,并且還被拆分成好幾個四接觸面,顯然,這次柵極對電流的控制力又進一步提高了。此外,GAA 的這種設計也可以解決原來鰭片間距縮小的問題,并且在很大程度上解決柵極間距縮小后帶來問題,例如電容效應等。

總之,在 GAAFET 技術的巧妙幫助下,半導體制程工藝的進化之路還將進一步往前走,并將成為 5nm 之后大家經(jīng)常聽到的關鍵詞。

2、三星、英特爾和臺積電,同樣的態(tài)度,不同的進展

GAAFET 技術如此重要,顯然目前芯片代工的三巨頭英特爾、三星和臺積電都在積極備戰(zhàn),準備在 5nm 之后的節(jié)點上大干一場。

首先要說明的是,前面我們講到源極到漏極的 “小棍子”,只是舉例,實際上也可以是其他形狀,例如圓柱狀、甚至是板狀的等等。

就這一點,目前行業(yè)里分幾種方案:

納米線,就是采用圓柱或者方形的截面;

板片狀,顧名思義,就是源極漏極的半導體設計成水平的板塊狀,通常會堆疊多個穿透柵極;

六角形截面;

納米環(huán)技術,就是穿透柵極的半導體為環(huán)形截面。

在三巨頭中,目前最積極高調(diào)的是三星,他們采用的是第二種方案,也就是堆疊的板片狀方案。目前三星也是三巨頭中唯一一家公布自己在 GAA 上詳細技術方案的企業(yè)。

三星還給自家 GAA 技術取了個獨特的名字:Multi-Bridge Channel,簡稱 MBCFET。

三星表示,他們會在 3nm 這一節(jié)點上使用 MBCFET 技術。MBCFET 相比納米線技術擁有更大的柵極接觸面積,從而在性能、功耗控制上會更加出色。

就板片狀的技術方案來說,三星透露其目前設計每個晶體管上堆疊 3 條板片,板片厚度為 5nm,板片之間的距離為 10nm,同時柵極長度為 12nm 等。

在具體表現(xiàn)方面,三星還稱第一代的 3nm MBCFET 相比 7nm FinFET 會有 35% 的性能提升,功耗會降低 50%,芯片面積則會縮減 45%,電壓則可以下降到 0.7V。

三星更是信心滿滿地表示,2020 年底,他們的 MBCFET 就可以開始風險試產(chǎn),2021 年有望大規(guī)模量產(chǎn),同時 2021 年他們還會推出第一代 MBCFET 的優(yōu)化版本。

值得一提的是,三星在 GAA 上也嘗試了其他技術方案,不同方案在性能、功率方面的表現(xiàn)也不同,未來可以根據(jù)芯片應用場景的差異來匹配對應的方案。

相比三星的激進,臺積電這邊就相對保守了,目前他們已經(jīng)表示,3nm 節(jié)點上將會繼續(xù)打磨 FinFET 技術,而不是急于上馬 GAAFET。

主要原因是臺積電切入 GAA 技術的時間相對晚于三星,同時也為產(chǎn)業(yè)鏈平穩(wěn)過渡考慮。至于什么時候會使用 GAA 技術,官方還沒有明確公布。但根據(jù)外界的消息,臺積電會在 2nm 節(jié)點上采用 GAA 技術。

臺積電已表示,2nm 研發(fā)生產(chǎn)將落腳新竹寶山,將規(guī)劃建設 4 個超大型晶圓廠,投入 8000 名工程師,目前已經(jīng)交付研發(fā),根據(jù)規(guī)劃,2nm 工藝預計會在 2023 年開始風險試產(chǎn),2024 年量產(chǎn)。

至于英特爾,按照他們的進度,2021 年會推出 7nm 工藝,采用的仍然是目前的 SuperFinFET,而到 2023 年,他們會在 5nm 這個節(jié)點上放棄 FinFET 晶體管,轉向 GAA 環(huán)繞柵極晶體管。這個消息來自產(chǎn)業(yè)鏈,并非英特爾官方公布,但此前英特爾曾表示,將在 5nm 工藝重新奪回領導地位,由此來看,他們在 2023 年的 5nm 節(jié)點上推出 GAA 工藝是大概率會發(fā)生的。

3、半導體行業(yè)還沒有到極限

就像 FinFET 工藝拯救了芯片產(chǎn)業(yè),在 5nm 之后的時代,GAAFET 也將成為帶領半導體行業(yè)進一步發(fā)展的關鍵。當然,在這背后,每前進一步,都是行業(yè)付出巨大努力的結果。

就以 GAA 技術來說,三星透露其自家 3nm GAA 的研發(fā)成本比 5nm FinFET 更高,有可能超過 5 億美元,巨大的研發(fā)成本首先就是擺在行業(yè)面前的一道坎。

同時 GAAFET 的工藝制造難度也是極高的,具體的細節(jié)這里就不說了,最難的地方自然是如何讓柵極環(huán)繞源極和漏極的納米線,這里面的工藝極其復雜,也只有對 FinFET 技術爐火純青的半導體巨頭才能應對這樣的技術挑戰(zhàn)。

此外,和 GAA 技術配套的 EUV 極紫外光刻技術也需要進一步成熟,解決光刻功率不夠以及光子噪音等問題。

但好消息時,因為 GAA 相當于傳統(tǒng) FinFET 的 “改良版”,因此生產(chǎn)制造的很多技術細節(jié)和步驟是可以共用的,這意味著像三星、臺積電和英特爾這些對 FinFET 技術非常熟悉的巨頭,在 GAA 技術過渡時可能會比過去更加順暢,產(chǎn)業(yè)化的時間也可能會更短。

最后,IT之家想說的是,GAA 技術的推進,的確在很大程度上推進半導體工藝特別是先進制程上的發(fā)展。但隨著制程技術越來越接近物理極限,想要把芯片繼續(xù)做薄做小,先進制程也并不是唯一的道路,材料、封裝等也都可以稱為突破的道路。

胡正明教授曾經(jīng)說過:FinFE 證實了這個產(chǎn)業(yè)還有很多可以用我們的智慧來解決的問題,我還真是看不到半導體產(chǎn)業(yè)發(fā)的極限。只要這個世界仍然對運算有需求,半導體行業(yè)的人們就會想出智慧的解決方案來拓寬行業(yè)的天花板,用技術讓這個世界更加美好。