在過去很長的一段時間中,AMD一直無法在桌面處理器的單核心性能領(lǐng)先Intel,只能靠著在單一處理器封裝塞入更多核心,以及設(shè)定較低的價格,與對手在市場相互拼搏,然而AMD卻透過Ryzen 5000系列處理器反轉(zhuǎn)此一情況,就讓我們一起來看看Zen 3架構(gòu)的改變之處。

重新設(shè)計整體架構(gòu)

AMD在2017年的時候就曾宣示,他們將提供世界上最好的桌面處理器(We wanted to deliver the best desktop processors in the world andchange the industry along the way.),如今他們透過Zen 3架構(gòu)的Ryzen 5000系列處理器達(dá)成這一目標(biāo),我們通過性能實測,看到Ryzen 9 5900X的性能確實能超越其主要競爭對手Intel Core i9-10900K。

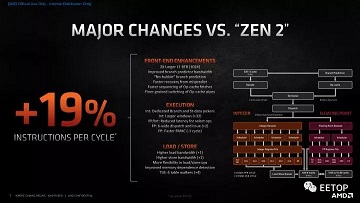

繼AMD先前推出的Zen與Zen 2架構(gòu)后,Zen 3的是款完全重新設(shè)計(Ground-up Redesign)的處理器架構(gòu),包含強(qiáng)化前端、執(zhí)行引擎、存取、SoC架構(gòu)等部分都經(jīng)過改善,并帶來了顯著的性能與功能提升。

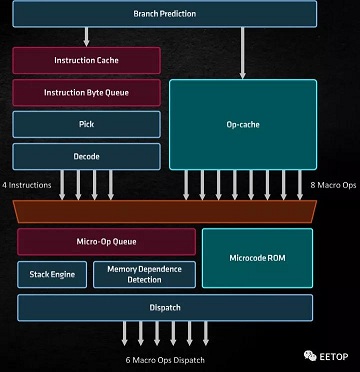

強(qiáng)化前端的目標(biāo)為增加大量分枝的大型程序預(yù)取(Fetching)性能,尤其在大量分枝的大型程序,將L1分枝預(yù)測的緩沖區(qū)加倍至1024個,并增加分枝預(yù)測器的通道寬度,增加預(yù)測錯誤的回復(fù)速度,提升循序預(yù)取性能,并讓切換cache流水線的粒度更細(xì)。

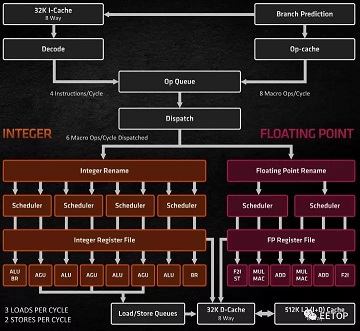

在執(zhí)行引擎部分,新架構(gòu)的設(shè)計目標(biāo)為縮短延遲并加大架構(gòu)以提高指令等級平行化(ILP,Instruction-Level Parallelism)的能力,在整數(shù)數(shù)據(jù)取用器、整數(shù)窗口、浮點數(shù)通道寬度、浮點數(shù)乘積累加運(yùn)算等部分也都進(jìn)行最佳化與性能提升。

存取方面的改良目標(biāo)為擴(kuò)大架構(gòu)并強(qiáng)化預(yù)取能力,以滿足執(zhí)行引擎所需的更大量數(shù)據(jù)吞吐量,數(shù)據(jù)讀取與寫入的時鐘頻率較Zen 2皆有所提升。

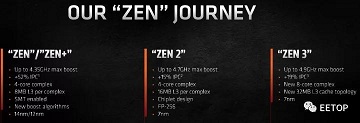

▲ Zen架構(gòu)的旅程始于2017年,到現(xiàn)在已經(jīng)進(jìn)入Zen3世代。

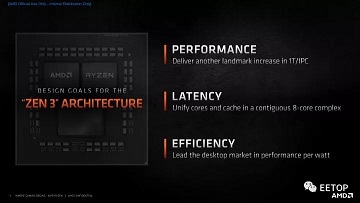

▲ Zen3改進(jìn)的重點為提升IPC/單核心性能、降低延遲、提升功耗效率。

▲ Zen3重新設(shè)計整個處理器,前端、執(zhí)行引擎、存取、SoC架構(gòu)都有改進(jìn)。

▲預(yù)取與解碼區(qū)塊的架構(gòu)也有所更新,以降低分支預(yù)測的延遲。

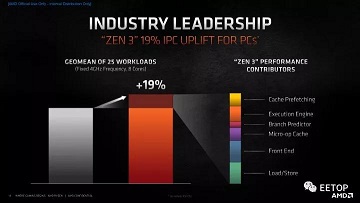

▲ Zen 3透過多項功能改善,達(dá)到IPC平均提升19%的成就。

▲這19%來自Cache預(yù)取、執(zhí)行引擎、分枝預(yù)測、微指令Cache、前端、存取等各項性能改進(jìn)的貢獻(xiàn)。

打破CCX屏障

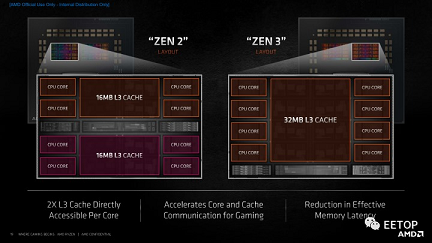

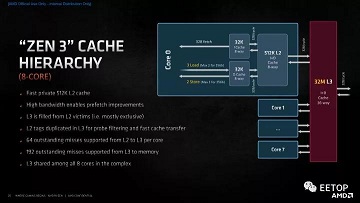

Zen 3的另一項重大改進(jìn),就是改進(jìn)了SoC架構(gòu),目標(biāo)同樣以降低延遲為主,同時縮短處理器核心對核心、核心對Cache、主存儲器等數(shù)據(jù)存取的延遲,并將L3Cache叢集增大1倍。

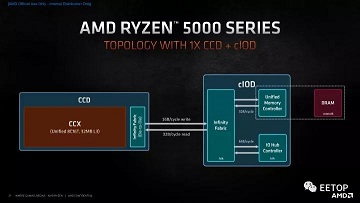

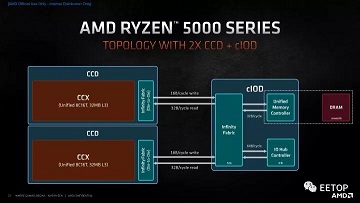

在Zen 2架構(gòu)的設(shè)計中,單一處理器封裝最多可以容納2組CCD(Compute Die,運(yùn)算裸片)與1組IOD(Input/Output Die,輸出入裸片),每組CCD最多可以容納2組CCX(Core Complexes,核心復(fù)合體),而每組CCX最多可以容納4個處理器核心。舉例來說,可以透過2組具有4個處理器核心的CCX,組成1組CCD,達(dá)成8核心處理器配置。

而Zen 3則將CCX可以容納的核心數(shù)提升至8個,每組CCD則只能容納1組CCX。因此8核心處理器會有1組具有8個處理器核心的CCX,組成1組CCD。

這樣最大的好處是可以把原本每組叢集只能容納4個核心的架構(gòu),改變?yōu)榭梢匀菁{8個核心,且把原本的2組16MB L3 Cache存儲器,合并為1組32MB的組態(tài)。

如此一來可以縮短處理器核心之間通訊的延遲,例如在Zen 2架構(gòu)中如果位于不同CCX的處理器核心的需要溝通,則某核心需透過Infinity Fabric將數(shù)據(jù)傳至IOD,再由IOD交至另一核心,將會因為傳輸延遲而影響性能,若處理器核心位于同一CCX則無此問題。

另一方面,統(tǒng)一的32MB L3 Cache存儲器也比拆分為2組16MB更具效率,且能容納更大筆的數(shù)據(jù),有助于提升游戲性能表現(xiàn)。

在制程方面,Zen 3的CCD采用與Zen 2一樣的臺積電7nm節(jié)點制程,并繼承在Ryzen 3000XT系列處理器所納入的設(shè)計改良,因此能再次推升最高時脈。IOD則完全延用先前12nm制程與設(shè)計,并讓處理器相容于先前推出的500、400系列芯片片組。

▲Zen 3大改了CCX的組態(tài),將原本只能容納4個處理器核心的限制提升至8個,也讓2組16MB L3 Cache存儲器合并為統(tǒng)一32MB區(qū)塊。

▲這樣的改變也讓8個處理器核心能共享同一塊L3 Cache存儲器,有助于提升多工性能表現(xiàn)。

▲以8核心的Ryzen 5000系列處理器為例,處理器封裝中包含CCD(其中有1組CCX)與IOD各1組。

▲ 16核心部分則有2組CCD與1組IOD。

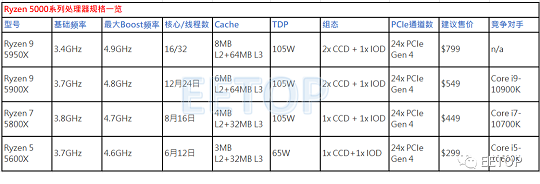

▲首波推出的4款Ryzen 5000系列處理器價格從美金299元至799元不等,其中只有Ryzen5 5600X附上Wraith Stealth散熱器。

▲相較前代的Ryzen 3000XT系列處理器,Ryzen 5000系列處理器的同級產(chǎn)品皆漲價美金50元。

整體而言,Ryzen 5000系列處理器的「歷史定位」在于單核心性能超級Intel旗艦產(chǎn)品,且依然維持核心較多的優(yōu)勢,因此無論在單核心或多核心程序表現(xiàn)都能追上或超越Intel(也需考慮軟件、編譯器、指令集等最佳化因素造成的性能影響),在游戲、電競、美術(shù)設(shè)計、影片編輯、電腦輔助制造(CAM)、電腦輔助設(shè)計(CAD)等應(yīng)用上都能帶來性能優(yōu)勢。

比較可惜的是,Ryzen 5000系列處理器較同級的Ryzen 3000XT貴了50美元(如Ryzen 5 5600X與Ryzen 5 3600XT相比),這樣的定價策略當(dāng)然可以解釋為新款處理器帶來更大的性能提升,但仍與消費者的期望相左。

有趣的是,在AMD發(fā)表Ryzen5000系列處理器的消息后,Intel也不甘示弱,以RocketLake-S處理器反擊,并不小心把牙膏擠太大力,對于消費者而言,這樣一來一往的競爭往往能讓產(chǎn)品的性能、價格更加親民,或許雙方未來都會陸續(xù)更貼近市場需求以得到消費者的青睞。