摘要:“一切都是為了您的電源更加可靠,!”對于帶使能EN引腳的LDO,,雖然我們都知道是用來開、關(guān)器件,,但是您知道如何靈活使用才能達到您想要的可靠電源的設(shè)計目標(biāo)嗎,?閱讀本文您將得到啟發(fā),并能舉一反三,。

1. 以ZL6205為例,,先簡單介紹一下。

致遠微電子推出的ZL6205系列LDO,,具有低壓差(240mV@500mA),,較好的輸出電壓精度(±1%),較大的負載電流特性,,同時集成欠壓,,過流,短路,,過溫等保護功能,。同樣ZL6205也帶EN腳,下文就以ZL6205為例,,結(jié)合ZL6205內(nèi)部集成的快速放電電路,,舉例說明EN腳在最常見的兩種使能方式下對輸出產(chǎn)生的不同效果。

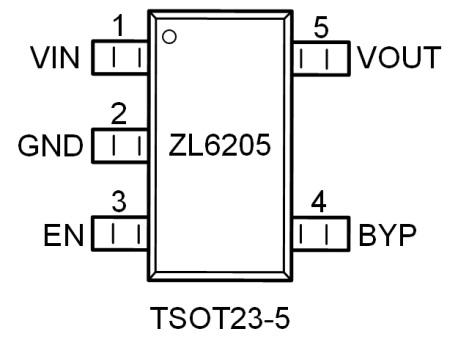

圖1 ZL6205引腳信息

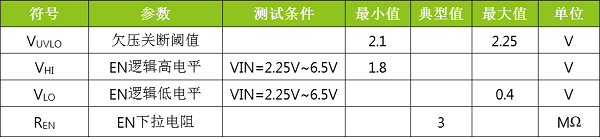

在了解EN腳不同使能方式之前,,有必要了解下ZL6205的一些電氣特性,。表1為ZL6205數(shù)據(jù)手冊里的部分電氣參數(shù)。VUVLO為ZL6205的欠壓關(guān)斷閾值電壓,,小于這個電壓值,,芯片處于關(guān)閉狀態(tài),REN為內(nèi)部集成的下拉電阻,,EN懸空時內(nèi)部拉為低電平,。EN引腳為高電平使能引腳,在推薦的工作電壓范圍內(nèi),,VHI和VLO分別為可靠識別的高電平(≥1.8V)和低電平(≤0.4V),。

表1 相關(guān)電氣參數(shù)

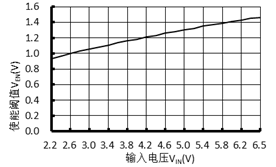

但是表1中的VHI和VLO不是實際的使能電壓閾值,圖2的曲線才是ZL6205的在不同輸入電壓下的實際使能電壓閾值,,可以看到隨著ZL6205輸入電壓的升高,,使能電壓閾值會跟著升高,但ZL6205的使能電壓閾值的回滯電壓很小。例如ZL6205在VIN=4.2V的時候,,VEN=1.2V是上電時的使能電壓閾值,,也是掉電時的禁能電壓閾值。

圖2 EN使能閾值與輸入電壓的關(guān)系

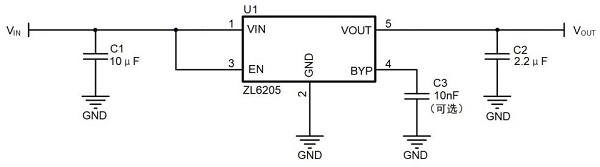

2. 方式一:直接上拉使能

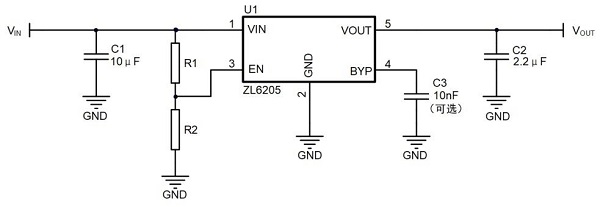

圖3為電源常見的使能方式,,EN腳與VIN腳直接短接,。當(dāng)ZL6205上電時,VEN始終VIN相等,,有時候VIN與EN腳間串聯(lián)一個電阻(常見的數(shù)k到數(shù)十k),,但通常EN引腳的輸入阻抗較大,ZL6205的REN的阻值為3MΩ,,所以EN腳電壓信號還是會與VIN基本保持一致,。

圖3 直接上拉使能

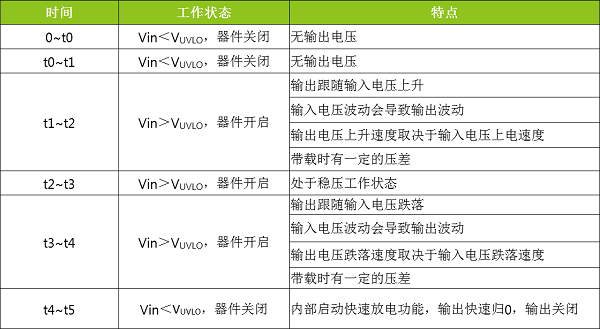

按照上圖的電路設(shè)計,ZL6205在輕載時上下電會得到圖4這樣的輸入輸出電壓曲線,。這個電路的最大特點就是上下電過程中,,輸出的開啟和關(guān)閉完全由芯片固有的欠壓閾值VUVLO(2.1V)控制,而不受VEN(EN腳的邏輯閾值電壓)控制,。各個時間段特點如表2所示,。上下電過程中輸入電壓越過VUVLO后均有一段輸出跟隨輸入電壓的階段(t1~t2,t3~t4),,該電路比較適合輸入電壓較為穩(wěn)定,且對輸出電壓上下電速度要求不高的場合,。

表2 各段時間電壓特征說明

圖4 直接上拉使能輸入輸出電壓曲線

3. 方式二:電阻分壓使能

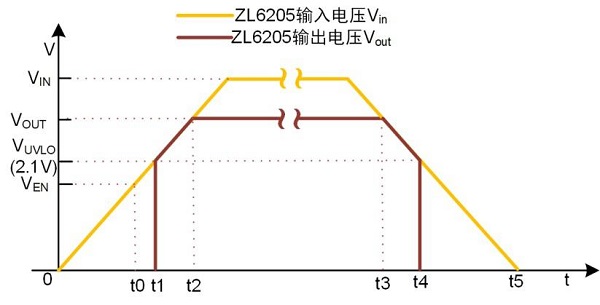

有時候需要VIN上升或者跌落到某一電壓(不小于VUVLO)后,,才允許ZL6205啟動輸出電壓或者關(guān)閉輸出電壓,這樣就需要圖5這樣的使能電路,。根據(jù)圖2可知,,ZL6205在VIN=2.2V~6.5V的輸入電壓范圍內(nèi)的使能電壓閾值VEN=1.2V±0.3V,這樣就可以通過電阻分壓來設(shè)置ZL6205的上電時的啟動電壓(或掉電時的關(guān)閉電壓),。

圖5 電阻分壓使能

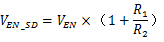

根據(jù)圖5可以得到以下公式,。

VEN_SD:上電過程中期望的開啟電壓點(或者掉電過程中期望的關(guān)閉電壓點),該值需要大于VUVLO(2.1V),,小于VIN,。

VEN:VEN_SD電壓對應(yīng)的器件實際使能閾值(可以根據(jù)圖2得到),要求精度不高時,,可以統(tǒng)一按照1.2V來計算,。

例如,對于常用的3.3V輸出版本的ZL6205來說,,在電源上下電過程中,,希望達到一定的電壓值,例如3.6V,再開啟或者關(guān)閉ZL6205,。那么這個3.6V就是需要設(shè)定的電壓點VEN_SD,。根據(jù)圖2可知,輸入電壓為3.6V對應(yīng)的VEN為1.15V,。代入上面的公式得R1:R2=2.13,, 電阻R1和R2需要滿足這個比例,結(jié)合考慮功耗,,穩(wěn)定性和EN輸入阻抗,,推薦R1=100k,R2 = 47k,。

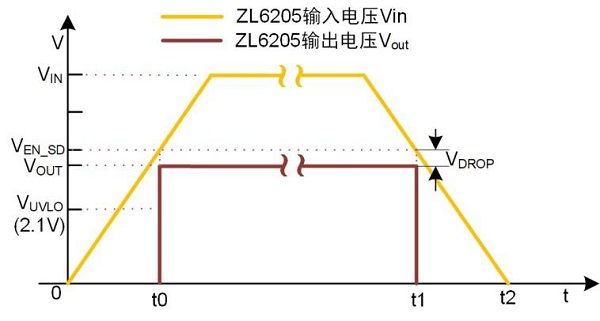

按照上面設(shè)計,,ZL6205上下電會得到圖6這樣的輸入輸出電壓曲線。對于常用的3.3V輸出版本的ZL6205來說,,3.6V的VEN_SD能滿足全負載范圍的壓差VDROP需要,。各個時間段特點如表3所示。這個電路的最大特點就是上下電過程中,,輸出的開啟和關(guān)閉完全由設(shè)定的VEN_SD來控制,,而不受芯片的欠壓閾值VUVLO(2.1V)控制。當(dāng)設(shè)置的VEN_SD大于穩(wěn)態(tài)輸出電壓VOUT時,,上下電過程很快,,看起來幾乎是一步到位,而沒有輸出跟隨輸入電壓的階段,,在輸入電壓低于VEN_SD的階段無論輸入怎么波動都不會影響到輸出,。所以該電路在輸入電壓上下電緩慢且不穩(wěn)定的場合中使用,輸出可以獲得更加快速且穩(wěn)定的上下電效果,。

表3 各段時間電壓特征說明

圖6 電阻分壓使能輸入輸出電壓曲線

4. 其他使能的應(yīng)用

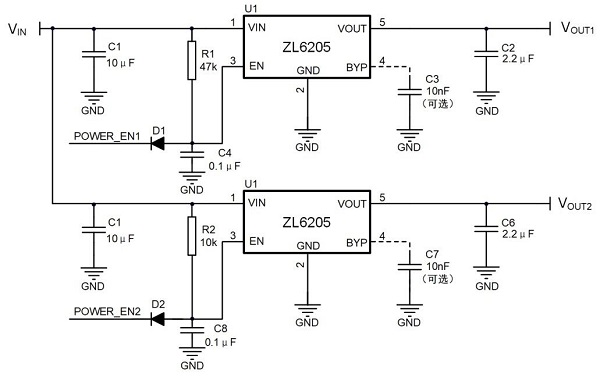

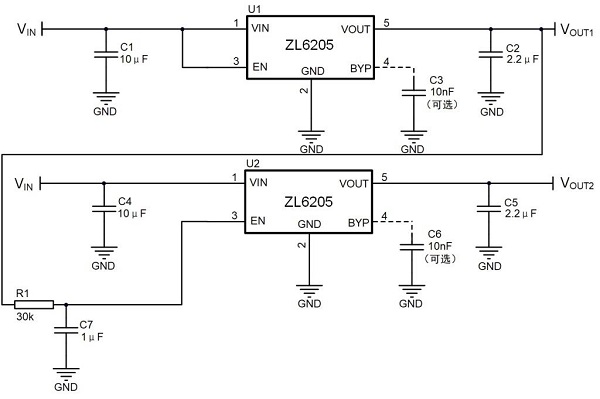

對于電源來說,,利用EN腳控制輸出的方式還有很多。如圖7所示,,該電路可以通過調(diào)整RC參數(shù)(R1和C4,,R2和C8)來調(diào)整輸出上下電時序,也可以通過外部控制信號POWER_EN1和POWER_EN2來控制輸出電壓上下電時序,。圖8則是利用第一路的輸出VOUT1作為輸入信號來控制第二路的輸出VOUT2,。從而實現(xiàn)需要的上電時序,這里由于篇幅限制,,更多的電源的應(yīng)用電路和解決方案可訪問廣州立功科技官網(wǎng),。

圖7 輸出電壓時序應(yīng)用電路一

圖8 輸出電壓時序應(yīng)用電路二