在技術(shù)領(lǐng)域最著名的準(zhǔn)則之一就是摩爾定律。在過(guò)去55年的時(shí)間里,“摩爾定律”已經(jīng)描述并預(yù)測(cè)了晶體管的縮小,如一組稱為技術(shù)節(jié)點(diǎn)的數(shù)字在過(guò)去以大約每?jī)赡暌淮蔚念l率更新。像一些基于物理學(xué)的世界末日時(shí)鐘一樣,幾十年來(lái),節(jié)點(diǎn)數(shù)量一直在不停地下降,因?yàn)楣こ處熢O(shè)法使它們可以容納在同一塊硅片中的晶體管數(shù)量定期增加一倍。

其實(shí)在戈登·摩爾(Gordon Moore) 首次推出以他的名字命名的趨勢(shì)時(shí),業(yè)界并沒(méi)有節(jié)點(diǎn)之類的東西,而且在一個(gè)IC上經(jīng)濟(jì)上只能集成大約50個(gè)晶體管。

但是經(jīng)過(guò)從業(yè)人員數(shù)十年的艱苦努力和數(shù)千億美元的投資,看看我們已經(jīng)走了多遠(yuǎn)!如果您有幸在高端智能手機(jī)上閱讀本文,那么它內(nèi)部的處理器是使用稱為7納米節(jié)點(diǎn)的技術(shù)制造的。這意味著在一平方毫米的硅中大約有1億個(gè)晶體管。在5納米節(jié)點(diǎn)上制造的處理器現(xiàn)已投入生產(chǎn),行業(yè)領(lǐng)導(dǎo)者期望在十年內(nèi)致力于所謂的1納米節(jié)點(diǎn)。

然后呢?

畢竟1 nm已經(jīng)幾乎是五個(gè)硅原子的寬度。因此,也許您會(huì)以為您很快就會(huì)想到摩爾定律將不再存在,半導(dǎo)體制造技術(shù)的發(fā)展將不會(huì)進(jìn)一步提高處理能力,而固態(tài)設(shè)備工程是一條死路一條。

不過(guò)你會(huì)錯(cuò)的。半導(dǎo)體技術(shù)節(jié)點(diǎn)系統(tǒng)繪制的前景圖是錯(cuò)誤的。實(shí)際上,7納米晶體管的大多數(shù)關(guān)鍵特征都比7納米大得多,并且命名和物理現(xiàn)實(shí)之間的脫節(jié)已經(jīng)存在了大約二十年。當(dāng)然,這不是秘密,但這確實(shí)會(huì)帶來(lái)一些不幸的后果。

一是持續(xù)關(guān)注“節(jié)點(diǎn)”的事實(shí)掩蓋了這樣一個(gè)事實(shí),即即使不再需要對(duì)CMOS晶體管的幾何結(jié)構(gòu)進(jìn)行進(jìn)一步的微縮,但半導(dǎo)體技術(shù)實(shí)際上仍將有可能繼續(xù)推動(dòng)計(jì)算向前發(fā)展;另一個(gè)問(wèn)題是,以節(jié)點(diǎn)為中心的半導(dǎo)體發(fā)展觀未能以過(guò)去的產(chǎn)業(yè)振興方式指出前進(jìn)的方向。最后,令人討厭的是,這么多的庫(kù)存投入到根本上毫無(wú)意義的數(shù)字中。

尋找更好的方法來(lái)標(biāo)記行業(yè)里程碑的努力開(kāi)始產(chǎn)生明顯更好的替代方法。但是,在一個(gè)聲名狼藉的競(jìng)爭(zhēng)性行業(yè)中,專家是否會(huì)團(tuán)結(jié)其中之一是個(gè)問(wèn)題?讓我們希望他們這樣做,這樣我們就可以再次擁有一種有效的方法來(lái)衡量世界上最大,最重要,最有活力的行業(yè)之一的進(jìn)步。

那么,我們將如何到達(dá)一個(gè)可以說(shuō)是過(guò)去一百年中最重要的技術(shù)發(fā)展錯(cuò)誤地出現(xiàn)了自然終點(diǎn)的地方?自1971年發(fā)布Intel 4004微處理器那年起,MOS晶體管的線性尺寸縮小了約1,000倍,單個(gè)芯片上的晶體管數(shù)量增加了約1500萬(wàn)倍。用來(lái)衡量集成密度這種驚人進(jìn)步的度量標(biāo)準(zhǔn)主要是尺寸,稱為金屬半節(jié)距(Metal half-pitch)和柵極長(zhǎng)度(gate length)。這在一開(kāi)始很方便,因?yàn)楹荛L(zhǎng)一段時(shí)間里,它們的數(shù)字幾乎相同。

金屬半節(jié)距是芯片上從一個(gè)金屬互連的起點(diǎn)到下一個(gè)金屬互連的起點(diǎn)的一半距離。在直到十年前一直占據(jù)主導(dǎo)地位的二維或“平面”晶體管設(shè)計(jì)中,柵極長(zhǎng)度測(cè)量的是晶體管源極和漏極之間的空間。器件的柵極疊層位于該空間中,該柵極疊層控制著源極和漏極之間的電子流動(dòng)。從歷史上看,它是決定晶體管性能的最重要尺寸,因?yàn)檩^短的柵極長(zhǎng)度表明開(kāi)關(guān)器件的速度更快。

在柵極長(zhǎng)度和金屬半節(jié)距大致相等的時(shí)代,它們代表了芯片制造技術(shù)的基本特征,成為節(jié)點(diǎn)數(shù)。芯片上的這些功能通常每代縮小30%。這樣的減小使晶體管密度加倍,因?yàn)閷⒕匦蔚膞和y尺寸都減小30%意味著面積減半。

在整個(gè)19世紀(jì)70年代和80年代,使用柵極的長(zhǎng)度和半節(jié)距作為節(jié)點(diǎn)一直達(dá)到其目的,但是在1990年代中期,這兩個(gè)功能開(kāi)始脫鉤。為了繼續(xù)在速度和設(shè)備效率上取得歷史性的進(jìn)步,芯片制造商比設(shè)備的其他功能更積極地縮短了柵極的長(zhǎng)度。例如,使用所謂的130 nm節(jié)點(diǎn)制造的晶體管實(shí)際上具有70 nm的柵極。結(jié)果是摩爾定律密度加倍路徑的延續(xù),但柵極長(zhǎng)度不成比例地縮小。然而,在大多數(shù)情況下,行業(yè)仍然遵循舊的節(jié)點(diǎn)命名約定的節(jié)奏。

無(wú)意義的技術(shù)節(jié)點(diǎn)

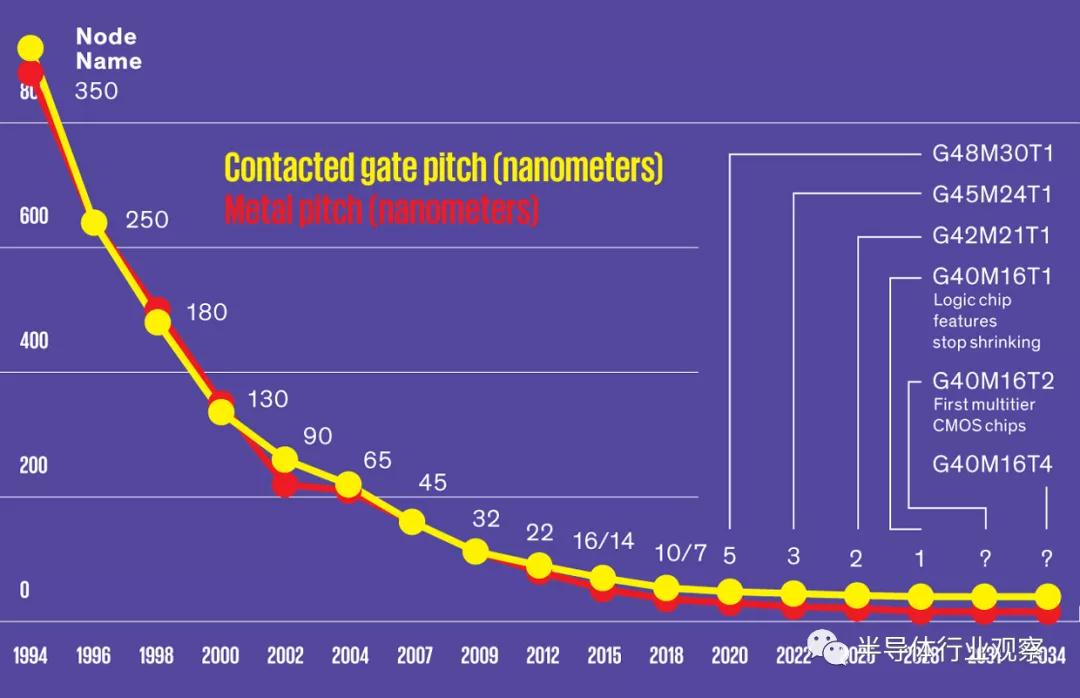

在19實(shí)際90年代中期之前,邏輯技術(shù)節(jié)點(diǎn)與其制造的CMOS晶體管的柵極長(zhǎng)度同義。實(shí)際的柵極長(zhǎng)度縮短了一會(huì)兒,然后停止微縮。

GMT方法

光刻技術(shù)的局限性:最先進(jìn)的光刻技術(shù),即極端紫外光刻技術(shù),依賴于13.5納米波長(zhǎng)的光。這意味著芯片功能將很快停止微縮。芯片制造商將不得不轉(zhuǎn)向單片3D集成,增加設(shè)備層次,以保持硅CMOS的密度增加。GMT方法通過(guò)說(shuō)明兩個(gè)最關(guān)鍵的特征(接觸的柵極節(jié)距和金屬節(jié)距)的大小以及層數(shù)來(lái)對(duì)此進(jìn)行跟蹤。

21世紀(jì)初的發(fā)展使事情變得更遙遠(yuǎn),因?yàn)樘幚砥饕朔牡南拗啤9こ處焸冋业搅吮3衷O(shè)備改進(jìn)的方法。例如,將晶體管的一部分硅置于源極(strain )下,可使電荷載流子在較低的電壓下更快地通過(guò),從而提高了CMOS器件的速度和功率效率,而又不使柵極長(zhǎng)度變得更短。

由于電流泄漏問(wèn)題需要對(duì)CMOS晶體管進(jìn)行結(jié)構(gòu)更改,因此事情變得更加陌生。2011年,當(dāng)英特爾在22納米節(jié)點(diǎn)上切換到FinFET時(shí),這些設(shè)備的柵極長(zhǎng)度為26納米,半間距為40納米,鰭片為8納米。

IEEE終身研究員和英特爾資深人士Paolo Gargini說(shuō),該行業(yè)的節(jié)點(diǎn)到那時(shí)絕對(duì)沒(méi)有意義,因?yàn)樗c您可以在芯片上找到的與實(shí)際工作相關(guān)的任何尺寸都沒(méi)有關(guān)系“。誰(shuí)領(lǐng)導(dǎo)著新的度量標(biāo)準(zhǔn)工作之一。

盡管半導(dǎo)體行業(yè)需要更好的東西,但已達(dá)成廣泛共識(shí),盡管不是普遍的。一種解決方案是簡(jiǎn)單地將術(shù)語(yǔ)與對(duì)晶體管重要的實(shí)際特征的大小重新對(duì)齊。這并不意味著要回到柵極長(zhǎng)度,后者不再是最重要的功能。

相反,建議使用兩種方法來(lái)表示制造邏輯晶體管所需面積的實(shí)際限制。一種稱為接觸柵間距。此短語(yǔ)是指從一個(gè)晶體管的柵極到另一個(gè)晶體管的柵極的最小距離。另一個(gè)重要指標(biāo)金屬間距測(cè)量?jī)蓚€(gè)水平互連之間的最小距離。(由于柵極長(zhǎng)度現(xiàn)在已不再重要,因此不再有任何理由將金屬間距分成兩半。)

Arm首席研究工程師Brian Cline解釋說(shuō),這兩個(gè)值是在新流程節(jié)點(diǎn)中創(chuàng)建邏輯的”最小公分母“。這兩個(gè)值的乘積很好地估計(jì)了晶體管的最小可能面積。其他每個(gè)設(shè)計(jì)步驟(形成邏輯或SRAM單元,電路塊)都增加了最低限度。他說(shuō):”具有深思熟慮的物理設(shè)計(jì)特征的良好邏輯過(guò)程將使該值的降級(jí)最小“。

IEEE國(guó)際設(shè)備和系統(tǒng)路線圖(IRDS)主席Gargini 在四月份提出,該行業(yè)采用結(jié)合接觸式柵極節(jié)距(G),金屬節(jié)距(M)的三位數(shù)指標(biāo)來(lái)”回歸現(xiàn)實(shí)“。,對(duì)于未來(lái)的芯片來(lái)說(shuō),至關(guān)重要的是,芯片上的設(shè)備的層數(shù)或?qū)訑?shù)(T)。(IRDS是”國(guó)際半導(dǎo)體技術(shù)路線圖“(ITRS)的繼承者,ITRS是一項(xiàng)現(xiàn)已失效,數(shù)十年之久的全行業(yè)研究,旨在預(yù)測(cè)未來(lái)節(jié)點(diǎn)的各個(gè)方面,從而使該行業(yè)及其供應(yīng)商有一個(gè)統(tǒng)一的目標(biāo)。)

”這三個(gè)參數(shù)是評(píng)估晶體管密度所需的全部知識(shí),“ ITRS的負(fù)責(zé)人Gargini說(shuō)。

IRDS路線圖顯示,即將推出的5nm芯片的接觸柵距為48nm,金屬柵距為36nm,并且具有單層結(jié)構(gòu),即公制G48M36T1。它并不能完全解決問(wèn)題,但是它確實(shí)傳達(dá)了比” 5-nm節(jié)點(diǎn)“有用的信息。

與節(jié)點(diǎn)命名法一樣,此GMT指標(biāo)的柵極間距和金屬間距值在整個(gè)十年中將繼續(xù)減小。但是,它們的運(yùn)行速度將越來(lái)越慢,以目前的速度,到現(xiàn)在大約10年后才能達(dá)到終點(diǎn)。到那時(shí),金屬間距將接近極限紫外光刻可以解決的極限。盡管上一代光刻機(jī)能夠經(jīng)濟(jì)高效地克服其193 nm波長(zhǎng)的可感知極限,但沒(méi)有人期望極端紫外線會(huì)發(fā)生同樣的事情。

Gargini說(shuō):”到2029年左右,我們達(dá)到了光刻技術(shù)的極限。“ 之后,”前進(jìn)的方向是堆疊……這是增加密度的唯一途徑。“

屆時(shí),層數(shù)(T)項(xiàng)將變得非常重要。當(dāng)今先進(jìn)的硅CMOS是單層晶體管,通過(guò)十多個(gè)金屬互連層將它們鏈接到電路中。但是,如果您可以構(gòu)建兩層晶體管,則可能使器件的密度幾乎翻倍。

對(duì)于硅CMOS,目前仍在實(shí)驗(yàn)室中,但是時(shí)間不長(zhǎng)。十多年來(lái),工業(yè)研究人員一直在探索生產(chǎn)” 單片式3D IC “的方法,這些芯片中一層又一層地堆疊著晶體管。這并非易事,因?yàn)楣杓庸囟韧ǔ:芨撸灾劣诮ㄔ煲粚訒?huì)損壞另一層。盡管如此,一些工業(yè)研究工作(尤其是比利時(shí)納米技術(shù)研究公司Imec,法國(guó)的CEA-Leti和Intel正在開(kāi)發(fā)可以在CMOS邏輯中構(gòu)建兩種類型晶體管的技術(shù)-NMOS和PMOS-一種在另一種之上。

即將出現(xiàn)的非硅技術(shù)甚至可以更快地進(jìn)入3D。例如,麻省理工學(xué)院教授馬克斯·舒拉克(Max Shulaker)和他的同事們參與了依賴于碳納米管晶體管層的3D芯片的開(kāi)發(fā)。因?yàn)槟梢栽谙鄬?duì)較低的溫度下處理這些設(shè)備,所以與使用硅設(shè)備相比,可以更輕松地將它們構(gòu)建為多層。

其他公司正在研究可以在硅上方的金屬互連層內(nèi)構(gòu)建的邏輯或存儲(chǔ)設(shè)備。其中包括由原子稀薄的半導(dǎo)體(如二硫化鎢)制成的微機(jī)械繼電器和晶體管。

大約一年前,一群著名的學(xué)者聚集在加州大學(xué)伯克利分校的校園中,提出了自己的標(biāo)準(zhǔn)。

這種專家的組合尋求一種指標(biāo),該指標(biāo)可以消除節(jié)點(diǎn)的世界末日時(shí)鐘氛圍。他們決定,至關(guān)重要的是,該指標(biāo)不應(yīng)有自然終點(diǎn)。換句話說(shuō),數(shù)字應(yīng)該隨著進(jìn)步而上升而不是下降。它還必須簡(jiǎn)單,準(zhǔn)確,并且與改進(jìn)半導(dǎo)體技術(shù)的主要目的(功能更強(qiáng)大的計(jì)算系統(tǒng))相關(guān)。

為此,他們需要做的事情不僅僅是IRDS的GMT指標(biāo)所能描述的,用于制造處理器的技術(shù)。他們想要一個(gè)不僅考慮處理器而且還考慮整個(gè)計(jì)算機(jī)系統(tǒng)其他影響性能的關(guān)鍵因素的度量標(biāo)準(zhǔn)。這可能看起來(lái)過(guò)于雄心勃勃,也許是這樣,但是隨著方向計(jì)算的開(kāi)始,它顯得格外刺眼。

破解Intel Stratix 10現(xiàn)場(chǎng)可編程門陣列的封裝,您將發(fā)現(xiàn)的不僅僅是FPGA處理器。在封裝內(nèi)部,處理器芯片被一系列” 小芯片“ 包圍,其中包括兩個(gè)高帶寬DRAM芯片。用密集的互連陣列蝕刻的一小片硅片將處理器連接到內(nèi)存。

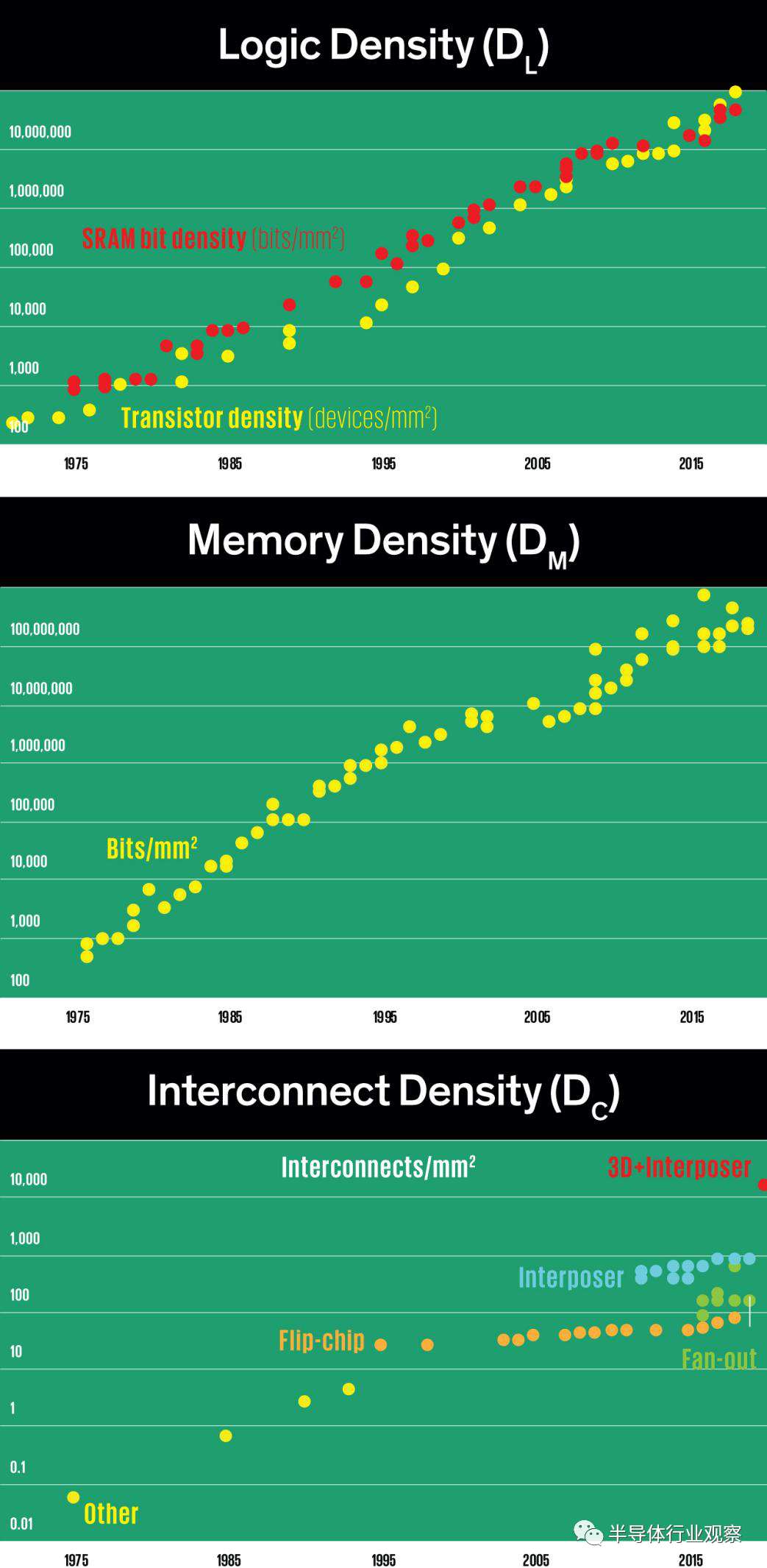

一臺(tái)計(jì)算機(jī)最基本的就是:邏輯,內(nèi)存以及它們之間的連接。因此,要拿出自己的新的指標(biāo),為此該小組選擇的參數(shù)是DL, DM, 和 DC。這就是LMC度量。

根據(jù)LMC指標(biāo)的發(fā)起者,在當(dāng)今以數(shù)據(jù)為中心的時(shí)代,D L,D M和D C的改進(jìn)共同為計(jì)算系統(tǒng)的整體速度和能源效率做出了重要貢獻(xiàn)。他們繪制了歷史數(shù)據(jù),顯示了邏輯,內(nèi)存和連接性增長(zhǎng)之間的相關(guān)性,這表明D L,D M和D C的均衡增長(zhǎng)已經(jīng)持續(xù)了數(shù)十年。這種平衡在計(jì)算機(jī)體系結(jié)構(gòu)中是隱含的他們認(rèn)為,令人驚訝的是,它適用于各種復(fù)雜程度的計(jì)算系統(tǒng),從移動(dòng)和臺(tái)式機(jī)處理器一直到世界上最快的超級(jí)計(jì)算機(jī)。小組成員說(shuō),這種均衡的增長(zhǎng)表明未來(lái)將需要類似的改進(jìn)。

LMC方法

稱為L(zhǎng)MC的節(jié)點(diǎn)度量標(biāo)準(zhǔn)的替代方法通過(guò)說(shuō)明邏輯密度(D L),主存儲(chǔ)器的密度(D M)以及鏈接它們的互連的密度(D C)來(lái)獲取技術(shù)的價(jià)值。

在LMC度量標(biāo)準(zhǔn)中, D L是邏輯晶體管的密度,以每平方毫米的cell數(shù)量表示。D M是每平方毫米內(nèi)存中系統(tǒng)主內(nèi)存的密度。D C是邏輯與主存儲(chǔ)器之間的連接,以每平方毫米的互連數(shù)表示。如果存在多層設(shè)備或3D芯片堆疊,則超過(guò)該平方毫米的整個(gè)體積都非常重要。

D L可能是三者中歷史上最熟悉的一種,因?yàn)樽詮牡谝慌鶬C以來(lái)人們一直在計(jì)算芯片上的晶體管數(shù)量。雖然聽(tīng)起來(lái)很簡(jiǎn)單,但事實(shí)并非如此。處理器上不同類型的電路在密度上有所不同,這在很大程度上是由于鏈接設(shè)備的互連。邏輯芯片中最密集的部分通常是構(gòu)成處理器高速緩存的SRAM存儲(chǔ)器,數(shù)據(jù)被存儲(chǔ)在其中以便快速重復(fù)訪問(wèn)。這些高速緩存是六晶體管單元的大型陣列,可以將它們緊密封裝在一起,部分原因是其規(guī)則性。通過(guò)這種測(cè)量,迄今為止報(bào)告的D L的最大值是使用TSMC 5納米工藝制造的135兆位SRAM陣列,每平方毫米封裝了2.86億個(gè)晶體管。在建議的命名法中,該名稱應(yīng)為286M。

但是,邏輯塊比嵌入其中的SRAM更復(fù)雜,更不統(tǒng)一且密度更低。因此,僅根據(jù)SRAM判斷技術(shù)可能并不公平。2017年,當(dāng)時(shí)的英特爾高級(jí)研究員Mark Bohr提出了一種使用某些常見(jiàn)邏輯單元的加權(quán)密度的公式。該公式著眼于一個(gè)簡(jiǎn)單且普遍存在的兩輸入,四晶體管與非門以及一個(gè)常見(jiàn)但更復(fù)雜的電路(稱為掃描觸發(fā)器)的單位面積晶體管數(shù)。在典型設(shè)計(jì)中,它根據(jù)此類小柵極和大單元的比例對(duì)每個(gè)元素加權(quán),以產(chǎn)生每平方毫米單個(gè)晶體管的結(jié)果。Bohr當(dāng)時(shí)說(shuō)SRAM的密度如此之大,應(yīng)單獨(dú)測(cè)量。

據(jù)AMD高級(jí)研究員Kevin Gillespie稱,AMD在內(nèi)部使用類似的東西。他說(shuō),如果一個(gè)度量標(biāo)準(zhǔn)不考慮設(shè)備的連接方式,那將是不準(zhǔn)確的。

由幾位專家分別提出的另一種可能性是,在經(jīng)過(guò)商定的,大面積的半導(dǎo)體知識(shí)產(chǎn)權(quán)中,例如在Arm廣泛使用的處理器設(shè)計(jì)中,測(cè)量平均密度。

實(shí)際上,根據(jù)Arm的Cline的說(shuō)法,Arm放棄了單一指標(biāo)的嘗試,而是希望從完整的處理器設(shè)計(jì)中提取電路功能塊的密度。他說(shuō):”我認(rèn)為對(duì)于所有硬件應(yīng)用來(lái)說(shuō),沒(méi)有一個(gè)適合所有人的邏輯密度指標(biāo)“,因?yàn)椴煌愋偷男酒拖到y(tǒng)的差異太大。他指出,不同類型的處理器(CPU,GPU,神經(jīng)網(wǎng)絡(luò)處理器,數(shù)字信號(hào)處理器)具有不同的邏輯和SRAM比率。

最后,LMC發(fā)起者選擇不指定特定的D L測(cè)量方法,而將其留給業(yè)界討論。

測(cè)量D M更加簡(jiǎn)單。目前,主存儲(chǔ)器通常是指DRAM,因?yàn)樗鼉r(jià)格便宜,耐用性高并且讀寫速度相對(duì)較快。

DRAM單元由一個(gè)晶體管控制,該晶體管控制對(duì)將位存儲(chǔ)為電荷的電容器的訪問(wèn)。由于電荷會(huì)隨時(shí)間泄漏,因此必須定期刷新cell。如今,電容器是建立在硅上方的互連層中的,因此密度不僅受晶體管尺寸的影響,還受互連幾何形狀的影響。LMC集團(tuán)在已發(fā)表的文獻(xiàn)中可以找到的最高D M值來(lái)自三星。在2018年,該公司詳細(xì)介紹了DRAM技術(shù),密度為每平方毫米(200M)2億個(gè)單元。

DRAM可能并不總是保持其作為主存儲(chǔ)器的位置。當(dāng)今,諸如磁阻RAM,鐵電RAM,電阻性RAM和相變RAM之類的替代存儲(chǔ)技術(shù)已投入商業(yè)生產(chǎn),其中一些作為嵌入處理器本身的存儲(chǔ)器,另一些作為獨(dú)立芯片。

在主內(nèi)存和邏輯之間提供足夠的連接已經(jīng)是當(dāng)今計(jì)算系統(tǒng)的主要瓶頸。D C衡量的處理器和內(nèi)存之間的互連歷史上是由封裝級(jí)技術(shù)而非芯片制造技術(shù)創(chuàng)建的。與邏輯密度和存儲(chǔ)器密度相比,DC已經(jīng)在過(guò)去幾十年穩(wěn)步少得多的改善。取而代之的是,隨著新封裝技術(shù)的引入和改進(jìn),出現(xiàn)了離散的跳躍。在過(guò)去的十年中,尤其是多事之秋,因?yàn)閱涡酒瑔纹到y(tǒng)(SoC)已讓位給在硅中介層上緊密結(jié)合在一起的小芯片(所謂的2.5D系統(tǒng))或堆疊成3D排列的小芯片。使用臺(tái)積電集成芯片系統(tǒng)的系統(tǒng)3D芯片堆疊技術(shù)具有最高的DC,在每平方毫米(12K)12000個(gè)互連。

但是,DC不一定需要將邏輯連接到單獨(dú)的存儲(chǔ)芯片。對(duì)于某些系統(tǒng),主存儲(chǔ)器是完全嵌入式的。例如,Cerebras Systems的機(jī)器學(xué)習(xí)大型芯片完全依賴于嵌入在單個(gè)大規(guī)模硅片上的邏輯核附近的SRAM。

LMC發(fā)起者建議,將描述一個(gè)將所有三個(gè)參數(shù)(D L,D M和D C)中最好的一個(gè)組合的系統(tǒng)[260M,200M,12K]。

英特爾首席技術(shù)官邁克爾·梅伯里(Michael Mayberry)認(rèn)為,用一個(gè)數(shù)字來(lái)描述半導(dǎo)體節(jié)點(diǎn)的先進(jìn)性已經(jīng)過(guò)去了很長(zhǎng)時(shí)間。但是,他原則上喜歡具有全面的系統(tǒng)級(jí)度量的想法。他說(shuō):”即使是不完美的,也可以選擇達(dá)成共識(shí)的東西,而不是當(dāng)前的節(jié)點(diǎn)品牌。“

他希望看到LMC擴(kuò)展了更多詳細(xì)級(jí)別,以指定要測(cè)量的內(nèi)容和方式。例如,關(guān)于D M值,Mayberry說(shuō),它可能需要專門與與其所服務(wù)的處理器位于同一芯片封裝內(nèi)的存儲(chǔ)器相關(guān)。他補(bǔ)充說(shuō),歸類為”主內(nèi)存“的內(nèi)容可能也需要進(jìn)行微調(diào)。將來(lái),處理器和數(shù)據(jù)存儲(chǔ)設(shè)備之間可能會(huì)有多層存儲(chǔ)。例如,英特爾和美光制造的3D XPoint內(nèi)存是一種非易失性系統(tǒng),在DRAM和存儲(chǔ)之間占據(jù)一席之地。

進(jìn)一步的批評(píng)是,基于密度的度量標(biāo)準(zhǔn)(如LMC)和基于光刻的度量標(biāo)準(zhǔn)(如GMT)均與代工廠和存儲(chǔ)芯片制造商的客戶所要求的相距甚遠(yuǎn)。AMD的Gillespie說(shuō):”有[密度]區(qū)域,但也有性能,功能和成本。“ Mayberry補(bǔ)充說(shuō),每種芯片設(shè)計(jì)都圍繞這四個(gè)軸進(jìn)行權(quán)衡,以至于”沒(méi)有一個(gè)單一的數(shù)字可以反映出節(jié)點(diǎn)的性能如何“。

”排名第三的內(nèi)存和存儲(chǔ)最重要的指標(biāo)仍然是單位成本,“ 全球第三大DRAM制造商美光科技公司高級(jí)研究員兼副總裁Gurtej Singh Sandhu說(shuō)。”還密切考慮了其他幾個(gè)因素,包括基于特定市場(chǎng)應(yīng)用的各種性能指標(biāo)。“

還有一個(gè)派別認(rèn)為,此時(shí)甚至不需要新的指標(biāo)。GlobalFoundries負(fù)責(zé)工程和質(zhì)量的高級(jí)副總裁Gregg Bartlett說(shuō),這些措施”實(shí)際上僅在以縮放為主導(dǎo)的應(yīng)用中才有用“ ,該公司于2018年結(jié)束了對(duì)7納米工藝的追求。這個(gè)空間以及有限的客戶和應(yīng)用程序數(shù)量,因此與絕大多數(shù)半導(dǎo)體行業(yè)的關(guān)系不大。” 僅剩下英特爾,三星和臺(tái)積電追求最后幾個(gè)CMOS邏輯節(jié)點(diǎn),但它們幾乎沒(méi)有參與其中,在全球半導(dǎo)體制造收入中占了很大一部分。

Bartlett的公司不在該小組中,他認(rèn)為CMOS邏輯與專用技術(shù)(例如嵌入式非易失性存儲(chǔ)器和毫米波無(wú)線電)的集成對(duì)行業(yè)的未來(lái)至關(guān)重要,而不是擴(kuò)展規(guī)模。

但是,毫無(wú)疑問(wèn),持續(xù)擴(kuò)展對(duì)許多半導(dǎo)體消費(fèi)者而言很重要。盡管出于不同的原因,LMC指標(biāo)和GMT指標(biāo)的創(chuàng)建者都感到緊迫感。對(duì)于LMC支持者來(lái)說(shuō),在晶體管縮放的重要性不高的時(shí)代,業(yè)界需要明確其長(zhǎng)期發(fā)展前景,以便他們能夠招募技術(shù)人才來(lái)實(shí)現(xiàn)這一未來(lái)。

對(duì)于Gargini和GMT支持者而言,這是為了使整個(gè)行業(yè)步入正軌。他認(rèn)為,如果沒(méi)有指標(biāo)的同步,該行業(yè)的效率就會(huì)降低。他說(shuō):“這增加了失敗的可能性。” “我們有10年的時(shí)間”,直到硅CMOS完全停止收縮。“僅勉強(qiáng)夠用”以產(chǎn)生將使計(jì)算不斷發(fā)展的必要突破。