SoC市場迎來了新變局

然而,隨著AI技術在安防、自動駕駛、醫(yī)療等應用中正漸入佳境,這些新興應用使得數據正以前所未有的速度增長。這就意味著需要更多的計算能力和更多的帶寬來處理所有數據。數據速率提高和功能日趨復雜致使相關SoC大小與日俱增,SoC開始接近占滿光罩(reticle)尺寸。

ODSA工作組曾在一份報告中指出,隨著先進技術向越來越精細的功能轉移,實現芯片制造的成本正在急劇上升。對于許多市場來說,這種額外的成本是不可接受的。為了攤薄成本,設計人員通常在舊的工藝節(jié)點上構造非常大的單裸片。

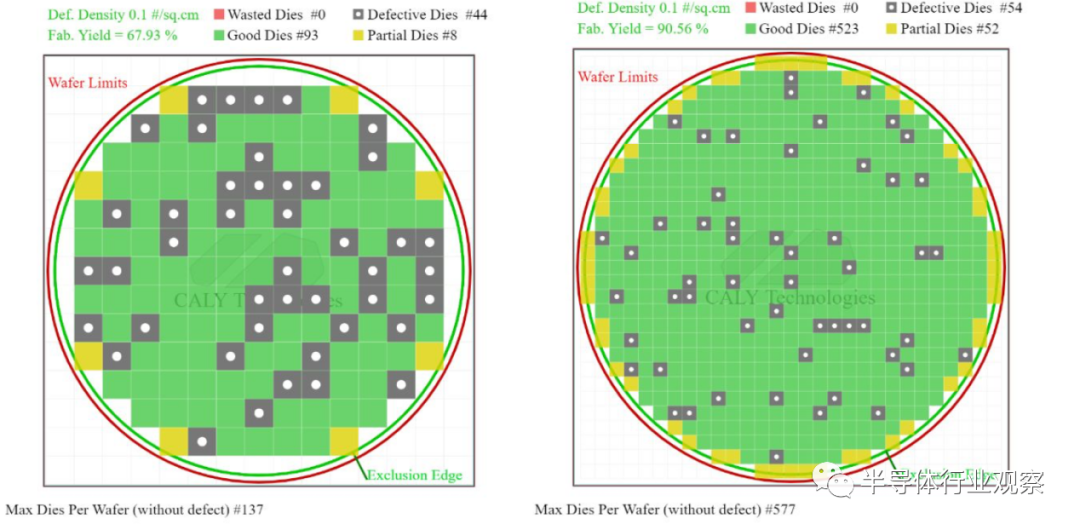

但大型裸片會帶來芯片制造良率降低的問題,ODSA工作組表示,大型裸片具有一定的缺陷,下圖比較了兩個裸片,一個10x10,另一個是20x20。只要使用非常好的d0(0.1),每300毫米晶圓的中,四個10x10裸片良率會比20x20裸片多29%。

裸片尺寸對良率的影響 來源:ODSA工作組

反過來,對更快的處理器以及利用較小的節(jié)點(例如7nm)好處的能力的需求也在增長。但眾所周知,每個節(jié)點的芯片制造和設計成本都會增加。根據相關資料指出,如果使用7nm節(jié)點,那么掩模的成本可能高達1000萬美元左右,更遑論流片等過程需要支出的巨額費用。

來源:AMD

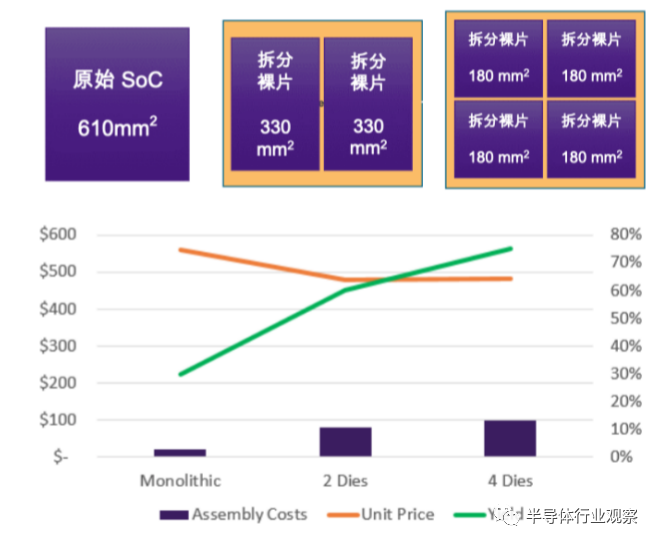

在芯片制造良率受到影響且先進制程投入費用愈發(fā)昂貴的雙重背景下,SoC的設計模式發(fā)生了巨大變化。設計人員將SoC分成較小的裸片,這些裸片封裝在多芯片模塊 (MCM) 中,以實現高產量并降低總體成本。

新思科技IP營銷副總裁John Koeter也曾表示:“用于高端數據中心和網絡應用的高級SoC達到了最大光罩限制,要求設計人員將SoC劃分為較小的模塊化芯片。”

實際上這種方法并不新鮮,在1965年《電子學》文章中,戈登·摩爾(Gordon Moore)介紹摩爾定律時曾說,利用較小的功能(分別封裝和互連)構建大型系統(tǒng)可能被證明更經濟。

來源:新思科技

對于這些被分割的裸片來說,互連至關重要。Die-to-die的互連將一個裸片與另一個裸片封裝在一起,每個裸片都包含一個帶有物理接口的IP模塊,具有公共接口的一個裸片可以通過短距離導線與另一個裸片進行通信。

die-to-die連接的市場趨勢

目前die-to-die連接呈現出兩種融合趨勢,分別稱為同質裸片和異質裸片。

同質裸片主要進行的是裸片拆分工作。為了滿足不同的應用、場景需求,現在芯片設計規(guī)模越來越大。

同質裸片將接近光罩大小的大規(guī)模SoC進行拆分,這樣以后,就能如前文所言,提高良率、降低裸片成本。同時還能夠增加可拓展性,延長摩爾定律有效性。

異質裸片主要進行封裝集成的工作,將不同功能集成到統(tǒng)一封裝。比如模擬模塊等,其需要相對較低的性能,但采用相對高的節(jié)點,將不同的工藝下結合到同一個封裝里,可以節(jié)省成本。

同時把現有設計放到SoC中,也能降低風險,因為成熟的設計風險更低,根據不同產品去采取不同的方案,通過die-to-die連接,可以有效控制產品上市時間和風險。

在MCM中die-to-die連接的新用例在不斷涌現,其中包括:接近最大光罩尺寸的高性能計算和服務器SoC、超過最大光罩尺寸的以太網交換機和網絡 SoC以及可擴展復雜算法的具有分布式SRAM 的AI SoC等。

就高性能計算和服務器 SoC來說,其尺寸越來越大,目前已達到 550 mm2至 800 mm2,這降低了 SoC 的良率并提高了單位芯片成本。解決這種問題的方法就是將 SoC 分為兩個或多個等效的同質芯片,并使用 die-to-die PHY IP 連接芯片。新思科技指出,在這種用例中,主要的要求是極低的延遲和零誤碼率,因為更小的多個芯片的表現和行為必須像單一芯片一樣。

需要die-to-die連接的高性能計算和服務器 SoC 的示例 來源:新思科技

需要die-to-die連接的高性能計算和服務器 SoC 的示例 來源:新思科技

還有AI SoC ,每個芯片都包含智能處理單元 (IPU) 和位于每個 IPU 附近的分布式 SRAM。在這種使用情況下,一個芯片中的 IPU 可能需要依賴于極低延遲的短距離 die-to-die 鏈路來訪問另一個芯片的 SRAM 中的數據。

需要 die-to-die 連接的 AI SoC 示例 來源:新思科技

需要 die-to-die 連接的 AI SoC 示例 來源:新思科技

這些SoC 中的die-to-die互連必須不影響整體系統(tǒng)性能,同時要求低延遲、低功耗和高吞吐量。不僅如此,SoC應用程序具有快速變化的要求,必須通過互連快速解決這些要求。

許多公司開發(fā)了具有專有接口的互連,這意味著它們只可用于公司自己的設備。但是,為了擴大采用范圍,行業(yè)需要使用開放接口進行互連,以使不同的芯片能夠相互通信。

EETimes在一篇文章中指出,曾有一家芯片公司每年僅開發(fā)四個SoC,因為用他們一個多月的時間使用其內部開發(fā)的互連IP在由其內部總線組創(chuàng)建的互連實例中實現任何更改。若采用商業(yè)互連IP,他們便能夠將其芯片產量增加到每年20多個設計,這使他們能夠經濟地交付按市場細分量身定制的芯片,以高毛利率和可接受的價格為客戶贏得更多的設計大獎。

并且EETimes表示,即使內部團隊十年來一直專門為客戶創(chuàng)建“優(yōu)化的”互連,但新的商業(yè)IP解決方案在各個方面都優(yōu)于他們,與內部開發(fā)的互連相比,最終每個芯片平均節(jié)省了3平方毫米的裸片面積。每個芯片可節(jié)省約30美分,總體可省大約數百萬美元。

因此商業(yè) die-to-die互連對于芯片公司來說是更加經濟的選擇。新思科技致力于提供高質量IP解決方案。

如何選擇die-to-die PHY IP?

新思科技表示,在研究用于 MCM 的 die-to-die 連接的高速 PHY IP 解決方案時,SoC 設計人員必須考慮幾個基本功能,包括以千兆位或兆兆位每秒(Gbps 或 Tbps)衡量的數據吞吐量或帶寬、以每比特皮焦耳 (pJ/bit) 衡量的能源效率、以納秒 (ns) 衡量的延遲、以毫米 (mm) 衡量的最大鏈路范圍,以及誤碼率(無單位)。

不僅如此,為了實現與其他收發(fā)器的互操作,die-to-die PHY IP 必須確保符合 USR 和 XSR 鏈路的相關 光學互聯網絡論壇(OIF)電氣規(guī)范。

在 die-to-die 的實現中,大量數據必須流經橋接芯片之間間隙的短數據路徑。為了保證將芯片放置在封裝基板上時的最大靈活性,PHY IP 必須支持 TX 和 RX 之間 50 毫米的最長距離。

能效成為重要的因素,尤其是在將 SoC 功能劃分為多個同質芯片的用例中。設計人員正在尋求在不影響 SoC 總功耗預算的情況下,在芯片之間推送大量數據的方法。理想的 die-to-die PHY IP 的能效好于每比特 1 皮焦耳 (1pJ/bit) 或同等的 1mW/Gbps。

為了使芯片之間的連接“透明”,延遲必須維持得極低,同時必須優(yōu)化誤碼率 (BER)。由于簡化了架構,die-to-die PHY IP 本身實現了超低延遲,BER 優(yōu)于 10e-15。

除了這些與性能相關的參數外,PHY IP 還必須支持所有側面的放置芯片,以實現芯片以及 MCM 的有效布局。

選擇 die-to-die PHY IP 時,還有許多其他考慮因素,包括納入可測試性功能,以便能夠在封裝之前對芯片進行生產測試等。這些要求推動了對高吞吐量 die-to-die PHY 的需求。

新思科技的 DesignWare USR/XSR PHY IP出現的非常及時,該IP核支持從2.5G到112G數據速率的NRZ和PAM-4信令,為大型MCM設計提供最大的每芯片邊緣吞吐量。為了提高片上系統(tǒng)(SoC)產量,Die-to-Die PHY允許將大型芯片分割成較小的芯片,同時為功率、單位IO寬度、延遲或傳輸距離的帶寬提供了權衡。

此外,為了加快產品開發(fā)周期,Synopsys的IP加速計劃提供了SoC架構設計支持,IP子系統(tǒng)以及全面的芯片啟動支持。

總結

當下,一眾廠商如新思科技的die-to-die 方案被廣泛使用在高性能計算應用中,展望未來,die-to-die方案將在AI加速,5G通信和自動駕駛汽車等場景廣泛應用。

特別是自動駕駛將對集成技術提出更高的要求:電路之間的數據傳輸速率必須非常高,這是因為要處理的攝像機圖像和雷達或LiDAR數據量很大,因此需要在電路之間定期進行交換。

目前,根據業(yè)內人士透露,已經有應用市場開始把die-to-die 的方案使用在汽車市場當中,相信未來會出現更多可能。

應用需求不斷提升正在加速片上die-to-die 方案的創(chuàng)新,其重要性也在呈爆炸式增長。