據(jù)《韓國(guó)經(jīng)濟(jì)》雜志報(bào)道,三星電子已成功研發(fā)出首款3nm工藝芯片,基于全柵極(GAAFET)技術(shù)。與三星使用FinFET工藝研發(fā)的5nm芯片相比,3nm芯片的總硅片面積減少35%,功耗降低50%,性能提高30%

據(jù)悉,韓國(guó)當(dāng)?shù)貢r(shí)間1月2日,三星電子事實(shí)上的領(lǐng)導(dǎo)者李在镕層參觀了三星的半導(dǎo)體研發(fā)中心,并商討了有關(guān)公司利用3nm工藝制造芯片的戰(zhàn)略計(jì)劃,以提供給全球客戶。

一、三星電子的GAAFET工藝

早在一年前,三星開(kāi)始進(jìn)行3nm GAAFET工藝的研發(fā),最初計(jì)劃于2021年開(kāi)始量產(chǎn)。

與此同時(shí),三星還曾表示要在2020年之前采用4nm GAAFET工藝,但業(yè)界對(duì)三星是否能在2020年之前將該工藝量產(chǎn)表示懷疑。

從事實(shí)上看,三星將GAAFET芯片投入生產(chǎn)的時(shí)間比業(yè)界預(yù)期的還要早。但隨著三星3nm芯片原型的開(kāi)發(fā),其量產(chǎn)的時(shí)間或許會(huì)比市場(chǎng)預(yù)期更早。

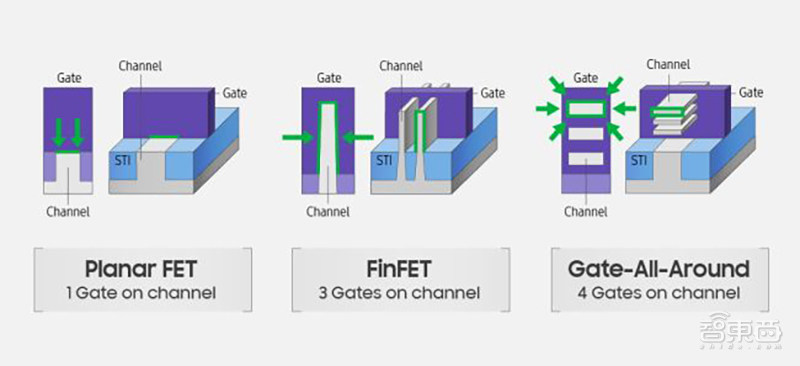

實(shí)際上,GAAFET的工藝設(shè)計(jì)與FinFET大不相同。

FinFET工藝將閘門(mén)設(shè)計(jì)成了像魚(yú)鰭般的3D結(jié)構(gòu),把以往水平的芯片內(nèi)部結(jié)構(gòu)變垂直,把晶體厚度變薄。

這種設(shè)計(jì)不僅能很好地接通和斷開(kāi)電路兩側(cè)的電流,大大降低了芯片漏電率高的問(wèn)題,還大幅地縮短了晶體管之間的閘長(zhǎng)。

而GAAFET的工藝則圍繞通道的四個(gè)側(cè)面設(shè)計(jì),以確保減少功率的泄漏,進(jìn)一步改善對(duì)通道的控制。

此外,GAAFET工藝還能夠?qū)崿F(xiàn)更高效的晶體管設(shè)計(jì),擁有更小的整體制程尺寸,大大提升了芯片的每瓦性能。

二、臺(tái)積電仍在5nm領(lǐng)域發(fā)力

三星電子的老對(duì)手臺(tái)積電在3nm工藝領(lǐng)域似乎還較為低調(diào)。

臺(tái)積電曾表示將在2019年年底啟動(dòng)3nm晶圓廠建設(shè),并表示其進(jìn)展“令人欣慰”,但關(guān)于3nm的技術(shù)細(xì)節(jié)卻未過(guò)多披露。

相反,當(dāng)下臺(tái)積電則更多低將心思放在5nm工藝的研發(fā)中。從去年年底開(kāi)始,關(guān)于臺(tái)積電5nm工藝試產(chǎn)良率的消息頻頻爆出。

就在去年10月,臺(tái)積電表示,其首批5nm工藝已順利拿下蘋(píng)果和華為海思兩大客戶,將分別打造蘋(píng)果A14芯片和華為新一代麒麟芯片。

據(jù)臺(tái)積電上個(gè)月的最新消息表示,其5nm工藝平均良率已提高至50%,2020年上半年即可實(shí)現(xiàn)量產(chǎn)。

而在三星電子則表示,其目標(biāo)要在2030年成為世界第一的半導(dǎo)體制造商。

結(jié)語(yǔ):芯片先進(jìn)制程領(lǐng)域戰(zhàn)火紛飛

多年來(lái),臺(tái)積電和三星的芯片代工之爭(zhēng)愈演愈烈,尤其進(jìn)入到了5nm及以下的先進(jìn)制程領(lǐng)域,除了良率、性能和客戶訂單之爭(zhēng)外,雙方圍繞芯片工藝、半導(dǎo)體材料和光刻機(jī)等方面的競(jìng)爭(zhēng)也更加激烈。

但就目前綜合看來(lái),三星雖然已公布其3nm工藝的最新進(jìn)展,但在良率、訂單等進(jìn)程上,依然是臺(tái)積電更勝一籌。未來(lái),輸了7nm的三星是否能在3nm扳回一城?我們拭目以待。