在全球處理器領(lǐng)域,,以X86架構(gòu)和ARM架構(gòu)為主流的指令集架構(gòu)占據(jù)了絕對(duì)優(yōu)勢(shì),。架構(gòu)授權(quán)成為我國(guó)處理器廠商發(fā)展無法越過的屏障以及發(fā)展保持持續(xù)性的潛在不利因素,。以RISC-V(第五代精簡(jiǎn)指令處理器)為代表的開源指令集架構(gòu)的出現(xiàn),,被業(yè)內(nèi)視為最有可能打破目前處理器生態(tài)格局的途徑,。近年來,,RISC-V在世界范圍內(nèi)逐漸步入發(fā)展熱潮,。2018年以來,,RISC-V在我國(guó)也受到越來越多的重視,,中國(guó)RISC-V產(chǎn)業(yè)聯(lián)盟和中國(guó)開放指令生態(tài)系統(tǒng)(RISC-V)聯(lián)盟相繼成立。如何利用RISC-V的開源特性與新興技術(shù)實(shí)現(xiàn)國(guó)產(chǎn)SoC的國(guó)產(chǎn)化發(fā)展,,成為我國(guó)集成電路產(chǎn)業(yè)共同關(guān)注的話題,。

2019年7月11日下午,,由《電子技術(shù)應(yīng)用》雜志社、中電會(huì)展與信息傳播有限公司,、EETOP(易特創(chuàng)芯)聯(lián)合承辦的“基于RISC-V的SoC國(guó)產(chǎn)化發(fā)展路徑”研討會(huì)在成都世紀(jì)城新國(guó)際會(huì)展中心召開,。電子科技大學(xué)電子科學(xué)與工程學(xué)院副教授黃樂天、芯來科技創(chuàng)始人& CEO胡振波,、知存科技創(chuàng)始人王紹迪從基于RISC-V指令集擴(kuò)展的專用SoC設(shè)計(jì),、國(guó)產(chǎn)化RISC-V處理器核及配套工具鏈、RISC-V在AI-SoC芯片中的應(yīng)用等多方位多角度,,闡述了我國(guó)利用開源開放的RISC-V構(gòu)建中國(guó)自主可控芯的不斷探索,。

《電子技術(shù)應(yīng)用》楊暉(左一)、知存科技王紹迪(左二),、電子科大黃樂天(右二),、芯來科技胡振波(右一)合影

基于RISC-V的SoC國(guó)產(chǎn)化發(fā)展路徑直播視頻

黃樂天:基于RISC-V擴(kuò)展指令集的專用SoC設(shè)計(jì)

電子科技大學(xué)副教授黃樂天博士就職于電子科學(xué)與工程學(xué)院,長(zhǎng)期以來從事計(jì)算機(jī)系統(tǒng)架構(gòu)與系統(tǒng)級(jí)芯片設(shè)計(jì)交叉方向的研究,,包括片上多核處理器與片上網(wǎng)絡(luò),、異構(gòu)計(jì)算系統(tǒng)與芯片、領(lǐng)域?qū)S锰幚砥髋c可重構(gòu)計(jì)算等,。

電子科技大學(xué)副教授黃樂天博士

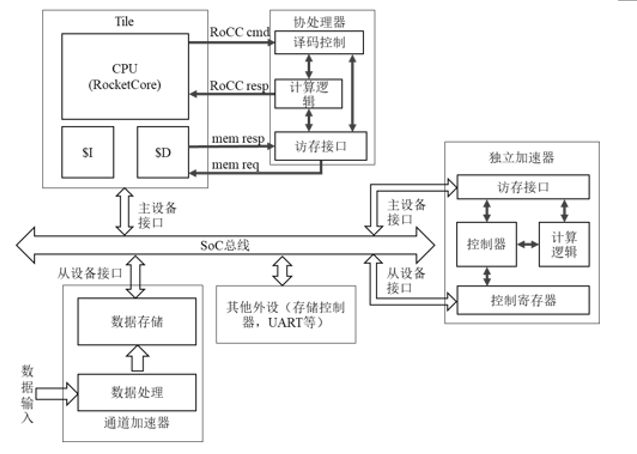

傳統(tǒng)SoC的設(shè)計(jì)方向是以軟制硬,,而目前的SoC必須靠硬件對(duì)軟件進(jìn)行加速,這種加速方式主要有下圖所示三種,。

專用SoC中加速器的三種耦合方式

RISC-V除常規(guī)指令之外,,還有定制指令,并為其預(yù)留了編碼格式,,利用預(yù)留編碼格式,,設(shè)計(jì)人員可以為他們想要加速的應(yīng)用程序添加所需的任何指令。 這是一個(gè)強(qiáng)大的功能,,因?yàn)樗粫?huì)破壞任何軟件兼容性,同時(shí)為發(fā)明和差異化留出空間,。

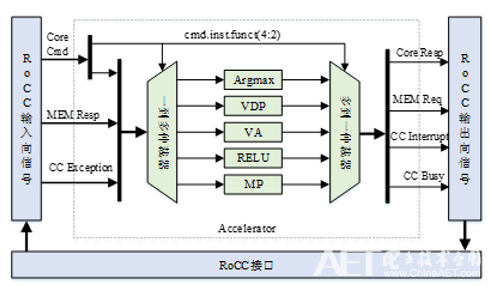

黃博士的團(tuán)隊(duì)基于RISC-V架構(gòu)設(shè)計(jì)了基于自定義擴(kuò)展指令的神經(jīng)網(wǎng)絡(luò)加速器,。

神經(jīng)網(wǎng)絡(luò)加速器的實(shí)現(xiàn)方式

加速器中,5個(gè)加速模塊共用RoCC接口,,需要對(duì)輸入向信號(hào)做一到多仲裁,,輸出向信號(hào)做多到一仲裁。

神經(jīng)網(wǎng)絡(luò)加速器總體硬件設(shè)計(jì)

經(jīng)驗(yàn)證,,該加速器的每個(gè)模塊都能有效地加速相應(yīng)的計(jì)算,,且向量長(zhǎng)度越長(zhǎng),加速效果越明顯,。

上述設(shè)計(jì)案例證明,,RISC-V的指令集格式非常適宜于通過指令擴(kuò)展設(shè)計(jì)專用加速器,,Rocket Chip定義的RoCC給定了較為完備的指令擴(kuò)展接口設(shè)計(jì)方法。但問題也很明顯,,即目前國(guó)產(chǎn)化的RISC-V處理器大多把其當(dāng)成ARM的替代品,,對(duì)于指令擴(kuò)展和專用SoC設(shè)計(jì)的支持不足。未來,,在人工智能/神經(jīng)網(wǎng)絡(luò)領(lǐng)域,,需要繼續(xù)探索指令擴(kuò)展加速器與專用SoC設(shè)計(jì)方法;同時(shí)通過對(duì)各種形式加速器的研究逐步形成設(shè)計(jì)方法學(xué),,從而更加廣泛的指導(dǎo)專用SoC設(shè)計(jì),;在前兩者研究的基礎(chǔ)上提出領(lǐng)域?qū)S茫―omain Specific)SoC架構(gòu)、設(shè)計(jì)自動(dòng)化工具和流程,,形成可以支持“敏捷開發(fā)”的設(shè)計(jì)自動(dòng)化工具集,。

芯來科技:本土RISC-V的先行者和布道者 賦能國(guó)內(nèi)AIoT產(chǎn)業(yè)變革

芯來科技成立于2018年,是中國(guó)大陸知名的專業(yè)RISC-V處理器內(nèi)核IP和解決方案公司,,同時(shí)還是中國(guó)RISC-V產(chǎn)業(yè)聯(lián)盟(CRVIC)副理事長(zhǎng)單位,,以及中國(guó)開放指令集生態(tài)(RISC-V)聯(lián)盟(CRVA)會(huì)員單位,致力于與上下游合作伙伴共同構(gòu)建RISC-V的產(chǎn)業(yè)生態(tài)系統(tǒng),。芯來科技創(chuàng)始人& CEO胡振波出版了國(guó)內(nèi)第一本和第二本RISC-V中文書籍,,堪稱中國(guó)本土RISC-V的先行者和布道者。

芯來科技創(chuàng)始人& CEO胡振波

芯來科技推出的N200系列RISC-V處理器內(nèi)核IP,,專為超低功耗與嵌入式場(chǎng)景而設(shè)計(jì),,達(dá)到業(yè)界一流的指標(biāo),非常適合替代傳統(tǒng)的8051與ARM Cortex-M系列內(nèi)核,。該內(nèi)核IP系列已經(jīng)過量產(chǎn)驗(yàn)證,,目前已經(jīng)全面推向市場(chǎng)。

芯來產(chǎn)品路線圖

其中,,N201內(nèi)核是一款入門級(jí)商用RISC-V處理器內(nèi)核,,可廣泛應(yīng)用于對(duì)面積、成本和功耗敏感的IoT領(lǐng)域芯片的微控制部分,。N201內(nèi)核支持RISC-V RV32IC/EC指令集架構(gòu),、支持機(jī)器模式(Machine Mode),可完美替代ARM Cortex-M0或傳統(tǒng)8051八位內(nèi)核,。

N201內(nèi)核

同時(shí),,芯來科技還推出一項(xiàng)RISC-V處理器內(nèi)核IP普惠計(jì)劃——“一分錢計(jì)劃”,用戶只需三步便可以加入到芯來“一分錢計(jì)劃”,,就可幾乎免費(fèi)地獲取與使用N201內(nèi)核,。

芯來科技“一分錢計(jì)劃”

除了標(biāo)準(zhǔn)的處理器內(nèi)核IP,芯來科技還提供RISC-V專用處理器、軟件工具鏈,、SoC子系統(tǒng)的定制服務(wù)和解決方案,,從而賦能客戶實(shí)現(xiàn)產(chǎn)品的差異化與高效的性價(jià)比。

知存科技:RISC-V在AI SoC芯片中的應(yīng)用

知存科技CEO王紹迪

隨著深度學(xué)習(xí)的進(jìn)一步發(fā)展和AI芯片算力的提升,,邊緣人工智能芯片將迎來更大的爆發(fā)點(diǎn),。安防、自動(dòng)駕駛,、智慧城市,、智慧家庭等應(yīng)用場(chǎng)景都將逐步走向落地。據(jù)有關(guān)預(yù)測(cè),,未來2-5年,,邊緣人工智能芯片市場(chǎng)需求將增長(zhǎng)至3000億人民幣。而AI芯片作為AI的載體,,被大家寄予厚望,,尤其是高算力、低成本,、低功耗的AI芯片,。

邊緣市場(chǎng)增長(zhǎng)迅速 ($20~30B in 2025)

得益于免費(fèi)、開源,、可模組化特色,,基于RISC-V打造低功耗AI芯片成為一個(gè)新的解決思路。RISC-V在AI中的優(yōu)勢(shì)非常明顯:(1)性價(jià)比高,,可顯著降低邊緣AI芯片的成本,;指令集精簡(jiǎn),邏輯硬件少,,芯片面積?。豢砂葱枳杂山M合的模塊化指令集,,針對(duì)專用芯片降低芯片面積,;無向前兼容負(fù)擔(dān),芯片面積??;(2)高效,精簡(jiǎn)指令集,,硬件簡(jiǎn)單、功耗低,,工作頻率高,;(3)靈活,可自定義指令,適用于專用場(chǎng)景,,從而提高效率,;(4)良好的生態(tài)發(fā)展,目前已經(jīng)有200多家公司和組織成員參與維護(hù)和更新指令集,,支持Linux,、RTOS、RT-Thread等,,且工具鏈愈加完善,,未來隨著越來越多玩家的加入,還將涌現(xiàn)越來越好的軟件,。

目前,,RISC-V在AI中的商業(yè)化也取得了多項(xiàng)進(jìn)展,在美國(guó),,NVIDIA早早就加入了RISC-V基金會(huì),,并做了不少研究,近日還公開了在深度神經(jīng)網(wǎng)絡(luò)(DNN)中應(yīng)用RISC-V指令集的可能,。Mythic也與其他十幾家企業(yè)和組織共同成立了OpenHW組織,,特斯拉也加入RISC-V基金會(huì),并考慮在新款芯片中使用免費(fèi)的RISC-V設(shè)計(jì),。在國(guó)內(nèi),,比特大陸在Sophon Edge人工智能芯片中就采用了RISC-V架構(gòu),嘉楠耘智也在去年年底發(fā)布了全球第一款基于RISC-V的邊緣計(jì)算商用芯片,。

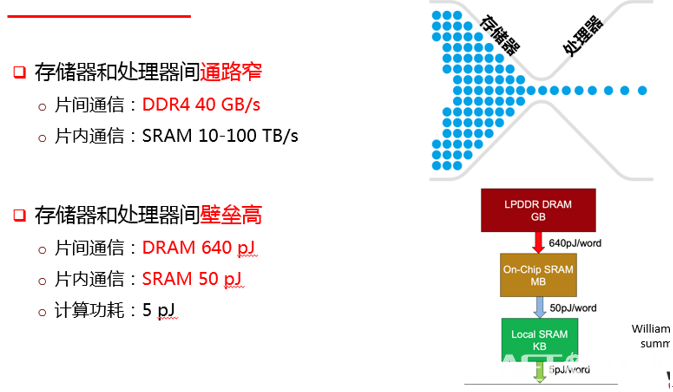

在很多AI推理運(yùn)算中,,90%以上的運(yùn)算資源都消耗在數(shù)據(jù)搬運(yùn)的過程。芯片內(nèi)部到外部的帶寬以及片上緩存空間限制了運(yùn)算的效率?,F(xiàn)在工業(yè)界和學(xué)術(shù)界很多人認(rèn)為存算一體化是未來的趨勢(shì),。

AI運(yùn)算的瓶頸

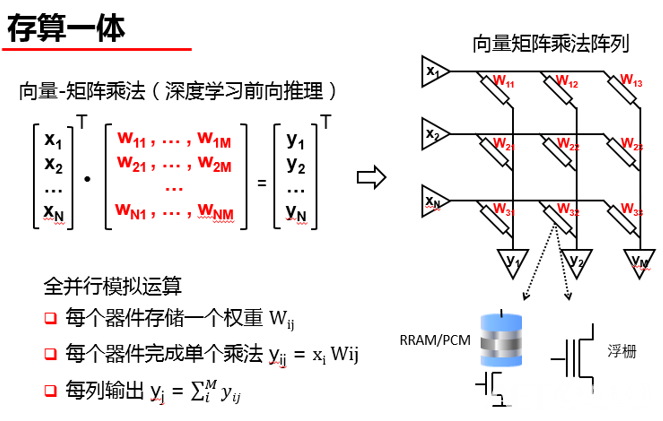

存算一體化分為幾種:DRAM和SSD中植入計(jì)算芯片或者邏輯計(jì)算單元,可以被叫做存內(nèi)處理或者近數(shù)據(jù)計(jì)算,,這種方式非常適合云端的大數(shù)據(jù)和神經(jīng)網(wǎng)絡(luò)訓(xùn)練等應(yīng)用;另一種就是存儲(chǔ)和計(jì)算完全結(jié)合在一起,,使用存儲(chǔ)的器件單元直接完成計(jì)算,比較適合神經(jīng)網(wǎng)絡(luò)推理類應(yīng)用,。

存算一體

知存科技是后者,,即將存儲(chǔ)和計(jì)算結(jié)合到閃存單元中的存算一體。知存科技使用單一浮柵存儲(chǔ)陣列完成深度學(xué)習(xí)網(wǎng)絡(luò)的存儲(chǔ)和計(jì)算功能,,運(yùn)算過程中無需緩存,、內(nèi)存和邏輯運(yùn)算加速器,在存儲(chǔ)單元器件中直接完成計(jì)算,,從而徹底解決人工智能運(yùn)算中的存儲(chǔ)墻和算力問題,。

知存科技的存算一體

目前知存科技基于自主研發(fā)的存算一體架構(gòu)和存儲(chǔ)陣列的嵌入式智能語音芯片已經(jīng)完成流片,支持DNN、LSTM等多種常用網(wǎng)絡(luò),,支持可變運(yùn)算和參數(shù)精度,,預(yù)計(jì)2019年年末進(jìn)入量產(chǎn)。

研討會(huì)現(xiàn)場(chǎng)討論熱烈,,演講嘉賓和與會(huì)聽眾就基于RISC-V的國(guó)產(chǎn)SoC的發(fā)展展開深入探討,。大家一致認(rèn)為,國(guó)產(chǎn)SoC想要擺脫X86,、ARM架構(gòu)的限制,,實(shí)現(xiàn)真正的崛起,RISC-V將是一個(gè)最大的機(jī)遇,,它給了我們和全球一致的起跑線,,錯(cuò)過RISC-V 我們可能又將錯(cuò)過一個(gè)時(shí)代!欣慰的是,,國(guó)內(nèi)RISC-V生態(tài)體系正在逐步建立起來,,也涌現(xiàn)了一批代表性企業(yè)真正投入到基于RISC-V指令集的處理器內(nèi)核及相應(yīng)開發(fā)環(huán)境等工作中??梢灶A(yù)見,,未來幾年,RISC-V將助力國(guó)產(chǎn)SoC迎來最佳發(fā)展期,。