Intel聯(lián)合創(chuàng)始人之一的戈登·摩爾提出了著名的摩爾定律,50多年來(lái)這個(gè)黃金法則主導(dǎo)了硅基半導(dǎo)體的發(fā)展規(guī)律,Intel也是摩爾定律最堅(jiān)定的捍衛(wèi)者。不過(guò)從14nm節(jié)點(diǎn)開始,依托于摩爾定律的Intel Tick-Tock戰(zhàn)略就已經(jīng)變了,升級(jí)周期從2年變成3年,14nm工藝實(shí)際上要戰(zhàn)四代處理器了。盡管Intel一直嘴硬說(shuō)摩爾定律未滅,但傳統(tǒng)半導(dǎo)體這幾年內(nèi)確實(shí)面臨著很大挑戰(zhàn),IRDS(設(shè)備與系統(tǒng)國(guó)際路線圖)日前發(fā)布的一份報(bào)告則給CMOS電路判了死刑——2024年它就會(huì)終結(jié)了。

傳統(tǒng)CMOS集成電路將在2024年走到盡頭

IRDS(International Roadmap for Devices and Systems)是IEEE電子和電子工程師協(xié)會(huì)設(shè)立的一個(gè)組織,從1965年開始每年都會(huì)發(fā)布一份半導(dǎo)體領(lǐng)域中技術(shù)路線圖,之前叫做ITRS(International Technology Roadmap for Semiconductors)路線圖,去年被IEEE重命名為IRDS,這樣可以更全面地反應(yīng)各種系統(tǒng)級(jí)新技術(shù)。

本年度的IRDS路線圖完整版要到11月份才會(huì)發(fā)布,現(xiàn)在發(fā)布是白皮書,但是這次的報(bào)告已經(jīng)足夠引起軒然大波了,因?yàn)樗A(yù)測(cè)傳統(tǒng)CMOS電路在2024年就要終結(jié)了,這又是怎么回事呢?來(lái)看下EETimes的報(bào)道。

首先對(duì)半導(dǎo)體工藝發(fā)展不太了解的讀者建議先看看我們之前做過(guò)的一個(gè)科普文章:沙子做的CPU,憑什么賣那么貴?里面解釋了了半導(dǎo)體技術(shù)的一些術(shù)語(yǔ),比如常見(jiàn)的xxnm工藝指的就是線寬,F(xiàn)inFET、FD-SOI則是指晶體管結(jié)構(gòu),Intel從22nm工藝、TSMC/三星/GF則是從16/14nm節(jié)點(diǎn)開始使用FinFET工藝,今年的工藝會(huì)發(fā)展到10nm,下一代則是7nm,TSMC、三星還提出了5nm工藝路線圖,Intel這邊就比較謹(jǐn)慎,5nm進(jìn)展尚未公布。

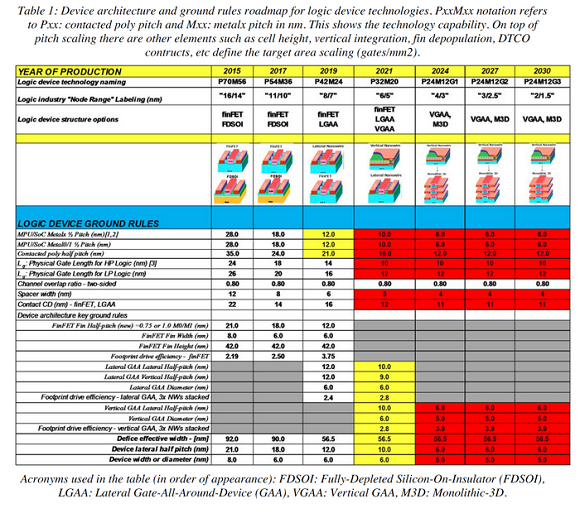

IRDS中介紹的CMOS工藝路線圖

從IRDS路線圖中可以看到,2015年16/14nm節(jié)點(diǎn)開始進(jìn)入FinFET工藝,一直到2021年下下代的5nm節(jié)點(diǎn)FinFET工藝都會(huì)存在,但是2019年就會(huì)開始應(yīng)用新的GAA(gate-all-around,環(huán)繞柵極)晶體管結(jié)果,2024年的4/3nm節(jié)點(diǎn)則會(huì)完全取代FinFET結(jié)構(gòu),這也是為什么這份報(bào)告出來(lái)之后引起熱議的原因,它代表著傳統(tǒng)CMOS電路在2024年走到盡頭了。

從2024年開始,未來(lái)的半導(dǎo)體工藝雖然還會(huì)有2.5nm、1.5nm線寬之分,但是再看下后面的紅字部分,這幾種新工藝的柵極距等指標(biāo)是沒(méi)有變化的,也就是說(shuō)晶體管并不會(huì)一直縮小,在5nm節(jié)點(diǎn)就已經(jīng)沒(méi)啥變化了。

未來(lái)會(huì)使用新的材料、新的3D工藝?yán)^續(xù)提升半導(dǎo)體技術(shù)

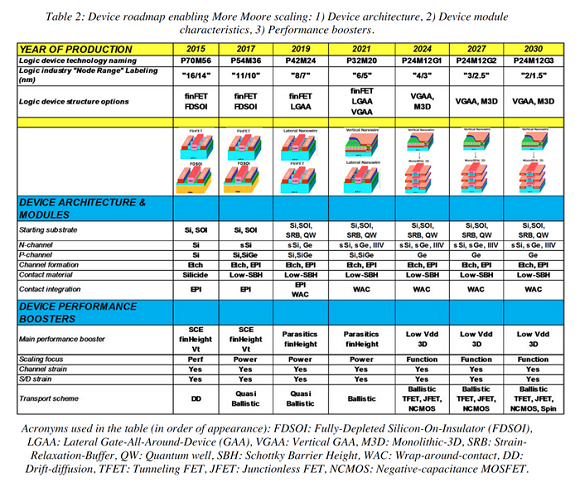

CMOS電路在2024年終結(jié)不代表半導(dǎo)體技術(shù)就沒(méi)有發(fā)展了,IRDS白皮書中也提到了新的發(fā)展方向,包括使用新的半導(dǎo)體材料和工藝,比如使用Ge(鍺)取代硅基半導(dǎo)體,它的電子遷移率比硅更高,電氣性能更好。還有就是3D工藝,這跟目前的NAND閃存發(fā)展過(guò)程有些相似,平面NAND閃存在16/15nm節(jié)點(diǎn)之后就步入瓶頸期,但是廠商開發(fā)了3D NAND閃存,未來(lái)的邏輯半導(dǎo)體芯片也會(huì)走上3D堆棧工藝。