文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.011

中文引用格式: 許谷涵,嚴(yán)偉,朱兆偉,等. 千萬門級模塊魚骨型時鐘網(wǎng)絡(luò)的實現(xiàn)[J].電子技術(shù)應(yīng)用,2016,42(8):53-55,59.

英文引用格式: Xu Guhan,Yan Wei,Zhu Zhaowei,et al. Implementation of FISHBONE-based clock structure in ten-million gates block[J].Application of Electronic Technique,2016,42(8):53-55,59.

0 引言

現(xiàn)階段在芯片后端設(shè)計過程中分割產(chǎn)生的模塊規(guī)模越來越大,單模塊規(guī)模最大已經(jīng)達(dá)到千萬門級。千萬門級模塊中時鐘網(wǎng)絡(luò)復(fù)雜,功耗占比大[1],是芯片設(shè)計中的棘手問題。在28 nm工藝節(jié)點(diǎn)之后由于連線間距進(jìn)一步縮小到0.1 μm以下,插入過多的緩沖單元會使得繞線變長,產(chǎn)生很大的時鐘延遲和功耗,在千萬門級模塊中,時鐘延遲甚至可以達(dá)到一個周期以上。魚骨型時鐘網(wǎng)絡(luò)時鐘根節(jié)點(diǎn)到時鐘末端級數(shù)少,可以節(jié)約功耗和面積[2],在千萬門級模塊中,不論從功耗、延遲,還是從可靠性的角度上看,網(wǎng)型的魚骨結(jié)構(gòu)相比于不定型時鐘樹應(yīng)該會有一定優(yōu)勢[3]。

1 單魚骨型時鐘網(wǎng)絡(luò)的結(jié)構(gòu)

單魚骨型(FISHBONE)時鐘樹的基本結(jié)構(gòu)如圖1所示。對千萬門級模塊而言,使用單魚骨樹來平衡所有的寄存器和宏單元,會造成延遲過大、驅(qū)動能力不夠等一系列問題。

圖1 單魚骨型時鐘結(jié)構(gòu)

因此,我們提出一種寄存器與宏單元分離的多主干驅(qū)動的復(fù)合型時鐘網(wǎng)絡(luò)(H-FISHBONE)。如圖2所示,H-FISHBONE由多個驅(qū)動寄存器的魚骨樹和多組復(fù)合驅(qū)動器驅(qū)動的宏單元塊構(gòu)成,二者分別經(jīng)多級驅(qū)動連接至?xí)r鐘根節(jié)點(diǎn)。

圖2 H-FISHBONE結(jié)構(gòu)

2 H-FISHBONE的實現(xiàn)流程

H-FISHBONE具體實現(xiàn)流程如圖3所示,本文以YCU-AM模塊為例,闡述在后端設(shè)計過程中,如何實現(xiàn)H-FISHBONE型時鐘網(wǎng)絡(luò)。YCU_AM模塊采用三星28 nm工藝,9層繞線金屬。供電電壓1 V,時鐘頻率200 MHz,版圖3 400 μm×3 590 μm,宏單元570個,共2 600萬門。

圖3 H-FISHBONE實現(xiàn)流程

2.1 提取時鐘結(jié)構(gòu),分析門控時鐘單元級數(shù)

用Primetime對初始網(wǎng)表進(jìn)行分析,采取時鐘路徑追蹤的方法可以得到詳細(xì)的時鐘結(jié)構(gòu),主要分析時鐘級數(shù)。如圖4所示,以時鐘根節(jié)點(diǎn)為第0級,按照與時鐘根節(jié)點(diǎn)連接關(guān)系的級數(shù),根節(jié)點(diǎn)后1~3級不等的門控單元(ICG)。

圖4 YCU-AM內(nèi)部時序器件級數(shù)關(guān)系簡圖

2.2 多級時鐘門控單元展平化處理

多級時鐘門控單元的存在,不利于平衡時鐘漂移,所以要將多級門控時鐘單元展平化處理為一級,既能保持控制功耗的功能,也有利于時鐘漂移的平衡。由于DFT設(shè)計過程中,會將ICG復(fù)用到掃描鏈中,因此在工作(Function)模式下,需要先將ICG的掃描鏈?zhǔn)鼓芏巳窟壿嬤B接到邏輯低電平鉗位單元(TIE-0),然后調(diào)用ICC的flatten-clock-gating引擎進(jìn)行展平化處理,為保證展平化過程精準(zhǔn)及節(jié)省運(yùn)行時間,我們要為ICC指出處于二、三級的ICG。

2.3 分離宏單元和寄存器

對于千萬門級模塊,大量的宏單元和寄存器連在同一單魚骨樹上,將不利于平衡時鐘漂移和時序收斂。因此我們將宏單元和寄存器拆分,對宏單元用復(fù)合驅(qū)動器進(jìn)行驅(qū)動構(gòu)建多組宏單元塊,對寄存器構(gòu)建多組FISHBONE。最后進(jìn)行FISHBONE和宏單元塊的再平衡。拆分時,對于同寄存器有共同ICG連接關(guān)系的宏單元,在ICG的輸入端引入一個與其相同類型的偽ICG,將宏單元重新連接到偽ICG上,以保證宏單元的各種輸入條件不變;在時鐘根節(jié)點(diǎn)隔離單元之后插入兩個并聯(lián)的驅(qū)動單元,分別連接宏單元與寄存器。

2.4 插入偽ICG解高扇出(High Fanout)

由于標(biāo)準(zhǔn)單元驅(qū)動能力有限,如果其驅(qū)動的負(fù)載電容過大會產(chǎn)生高扇出問題。我們采取克隆高扇出ICG的方法,克隆出的ICG稱偽ICG。偽ICG是按照距離自動尋址的方式插入,先尋找高扇出ICG最近的寄存器,插入第一個偽器件,偽器件驅(qū)動其周圍70×70范圍內(nèi)的負(fù)載(根據(jù)負(fù)載的多少適當(dāng)減增范圍),然后由近及遠(yuǎn)插入多個偽器件。

2.5 多組FISHBONE的構(gòu)建

如圖4所示,F(xiàn)F1和FF2之間相差一級門控時鐘單元的單元延遲,要插入一個與所用ICG單元延遲相近的緩沖單元,用來平衡FF1和FF2之間的延遲。經(jīng)過以上幾步,得到時鐘結(jié)構(gòu)連接關(guān)系如圖5所示,其中G是偽ICG,B是平衡緩沖單元,H是插入FISHBONE三級驅(qū)動的位置。構(gòu)建FISHBONE的個數(shù),需根據(jù)負(fù)載的數(shù)量和分布來確定。本設(shè)計有44 000個負(fù)載(均勻分布在大約3 000×3 000的范圍內(nèi)),從均勻性和最簡化角度考慮,將版圖分為6個區(qū)域進(jìn)行多魚骨樹的構(gòu)建,每個單魚骨樹驅(qū)動7 000-8 000個負(fù)載。如圖6所示。

圖5 連接關(guān)系圖

圖6 FISHBONE主干的位置分布

FISHBONE的構(gòu)建有以下幾個重要參數(shù):(1)金屬線分布屬性;(2)驅(qū)動比(drive-rate=total load/L3driver);(3)驅(qū)動單元間隔(row-step)。由于高層金屬的抗電遷移能力更強(qiáng),并且對下層的噪聲影響也小很多,所以選擇高層金屬來構(gòu)建FISHBONE。本設(shè)計選擇橫向走線的IA層為主干位置,驅(qū)動分支設(shè)定在M7。

驅(qū)動比用于確定各級緩沖單元的數(shù)量,本設(shè)計中驅(qū)動比設(shè)置為40,可根據(jù)負(fù)載數(shù)量以及之后的靜態(tài)時序分析結(jié)果適當(dāng)調(diào)節(jié)驅(qū)動比。驅(qū)動單元間隔,需要是布局通道(Row)的整數(shù)倍,本設(shè)計設(shè)置為2,可根據(jù)主干金屬線長度適當(dāng)增減。本設(shè)計單魚骨樹詳細(xì)布線如圖7所示。

圖7 FISHBONE詳細(xì)布線圖

2.6 FISHBONE和宏單元塊的再平衡

宏單元和FISHBONE分別是由多組復(fù)合驅(qū)動直接驅(qū)動,與時鐘根節(jié)點(diǎn)的距離和負(fù)載大小不同,選擇的多級驅(qū)動也不同,因此在完成以上步驟之后,要進(jìn)行寄生參數(shù)的提取和靜態(tài)時序分析,對比各個部分的時鐘延遲,適當(dāng)調(diào)節(jié)部分參數(shù)(復(fù)合驅(qū)動的級數(shù)、驅(qū)動比、驅(qū)動間距、主干、分支金屬寬度等)用以平衡時鐘漂移。

3 分析結(jié)果

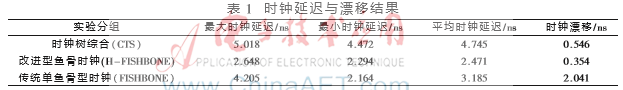

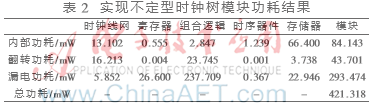

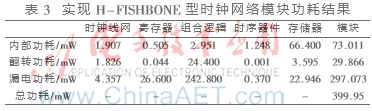

如表1分別是YCU_AM進(jìn)行時鐘樹綜合(CTS)實現(xiàn)不定型時鐘樹、實現(xiàn)單魚骨樹以及本文方法實現(xiàn)H-FISHBONE的三組時序結(jié)果對比。從表中可以看出,單魚骨樹時鐘漂移竟然達(dá)到2 ns,不適用于千萬門級模塊,相比不定型時鐘樹,H-FISHBONE平均時鐘延遲降低了約47%,時鐘漂移降低了約35%。分別對實現(xiàn)CTS和H-FISHBONE后模塊行功耗分析,測試端角ml-cworst-125c-min,測試信號翻轉(zhuǎn)率為0.1,靜態(tài)概率0.5。得到結(jié)果如表2、表3所示;可以看出使用H-FISHBONE模塊單元內(nèi)部功耗降低約13%,動態(tài)翻轉(zhuǎn)功耗降低約31%,使得模塊整體功耗降低約5%。

4 結(jié)束語

本文針對千萬門級以上模塊提出了改進(jìn)型的H-FISHBONE型時鐘網(wǎng)絡(luò),以2 600萬門YCU_AM模塊為例介紹了H-FISHBONE在后端設(shè)計過程中的實現(xiàn)方法,通過實驗結(jié)果發(fā)現(xiàn)H-FISHBONE在降低時鐘延遲和動態(tài)功耗上有顯著的優(yōu)勢,為千萬門級模塊提出了一種在時鐘網(wǎng)絡(luò)構(gòu)建方面減小時鐘偏斜和降低功耗有效可行的方法。

參考文獻(xiàn)

[1] DENG C,CAI Y C,ZHOU Q.Register clustering methodology for low power clock tree synthesis[J].Journal of Computer Science & Technology,2015,30(2):391-403.

[2] LIN H T,CHUANG Y L,YANG Z H, et al. Pulsed-latch utilization for clock-tree power optimization[J].IEEE Transactions on Very Large Scale Integration Systems,2014,22(4):721-733.

[3] CHIPANA R,KASTENSMIDE F L.SET susceptibility analysis of clock tree and clock mesh topologies[C].2014 IEEE Computer Society Annual Symposium on VLSI(ISVLSI).2014:559-564.