摘 要: 介紹了一種新的實(shí)時(shí)工業(yè)以太網(wǎng)總線技術(shù)EtherCAT,該工業(yè)以太網(wǎng)技術(shù)的高度實(shí)時(shí)性、靈活的拓?fù)浣Y(jié)構(gòu)、簡單的配置方法、技術(shù)的開放性等能有效緩解傳統(tǒng)以太網(wǎng)總線技術(shù)傳輸數(shù)據(jù)量小、實(shí)時(shí)性不高、通信接口不統(tǒng)一帶來的工業(yè)控制領(lǐng)域瓶頸問題。從EtherCAT的運(yùn)行原理及其從站硬件電路設(shè)計(jì)所需芯片選型入手,對(duì)芯片的選擇以及外圍電路設(shè)計(jì)進(jìn)行了詳細(xì)的描述。通過對(duì)幾種實(shí)時(shí)工業(yè)以太網(wǎng)通信技術(shù)的比較證明了該種實(shí)時(shí)工業(yè)以太網(wǎng)技術(shù)的數(shù)據(jù)傳輸?shù)母咚傩浴?/p>

關(guān)鍵詞: EtherCAT;PHY芯片;從站控制器;硬件電路

0 引言

隨著伺服控制系統(tǒng)日益復(fù)雜,傳統(tǒng)的現(xiàn)場(chǎng)總線技術(shù)已經(jīng)無法給伺服控制領(lǐng)域帶來飛躍性的成就。因此,國內(nèi)外公司紛紛提出其他工業(yè)以太網(wǎng)協(xié)議以改善這種情況,其中德國Beckhoff開發(fā)的EtherCAT以其卓越的性能及基于普通以太網(wǎng)標(biāo)準(zhǔn)的特點(diǎn),逐漸成為伺服控制總線技術(shù)的主流。因此,深入研究EtherCAT并將其實(shí)際應(yīng)用于伺服控制領(lǐng)域具有重要意義。

1 EtherCAT原理

EtherCAT采用主從式通信結(jié)構(gòu)。主站向各個(gè)從站發(fā)送以太網(wǎng)數(shù)據(jù)幀,數(shù)據(jù)幀經(jīng)過各個(gè)從站時(shí)經(jīng)從站分析其中的指令進(jìn)行數(shù)據(jù)的提取或插入從站自身的數(shù)據(jù),并將工作計(jì)數(shù)器(Working Counter,WKC)更新。最終與主站事先設(shè)置的預(yù)期WKC值作比較,以判斷是否經(jīng)過了所有的從站并被正確處理。由于從站對(duì)數(shù)據(jù)幀的接收與編碼及轉(zhuǎn)發(fā)、數(shù)據(jù)的提取與插入都是通過硬件完成,所以數(shù)據(jù)幀在每個(gè)從站停留的時(shí)間極小,保證了EtherCAT的實(shí)時(shí)性。經(jīng)過最后一個(gè)從站處理后的數(shù)據(jù)幀將返回主站,主站接收并處理后,一次通信完成[1]。這種通信方式不會(huì)引起通信通路的堵塞,可保證網(wǎng)絡(luò)的實(shí)時(shí)性和正確性。整個(gè)通信過程如圖1。

2 EtherCAT從站硬件設(shè)計(jì)

凡是能夠發(fā)送和接收以太網(wǎng)數(shù)據(jù)幀的設(shè)備都可以作為主站,而且主站功能完全由軟件實(shí)現(xiàn)[1]。從站的建設(shè)則需要專用的集成電路搭建,這也是本文研究的重點(diǎn)。

2.1 EtherCAT從站硬件結(jié)構(gòu)

根據(jù)DSP是否支持EtherCAT,相應(yīng)的設(shè)計(jì)方法也不同。

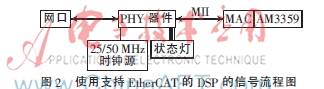

如果使用DSP支持EtherCAT,如TI的AM3359,則信號(hào)流程圖如圖2。

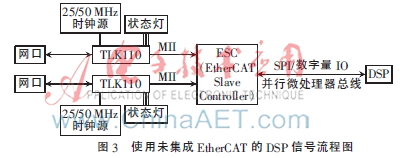

但是目前更多的芯片內(nèi)部并沒有集成EtherCAT模塊,在這些芯片上實(shí)現(xiàn)性能更加優(yōu)異的EtherCAT正是本文所要研究的重點(diǎn)。使用未集成EtherCAT模塊的DSP建立從站硬件的信號(hào)流程圖如圖3所示[1]。

2.2 EtherCAT從站硬件芯片選擇

目前常用的從站硬件建設(shè)方法是使用德國Beckhoff公司提供的從站控制器(EtherCAT Slave Controller,ESC),常用的兩種從站控制專用芯片如表1所示[1]。

如果只有一個(gè)從站,則只需要一個(gè)MII端口。但是考慮到EtherCAT可以完成一個(gè)主站和多個(gè)從站的通信,為長遠(yuǎn)考慮,選擇ET1100。ET1100使用MII接口時(shí),對(duì)外接的PHY器件特別是其時(shí)鐘源有如下要求:

(1)PHY芯片和ET1100使用同一個(gè)時(shí)鐘源;

(2)PHY的TX_CLK信號(hào)和PHY的輸入時(shí)鐘之間的相位關(guān)系必須固定,最大允許5 ns的抖動(dòng);

(3)ET1100不使用PHY的TX_CLK信號(hào),以省略ET1100內(nèi)部的發(fā)送FIFO。

符合以上要求的PHY芯片很多,這里選擇TI公司的TLK110。

TLK110是單口10M/100M以太網(wǎng)物理層信號(hào)收發(fā)器,它支持標(biāo)準(zhǔn)MII接口,供電靈活,3.3 V獨(dú)立供電,也可以使用3.3 V/1.5 V聯(lián)合供電。功耗低,小于205 mW,使用25 MHz時(shí)鐘源。

2.3 EtherCAT從站硬件電路設(shè)計(jì)

采用的網(wǎng)口為普通網(wǎng)口,給TLK110傳遞的信號(hào)為兩組差分信號(hào)RD+/RD-和TD+/TD-。另外C_YLW/C_GRN信號(hào)燈主要用來判別網(wǎng)口是否正確連接和是否正常工作。TLK110通過MII接口與ET1100通信,其外圍電路設(shè)計(jì)如圖4。

MII_RXD[3:0]要使用2.2 kΩ的電阻上拉到3.3 V,因?yàn)門LK110的RXD管腳發(fā)送網(wǎng)絡(luò)信號(hào)給ET1100,使用上拉一方面可保證發(fā)送的信號(hào)不存在0或1以外的不確定狀態(tài),即信號(hào)的確定性;另一方面,管腳上拉提供驅(qū)動(dòng)能力,確保信號(hào)能到達(dá)ET1100。該P(yáng)HY芯片管腳所接信號(hào)既有模擬信號(hào),又有數(shù)字信號(hào),在做PCB設(shè)計(jì)時(shí)容易引起數(shù)模串?dāng)_。所以在設(shè)計(jì)原理圖時(shí)將22號(hào)管腳經(jīng)0 Ω電阻直接接到數(shù)字電源。同樣的方法處理15、19的地信號(hào),從而保證TLK110所接均為數(shù)字信號(hào),便于PCB設(shè)計(jì)同時(shí)避免模數(shù)信號(hào)串?dāng)_引發(fā)問題。TLK110的時(shí)鐘信號(hào)由ET1100提供,輸入到TLK110的XI管腳,而復(fù)位信號(hào)則由FPGA提供。要實(shí)現(xiàn)EtherCAT的多從站通信,需要兩塊TLK110芯片,另一塊芯片與該TLK110接線一致。

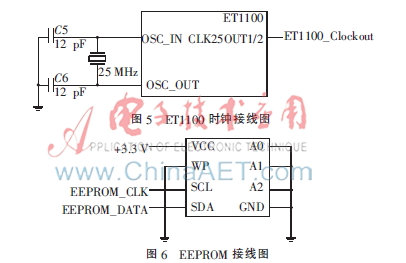

本設(shè)計(jì)中,ET1100通過SPI接口與FPGA相連,同時(shí)通過MII接口連接兩個(gè)PHY芯片,并給PHY器件提供時(shí)鐘信號(hào)。由于ET1100自身沒有如EEPROM一類的存儲(chǔ)器件,所以選擇帶I2C接口的EEPROM來存儲(chǔ)設(shè)備的配置信息。圖5、6為ET1100的時(shí)鐘接線圖以及外掛EEPROM接線圖。

ET1100的I/O管腳可以使用3.3 V或5 V供電,并且該電壓值決定所有輸入輸出信號(hào)的電壓。一般選擇 3.3 V電壓供電。所有VCCIO和GNDIO之間都要接濾波電容。ET1100內(nèi)核和PLL供電電壓為2.5 V,既可由外部提供也可由芯片內(nèi)部通過轉(zhuǎn)換I/O口電壓得到。同時(shí),VCCcore和GNDcore之間也需要使用濾波電容連接。如圖7。

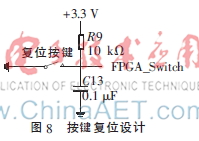

該芯片復(fù)位為低電平復(fù)位,復(fù)位信號(hào)來源為FPGA,按鍵復(fù)位設(shè)計(jì)如圖8。

一般情況下FPGA_Switch置于高電平,需要復(fù)位時(shí)手動(dòng)按下復(fù)位按鍵,F(xiàn)PGA_Switch變成低電平,此時(shí)FPGA經(jīng)內(nèi)部編程實(shí)現(xiàn)給其他芯片提供低平復(fù)位信號(hào)。

在本設(shè)計(jì)中,ET1100不直接與DSP相連,信號(hào)流程圖如圖9所示。

ESC與DSP之間可通過過程數(shù)據(jù)接口(Process Data Interface,PDI)連接,一般使用的有數(shù)字量I/O接口、SPI從站接口、并行微處理器總線接口。由于SPI接口占用的管腳比較少,其他的管腳可以作為普通的I/O口使用,包括16個(gè)通用數(shù)字輸入引腳和16個(gè)通用數(shù)字輸出引腳[1],所以采用SPI接口連接ESC與DSP。一般情況下,ET1100直接與DSP相連,但是這里在中間加入FPGA,雖然運(yùn)行時(shí)間會(huì)因此增加幾微秒,但是由于硬件電路的可變更性比較低,作為實(shí)驗(yàn)板卡的設(shè)計(jì),要盡量考慮功能的豐富性以及使用的長遠(yuǎn)性,所以這里將網(wǎng)口數(shù)據(jù)通過FPGA,以便于日后需要作出更改時(shí),不必更改硬件線路,只需改寫FPGA程序。另外,加入FPGA便于引出測(cè)試點(diǎn),可隨時(shí)監(jiān)測(cè)傳輸?shù)臄?shù)據(jù)。

3 實(shí)驗(yàn)性能分析

在表2的實(shí)驗(yàn)條件下,對(duì)各個(gè)以太網(wǎng)協(xié)議傳輸速率進(jìn)行比較,得到如表3[2]所示數(shù)據(jù)。

表3中的數(shù)據(jù)顯示各個(gè)實(shí)時(shí)工業(yè)以太網(wǎng)協(xié)議在同一實(shí)驗(yàn)條件下的數(shù)據(jù)傳輸時(shí)間。由表中數(shù)據(jù)明顯可以看出,EtherCAT傳輸?shù)攘繑?shù)據(jù)所用時(shí)間遠(yuǎn)遠(yuǎn)小于其他以太網(wǎng)協(xié)議,即EtherCAT的高速性相對(duì)突出。

4 結(jié)論

本文針對(duì)傳統(tǒng)以太網(wǎng)總線技術(shù)存在的短板,介紹了一種新的實(shí)時(shí)工業(yè)以太網(wǎng)技術(shù)EtherCAT。通過對(duì)EtherCAT運(yùn)行原理的分析,詳細(xì)描述了如何利用不含EtherCAT控制模塊的DSP搭建EtherCAT從站硬件,包括從站硬件設(shè)計(jì)中的芯片選型以及電路設(shè)計(jì),并通過比較各個(gè)工業(yè)以太網(wǎng)協(xié)議的數(shù)據(jù)傳輸速率,最終證明了EtherCAT高速傳輸方面的卓越性能。但是由于時(shí)間、實(shí)驗(yàn)條件以及個(gè)人能力所限,對(duì)EtherCAT的探究目前僅限于實(shí)驗(yàn)室中。如何將這種優(yōu)秀的工業(yè)以太網(wǎng)技術(shù)應(yīng)用到實(shí)際工業(yè)控制領(lǐng)域中需要進(jìn)行更加深入的研究。

參考文獻(xiàn)

[1] 郇極,劉艷強(qiáng).工業(yè)以太網(wǎng)現(xiàn)場(chǎng)總線EtherCAT驅(qū)動(dòng)程序設(shè)計(jì)及應(yīng)用[M].北京:北京航空航天大學(xué)出版社,2010.

[2] ETG. EtherCAT_Introduction_CN[EB/OL].(2012-09-20)[2014-02-26]. http://www.ethercat.org.cn.