摘 要: 針對(duì)傳統(tǒng)固定監(jiān)控架設(shè)成本高、監(jiān)控有死角且需要布置的視頻采集端個(gè)數(shù)太多的情況,提出一種基于ARM和FPGA相結(jié)合架構(gòu)的移動(dòng)視頻監(jiān)控系統(tǒng)及其軟硬件實(shí)現(xiàn)方法,在減少視頻采集端節(jié)點(diǎn)的前提下,能夠全方位實(shí)時(shí)捕捉用戶所需的信息。該系統(tǒng)由電機(jī)控制模塊、視頻采集模塊和無(wú)線網(wǎng)絡(luò)控制模塊構(gòu)成,實(shí)現(xiàn)了無(wú)線視頻監(jiān)控系統(tǒng);基于Linux操作系統(tǒng)、Web服務(wù)器和視頻編碼器,實(shí)現(xiàn)了用戶可以通過(guò)Internet遠(yuǎn)程查看目標(biāo)現(xiàn)場(chǎng)的狀況。

關(guān)鍵詞: 視頻監(jiān)控;ARM;FPGA;Linux;Internet

中國(guó)視頻監(jiān)控市場(chǎng)快速發(fā)展,數(shù)字監(jiān)控逐步成為主流,網(wǎng)絡(luò)化、個(gè)人化和智能化將是中國(guó)視頻監(jiān)控市場(chǎng)重要的發(fā)展趨勢(shì)。但當(dāng)前基于流媒體傳輸?shù)募夹g(shù)對(duì)網(wǎng)絡(luò)條件要求較高,不能大面積推廣,固定監(jiān)控成本太高。如何將視頻監(jiān)控與Interne相結(jié)合,使監(jiān)控人員可以隨時(shí)隨地實(shí)施監(jiān)控,是現(xiàn)代監(jiān)控技術(shù)急需解決的問(wèn)題。另一方面,目前視頻監(jiān)控系統(tǒng)采用的微控制器多是ARM9、ARM11等系列微控制器,ARM微控制器硬件外設(shè)出廠時(shí)已經(jīng)固定,不利于用戶進(jìn)行硬件擴(kuò)展和升級(jí),而ARM和FPGA相結(jié)合的多芯片解決方案又會(huì)導(dǎo)致系統(tǒng)成本太高,同時(shí)還會(huì)造成系統(tǒng)資源的浪費(fèi),功耗太大。針對(duì)以上不足,本文提出了一種新的解決方案,采用Zynq系列處理器,芯片采用的是高性能Cortex-A9雙核和FPGA相結(jié)合,ARM部分可以解決高清視頻的處理問(wèn)題,可編程邏輯FPGA部分可以升級(jí)和擴(kuò)展硬件。

1 移動(dòng)視頻監(jiān)控系統(tǒng)架構(gòu)

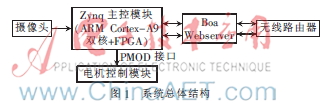

本設(shè)計(jì)的主控板為Digilent公司的ZedBoard開(kāi)發(fā)板,主芯片Zynq7020結(jié)合高性能雙核ARM Cortex-A9 MPCore處理系統(tǒng)和可編程邏輯于一體[1]。視頻采集端位于移動(dòng)小車(chē)之上,從而達(dá)到移動(dòng)采集視頻的目的。系統(tǒng)的設(shè)計(jì)主要包括ARM控制部分的設(shè)計(jì)和FPGA邏輯部分的設(shè)計(jì)。ARM部分主要用來(lái)運(yùn)行操作系統(tǒng)和系統(tǒng)上的應(yīng)用軟件,如Web服務(wù)器Boa,視頻編碼器mjpg-streamer;FPGA部分主要用來(lái)擴(kuò)展硬件資源,進(jìn)行小車(chē)電機(jī)驅(qū)動(dòng)部分PWM IP核的設(shè)計(jì)。系統(tǒng)總體結(jié)構(gòu)框圖如圖1所示。各模塊功能為:攝像頭負(fù)責(zé)視頻圖像采集,Zynq主控模塊負(fù)責(zé)ARM操作系統(tǒng)部分和FPGA邏輯資源部分,電機(jī)控制模塊負(fù)責(zé)智能小車(chē)的運(yùn)動(dòng),Boa Webserver負(fù)責(zé)網(wǎng)絡(luò)的交互,無(wú)線路由器負(fù)責(zé)無(wú)線網(wǎng)絡(luò)數(shù)據(jù)的收發(fā)。

系統(tǒng)上電之后,首先自動(dòng)執(zhí)行芯片內(nèi)部固化的芯片初始化程序,然后執(zhí)行第一階段的啟動(dòng)加載器FSBL,使用比特流文件(PWM IP核設(shè)計(jì)生成的bit文件)對(duì)FPGA部分進(jìn)行配置,待FPGA配置完成后,開(kāi)始執(zhí)行U-boot引導(dǎo)程序,啟動(dòng)Linux操作系統(tǒng)[2]。系統(tǒng)啟動(dòng)完成后,智能小車(chē)通過(guò)無(wú)線路由器產(chǎn)生無(wú)線信號(hào),用戶在另一端就可以通過(guò)網(wǎng)絡(luò)來(lái)連接智能小車(chē)終端,實(shí)施視頻監(jiān)控。用戶和系統(tǒng)的交互實(shí)現(xiàn)如圖2所示。

本文主要介紹電機(jī)控制部分的設(shè)計(jì),具體包括電機(jī)控制部分硬件電路的設(shè)計(jì),F(xiàn)PGA部分PWM IP核的設(shè)計(jì),Linux操作系統(tǒng)PWM驅(qū)動(dòng)程序的設(shè)計(jì)。

2 電機(jī)控制部分的設(shè)計(jì)

2.1 電機(jī)控制部分硬件電路的設(shè)計(jì)

該模塊主要由L298P雙H橋直流電機(jī)驅(qū)動(dòng)芯片實(shí)現(xiàn)。由于一個(gè)L298P芯片可以驅(qū)動(dòng)兩個(gè)直流電機(jī),小車(chē)有4個(gè)車(chē)輪,因此需要兩塊L298P芯片[3]。同時(shí),為了減少使用的FPGA I/O引腳數(shù)量,在原理圖設(shè)計(jì)中采用了四二輸入或非門(mén)芯片SN74HC02D,這樣用兩個(gè)I/O引腳就可以控制L298P的4個(gè)輸入端。DIR1、DIR2、PWM1、PWM2通過(guò)Zedboard的PMOD接口與FPGA相連。原理圖如圖3所示,圖中IN1、IN2、IN3、IN4為輸入信號(hào),ENA、ENB為使能信號(hào)。ENA控制IN1、IN2的輸入使能,ENB控制IN3、IN4的輸入使能。當(dāng)ENA為1,DIR1為1時(shí)(也就是IN1為0,IN2為1時(shí)),P1接口上的電動(dòng)機(jī)正轉(zhuǎn);當(dāng)ENA為1,DIR1為0時(shí)(也就是IN1為1,IN2為0時(shí)),P1接口上的電動(dòng)機(jī)反轉(zhuǎn);當(dāng)ENA為0時(shí),P1接口上的電動(dòng)機(jī)停止。與P2口連接的電動(dòng)機(jī)原理同上。

2.2 FPGA部分PWM IP核的設(shè)計(jì)

Xilinx嵌入式系統(tǒng)部分的設(shè)計(jì)由其公司推出的EDK(Embedded Development Kit)開(kāi)發(fā)套件實(shí)現(xiàn),EDK具有完成嵌入式系統(tǒng)設(shè)計(jì)的一整套工具,即:硬件設(shè)計(jì)工具XPS(Xilinx Platform Studio)和軟件設(shè)計(jì)工具SDK(Xilinx Software Development Kit),硬件設(shè)計(jì)步驟如下:(1)設(shè)置新工程路徑;(2)自定義IP配置外設(shè);(3)建立UCF文件;(4)bit流的生成[4]。自定義IP的部分主要實(shí)現(xiàn)電機(jī)的正轉(zhuǎn),反轉(zhuǎn)和停止控制。關(guān)鍵VerilogHDL代碼如下:

case(state)

//電機(jī)停止

′N(xiāo)OP:{pwm_left,pwm_right}<={7′d0,7′d0};

′GOING://電機(jī)正向旋轉(zhuǎn)

begin

if(dis_value>31)

{pwm_left,pwm_right,dir_lself,dir_rself}

<={7′d100,7′d100,1′d0,1′d0};

else

{pwm_left,pwm_right,dir_lself,dir_rself}<=

{{dis_value[4:0],2′b0},{dis_value[4:0],2′b0},1′d1,1′d1};

end

′RETURN://電機(jī)反向旋轉(zhuǎn)

begin

if(dir_value==3′b010)

{pwm_left,pwm_right,dir_lself,dir_rself}<={7′d80,7′d80,1′d1,1′d0};

else

{pwm_left,pwm_right,dir_lself,dir_rself}<={7′d80,7′d80,1′b0,1′b1};

end

endcase

在本設(shè)計(jì)中,對(duì)電機(jī)的控制,傳輸?shù)臄?shù)據(jù)量較小,只需要添加一個(gè)低速的AXI4-Lite總線設(shè)備PWM模塊來(lái)控制PMOD接口就可以實(shí)現(xiàn)硬件設(shè)備之間通信,其中AXI4-Lite的全局時(shí)ACLK設(shè)置為100 MHz,PWM模塊分配的起始物理地址為0x6CA00000,空間大小為64 KB,PWM配置信息如圖4所示。

2.3 Linux下電機(jī)驅(qū)動(dòng)部分的設(shè)計(jì)

由于遠(yuǎn)端傳輸是在Linux系統(tǒng)下TCP/IP協(xié)議實(shí)現(xiàn)的,因此,編寫(xiě)Linux下的IP驅(qū)動(dòng),應(yīng)用程序就可以通過(guò)Linux的標(biāo)準(zhǔn)接口訪問(wèn)FPGA的PMOD接口設(shè)備。本設(shè)計(jì)編寫(xiě)的是字符型設(shè)備驅(qū)動(dòng)程序,包含設(shè)備加載、設(shè)備卸載以及文件操作函數(shù)。PWM模塊加載時(shí)系統(tǒng)調(diào)用module_init(pwm_init)宏實(shí)現(xiàn)模塊的初始化操作,在本系統(tǒng)中pwm_init()函數(shù)主要完成以下工作:(1)內(nèi)核注冊(cè)字符型設(shè)備驅(qū)動(dòng);(2)創(chuàng)建PWM設(shè)備類(lèi);(3)利用PWM設(shè)備類(lèi)創(chuàng)建設(shè)備;(4)將PWM模塊物理地址映射到虛擬地址上[5]。部分關(guān)鍵代碼如下所示:

//XPS分配的物理地址

#define PWM_MOUDLE_PHY_ADDR 0x6CA00000

//注冊(cè)驅(qū)動(dòng)

pwm_driver_major=register_chrdev(0,DEVICE_NAME,&pwm_driver_fops);

pwm_driver_class=class_create(THIS_MODULE,"

pwm_driver");//創(chuàng)建設(shè)備類(lèi)

pwm_driver_device=device_create(pwm_driver_class,NULL,MKDEV(pwm_driver_major,0),NULL,"pwm_device");

//利用設(shè)備類(lèi)創(chuàng)建設(shè)備

//將PWM IP物理地址映射為虛擬地址

pwm_fre_addr=(unsignedlong)ioremap(PWM_MOUDLE_ PHY_ADDR,sizeof(u32));

初始化工作結(jié)束,但是僅有初始化函數(shù),設(shè)備仍然無(wú)法工作,還需要有實(shí)現(xiàn)頻率和占空比的調(diào)節(jié)機(jī)制。控制PWM的頻率函數(shù)如下所示:

static ssize_t sys_pwm_frequency_set(struct device*dev, struct device_attribute*attr,const char*buf,size_t count)

{

long value=0;

int i;

frequency=0;

//修改頻率之前,關(guān)閉PWM模塊

outl(value,pwm_fre_addr);

//將寫(xiě)入pwm_frequency中的字符串轉(zhuǎn)化為整數(shù)

for(i=0;i<count-1;i++)

{

frequency*=10;

frequency+=buf[i]-′0′;

}

//100 MHz/frequency,100 MHz在XPS中已經(jīng)設(shè)定

if(value>100000000)value=100000000;

value=100000000/frequency;

//將計(jì)數(shù)值寫(xiě)入到PWM模塊的pwm_fre_addr寄存器中

outl(value,pwm_fre_addr);

return count;

}

控制PWM占空比的函數(shù)和控制PWM頻率的函數(shù)一樣。

3 實(shí)驗(yàn)結(jié)果及測(cè)試

系統(tǒng)的主控制板為Zedboard開(kāi)發(fā)板,上電啟動(dòng)后,無(wú)線路由器會(huì)發(fā)布一個(gè)SSID為T(mén)p_Link_5C90的無(wú)線網(wǎng)絡(luò),可以通過(guò)任何可以上網(wǎng)的設(shè)備連接這個(gè)網(wǎng)絡(luò)。在瀏覽器中輸入網(wǎng)址:192.168.1.100,就會(huì)登錄到移動(dòng)視頻監(jiān)控的網(wǎng)頁(yè)上,通過(guò)界面的按鈕控制視頻終端的運(yùn)行。

本文設(shè)計(jì)采用Xilinx All Programmable芯片Zynq作為主控CPU,F(xiàn)PGA部分可以實(shí)現(xiàn)邏輯擴(kuò)展和功能補(bǔ)充。例如:自定義通信協(xié)議、IP核,同時(shí)還可以利用Xilinx的部分可重配置技術(shù)升級(jí)硬件系統(tǒng),易于后期擴(kuò)展和硬件升級(jí);ARM部分采用的是性能較高的Cortex-A9雙核,使得對(duì)高清晰視頻的處理較為流暢,而且系統(tǒng)整體功能也比較穩(wěn)定。相比于傳統(tǒng)的模擬監(jiān)控,數(shù)字視頻處理技術(shù)提高了圖像的質(zhì)量和監(jiān)控效率。

設(shè)計(jì)中采用軟硬件協(xié)同設(shè)計(jì)的方法,即:在整個(gè)系統(tǒng)及定義的基礎(chǔ)上,同時(shí)對(duì)軟硬件進(jìn)行設(shè)計(jì)和協(xié)調(diào),其中包括軟硬件的劃分(哪些功能使用軟件完成,哪些功能使用硬件完成)、軟硬件系統(tǒng)的開(kāi)發(fā)與聯(lián)合調(diào)試,降低了開(kāi)發(fā)風(fēng)險(xiǎn),縮短了開(kāi)發(fā)周期。

參考文獻(xiàn)

[1] Xilinx Inc. UG585, Zynq-7000 All Programmable SoC Technical Reference Mannual[Z]. 2013.

[2] Xilinx Inc. UG873, Zynq-7000 All Programmable SoC: Concepts, Tools and Techniques[Z]. 2013:12-35,40-53.

[3] 王芳芳,張歡.基于Zynq平臺(tái)的動(dòng)態(tài)智能家居系統(tǒng)的設(shè)計(jì)[J].軟件,2013,34(8):98-100.

[4] 胡典榮,郭春生.基于ZedBoard的SPI和以太網(wǎng)傳輸設(shè)計(jì)[J].杭州電子科技大學(xué)學(xué)報(bào),2013,33(5):126-129.

[5] 陸佳華,江舟,馬岷.嵌入式系統(tǒng)軟硬件協(xié)同設(shè)計(jì)指南:基于Xilinx Zynq[M].北京:機(jī)械工業(yè)出版社,2013.