嵌入式邏輯分析儀—SigbalTap II,是Altera Quartus II 自帶的嵌入式邏輯分析儀,與Modelsim軟件仿真有所不同,是在線式的仿真,更準(zhǔn)確的觀察數(shù)據(jù)的變化,方便調(diào)試。

很多學(xué)過單片機(jī)的孩子認(rèn)為,單片機(jī)可以在線單步調(diào)試,而FPGA" style="outline-style: none; color: rgb(51, 51, 51); text-decoration: none;">FPGA是并發(fā)的,不能單步調(diào)試,這使得FPGA的調(diào)試學(xué)習(xí)帶來了困難。其實這個說法不是完全正確的。別忘了,還有SignalTap II Logic Analyzer。有了這個嵌入式邏輯分析儀,在調(diào)試多通道或單通道數(shù)據(jù),進(jìn)行數(shù)據(jù)采樣、監(jiān)控等操作時,給我們帶來了很大的方便,因此,FPGA的學(xué)習(xí)中,利用JTAG來調(diào)試SiganlTap II將會有很大的幫助。

二、應(yīng)用實例

本例中用正弦波、三角波、鋸齒波、方波波形數(shù)據(jù)為參考,簡要講解SignalTap II Logic Analyzer軟件的應(yīng)用,步驟如下:

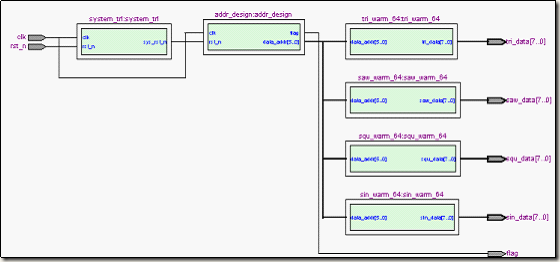

(1)新建工程,設(shè)計代碼,引腳配置,RTL圖如下

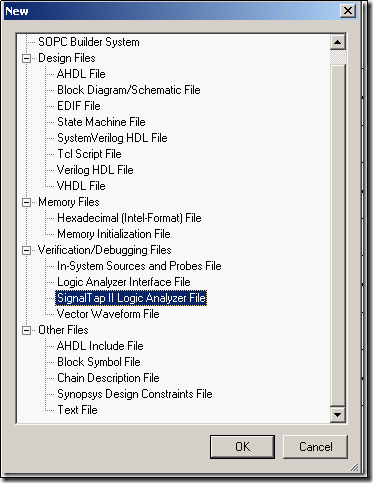

(2)新建SignalTap II 文件

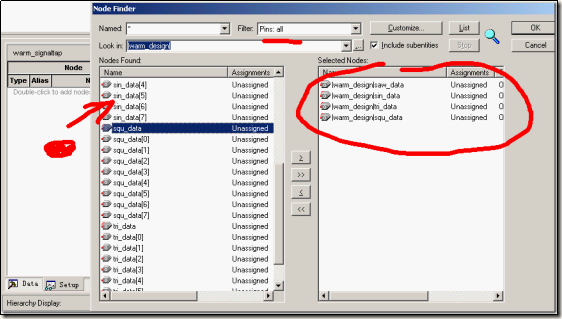

(3) 設(shè)置待測信號名

(4)在node雙擊添加需要觀察的數(shù)字信號;不要調(diào)入系統(tǒng)時鐘,因為本例打算用系統(tǒng)時鐘來做邏輯分析儀的采樣時鐘

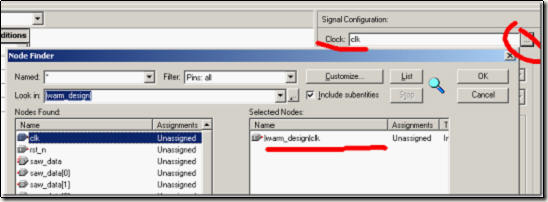

(5)添加系統(tǒng)采樣時鐘(類似示波器的采樣)

(6)設(shè)置采樣深度:因為占用ESB/M9K,采樣深度最好小于9K,這里設(shè)置為2K

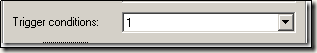

(7)設(shè)置采樣其實觸發(fā)位置:跳變沿觸發(fā)

(8)觸發(fā)方式:

(此處我也不是很清楚,大概各種模式吧)

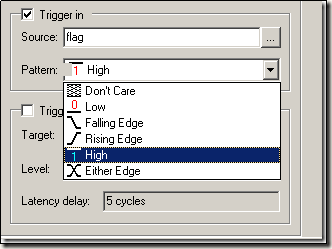

(9)設(shè)置觸發(fā)輸入:選擇觸發(fā)信號以及觸發(fā)方式,flag為觸發(fā)使能信號,實際工程中沒用,只是signaltap ii的使能信號;高電平觸發(fā),設(shè)置如下:

注意:flag為邊沿采樣信號,當(dāng)flag變化的時候,恰好warm_data在穩(wěn)態(tài),因此將flag作為采樣的觸發(fā);當(dāng)然在低速地要求的情況下,flag也可以省略,SiganlTap II 會自動根據(jù)一定頻率采樣。

(10)Save and Yes,再次編譯,和本工程捆綁在一起Download to Device,(當(dāng)然也可以在Settings設(shè)置);關(guān)于PIN,如果沒有邏輯分析儀測試沒有信號輸入,如果你懶得設(shè)置,可以不分配out的信號,但是clk和rst_n必須分配,因為那是系統(tǒng)的驅(qū)動信號。

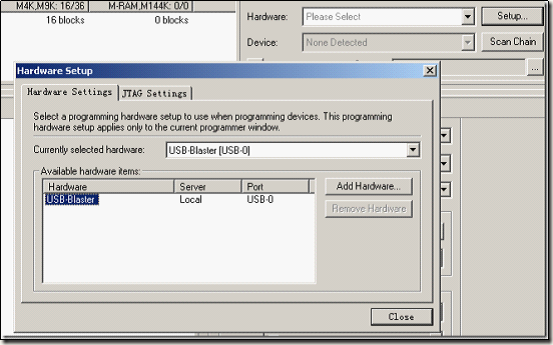

(11)設(shè)置Handware Setup,鏈接Device

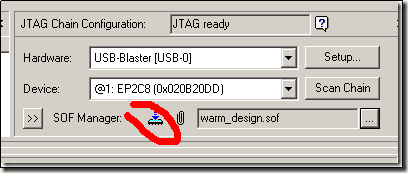

(12)Download sof文件(當(dāng)然也可以在Q II直接download)

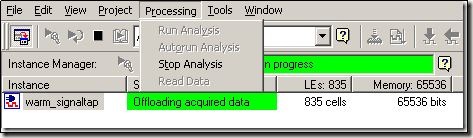

(13)進(jìn)程—Anturon Analysis,自動分析

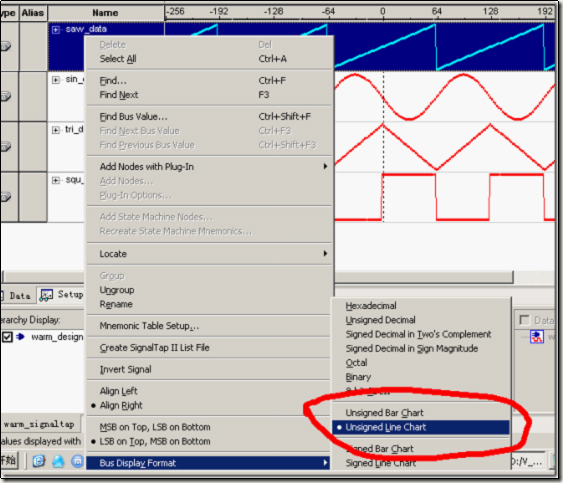

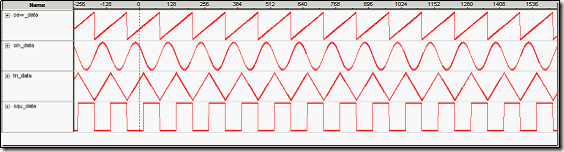

(14) 觀察輸出信號,設(shè)置為模擬信號,如下,方便觀察

(15)為什么可以那么帥。。。。

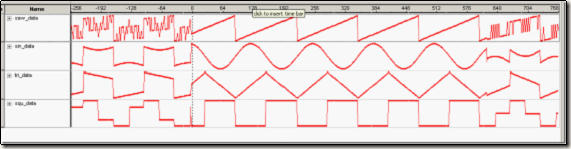

(16)實際測試到一段時間后,會出現(xiàn)bug,可能長時間采樣倒是邏輯邊沿不能對齊吧,畢竟沒那么完美,復(fù)位一下就好了。

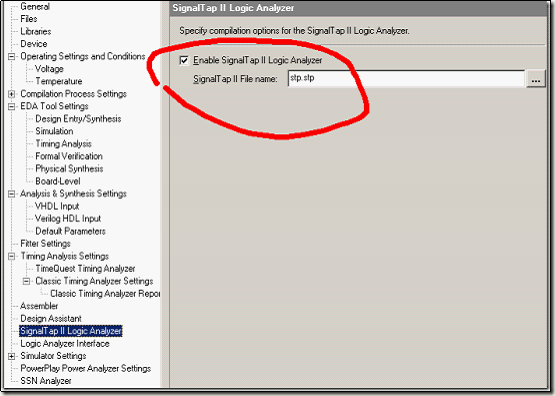

(17)測試ok 后,取消下圖中的enable SignalTap II Logic Analyzer ,減少邏輯單元,精簡成本設(shè)計: