TCP/IP是因特網(wǎng)上傳輸數(shù)據(jù)所必需的協(xié)議, 這種網(wǎng)絡(luò)通信模式在PC之間的實現(xiàn)已經(jīng)完善, 但是體積、價格等因素限制了其應(yīng)用的范圍。因此, 基于TCP/IP 協(xié)議與以太網(wǎng)的嵌入式系統(tǒng)網(wǎng)絡(luò)通信設(shè)計成為目前一個熱門的話題。本系統(tǒng)實現(xiàn)了在以TI公司的TMS320DM643" title="TMS320DM643">TMS320DM643為核心的嵌入式系統(tǒng)中,對數(shù)字電視傳輸流" title="數(shù)字電視傳輸流">數(shù)字電視傳輸流(TS)信號進行采集" title="采集">采集并在以太網(wǎng)中傳輸。利用本系統(tǒng)可輕松地實現(xiàn)在局域網(wǎng)中對數(shù)字電視傳輸流信號的傳輸、調(diào)度。數(shù)字電視傳輸流信號源是針對歐洲數(shù)字有線廣播系統(tǒng)標(biāo)準(zhǔn)(DVB-C)的數(shù)字有線電視信號。網(wǎng)絡(luò)接入硬件在以TMS320DM643為核心的嵌入式系統(tǒng)中實現(xiàn),網(wǎng)絡(luò)接入軟件采用了TI公司針對C6000系列DSP" title="DSP">DSP推出的TCP/IP NDK(Network Developer’s Kit)網(wǎng)絡(luò)開發(fā)包來實現(xiàn)。

系統(tǒng)電路設(shè)計

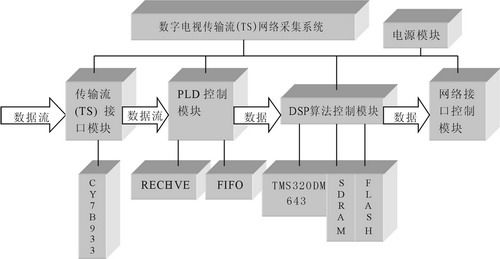

電路主要由5部分組成。數(shù)字電視傳輸流網(wǎng)絡(luò)采集系統(tǒng)框圖如圖1所示。

圖1 數(shù)字電視傳輸流網(wǎng)絡(luò)采集系統(tǒng)框圖

其主要功能是通過傳輸流接口模塊采集數(shù)字電視信號進入PLD(Cyclone EP1C6Q240C8)芯片,進行必要的處理后,將信號發(fā)送到DSP(TMS320DM643)芯片存儲起來,并進行算法處理。通過TMS320DM643對BCM5221進行必要的配置,將存儲在TMS320DM643內(nèi)的數(shù)據(jù)通過BCM5221傳送到局域網(wǎng)中,并通過計算機接收數(shù)據(jù)。

傳輸流接口模塊

傳輸流接口模塊由CY7B933輸入接口芯片及其電器接口電路組成。CY7B933輸入接口電路是點對點的傳輸模塊,可以通過光纖、同軸電纜和雙絞線進行高速的串行數(shù)據(jù)傳輸。輸入接口符合DVB-ASI的接口標(biāo)準(zhǔn)。輸入接口接收到串行位流后,通過內(nèi)部PLL時鐘同步恢復(fù)數(shù)據(jù)的時鐘信息,并對位流進行串并轉(zhuǎn)換、解碼和傳輸檢錯等操作。這種輸入接口能靈活地把高速點對點串行數(shù)據(jù)轉(zhuǎn)變成并行數(shù)據(jù),而且應(yīng)用領(lǐng)域廣泛,包括各種服務(wù)器、存儲器和視頻傳輸?shù)膽?yīng)用。

PLD控制模塊

在項目中,此部分硬件選用的是Altera公司的EP1C6Q240C8芯片。

此模塊的主要功能是實現(xiàn)與CY7B933接收芯片的接口,把數(shù)據(jù)從CY7B933接收進來,并緩存數(shù)據(jù)。這部分功能均由VHDL語言編寫的功能模塊實現(xiàn)。主要有兩個功能模塊:RECEIVE與FIFO。RECEIVE模塊主要負責(zé)從CY7B933接收數(shù)據(jù)字段;FIFO模塊主要負責(zé)緩存數(shù)據(jù)。

RECEIVE模塊

RECEIVE模塊的功能是實現(xiàn)與CY7B933接收芯片的接口,把數(shù)據(jù)從CY7B933接收進來。其工作方式是以一個傳輸流包為邊界接收數(shù)據(jù)的。

首先,RECEIVE模塊會檢測傳輸流包的邊界,通過查找包頭字節(jié)(固定為0x47)間的字節(jié)數(shù)來確定。因為包中數(shù)據(jù)也可能含有0x47,所以要犧牲3個包的數(shù)據(jù)來檢查3次。當(dāng)發(fā)現(xiàn)0x47這個字節(jié)的時候,就會觸發(fā)一個內(nèi)部的計數(shù)器開始計數(shù)。當(dāng)計數(shù)到188后,如果下一個字節(jié)又是0x47,說明傳輸流包屬于188個字節(jié)的包,那么計數(shù)器被清零;如果下一個字節(jié)又是0x47,說明傳輸流包屬于188個字節(jié)的包,那么計數(shù)器被清零,否則計數(shù)器清零并重新開始檢測邊界。

當(dāng)檢測到邊界以后,RECEIVE模塊開始接收數(shù)據(jù)包。計數(shù)器會從零開始計數(shù),在接收數(shù)據(jù)的過程中使能wrreq輸出有效信號,同時把數(shù)據(jù)輸出到下一級。當(dāng)計數(shù)到188時,表示一個數(shù)據(jù)包接收完成。當(dāng)一個包的數(shù)據(jù)接收完之后,計數(shù)器清零,并置ts188,保持高電平一個時鐘周期。下一個周期檢測數(shù)據(jù)是否為0x47,如果是,說明是下一個數(shù)據(jù)包的邊界;否則,說明出現(xiàn)了錯誤,并重新回到上一段所說的檢測數(shù)據(jù)包邊界的狀態(tài)。

此外,PLD模塊內(nèi)會有一個專用計數(shù)器記錄空包數(shù),當(dāng)接收到數(shù)據(jù)包后,會首先檢測此數(shù)據(jù)包是否為空包,如果是空包,PLD模塊會把這個空包刪除,并在計數(shù)器中加1。如果接收的不是空包,就會把計數(shù)器的值加到這個數(shù)據(jù)包的私有字段中,并緩存到FIFO。然后計數(shù)器自動清零。這樣處理數(shù)據(jù)包的目的是為了減少網(wǎng)絡(luò)傳輸?shù)臄?shù)據(jù)流量,從而可以傳輸更多的傳輸流數(shù)據(jù)。把計數(shù)器的值加入私有字段是為了在計算機接收到數(shù)據(jù)后,可以把原來的空包恢復(fù)出來,從而保證原傳輸流數(shù)據(jù)的完整性。

FIFO模塊

FIFO模塊的功能是從RECEIVE模塊接收數(shù)據(jù),并緩存起來。當(dāng)RECEIVE模塊接收完一個完整的傳輸流數(shù)據(jù)包之后,會發(fā)送ts188或ts204的中斷信號給DSP,DSP就會啟動EDMA功能從FIFO模塊接收數(shù)據(jù)。DSP與FIFO模塊采用異步連接的方式,具體的接收操作在DSP部分說明中再加以描述。

DSP算法處理模塊

此模塊主要由以TMS320DM643為核心的嵌入式系統(tǒng)組成。主要實現(xiàn)從PLD模塊接收傳輸流數(shù)據(jù)包,把數(shù)據(jù)包打包成TCP/IP格式,并實現(xiàn)對網(wǎng)絡(luò)接口(BCM5221)控制模塊的初始化,然后把數(shù)據(jù)包傳送到網(wǎng)絡(luò)模塊。

為了實現(xiàn)上述功能,必須建立起一套以TMS320DM643為核心的基本系統(tǒng)。

系統(tǒng)的具體配置

時鐘配置:EMIF內(nèi)核時鐘ECLKIN是133MHz。此外,系統(tǒng)的外設(shè)總線、EDMA傳輸和L2存儲器的工作時鐘為CPU內(nèi)核時鐘的1/2,即300MHz;片上定時器的工作時鐘為CPU內(nèi)核時鐘的1/8,即75MHz。

中斷配置:TMS320DM643除了RESET和NMI引腳提供外部不可屏蔽中斷請求輸入以外,還有兩個外部中斷引腳GP0[5]/EXT_INT5、GP0[7]/EXT_INT7,以提供可屏蔽的外部中斷請求輸入。系統(tǒng)中,EXT_INT5外部中斷用作PLD模塊的請求接收數(shù)據(jù)信號,每當(dāng)PLD模塊接收完一個傳輸流包,就會發(fā)送一個外部中斷信號給DSP,通知DSP接收數(shù)據(jù)。此外,EDMA中斷用于接收完一個包的數(shù)據(jù)后做后續(xù)處理。

系統(tǒng)對EMIF的使用情況:

系統(tǒng)在CE0空間擴展了4M×64bit的SDRAM存儲器(MT48LC4M32BPG),用于存儲程序與數(shù)據(jù)。SDRAM的工作時鐘由TMS320DM643的ECLKOUT1提供,與EMIF的工作時鐘頻率相同,本系統(tǒng)中默認ECLKIN為其時鐘源,即133MHz。

系統(tǒng)在CE1空間擴展了4M×8bit的Flash存儲器(Am29LV033C)。在對Flash進行讀/寫訪問前,需要通過EMIF的CE1控制寄存器CE1CTL,將CE1空間配置為8-bit異步存儲器接口,及讀/寫時序。

系統(tǒng)在CE2空間擴展了與FIFO模塊連接的接口。在DSP看來,F(xiàn)IFO模塊可視為8bit異步只讀存儲器。FIFO模塊的讀使能信號rdreq與TMS320DM643的CE2片選信號連接;FIFO模塊的讀時鐘信號rdclk與TMS320DM643的ARE讀使能信號連接。

以太網(wǎng)接口

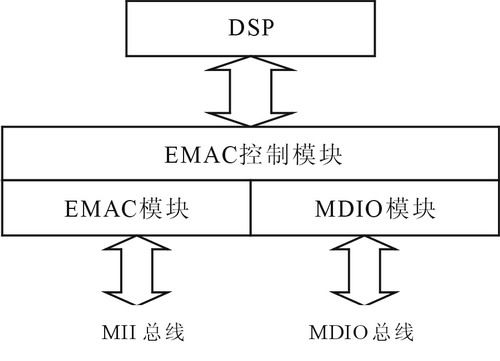

TMS320DM643上集成有一個EMAC+MDIO片上外設(shè),EMAC是Ethernet Media Access Controller的縮寫,即以太網(wǎng)媒體訪問控制器,MDIO是Management Data Input/Output的縮寫,即管理數(shù)據(jù)輸入/輸出模塊。EMAC+MDIO用于為以太網(wǎng)物理層(PHY)器件提供接口,其中,EMAC為接口以太網(wǎng)PHY提供數(shù)據(jù)通路,MDIO為接口以太網(wǎng)PHY提供管理信息通路。

TMS320DM643的網(wǎng)絡(luò)接口原理框圖如圖2所示。圖2描述了EMAC+MDIO與DSP中間有一個EMAC 控制模塊。它主要包含一些必備的、使EMAC更加有效使用DSP的存儲空間,控制其復(fù)位、中斷的一些邏輯。

這些寄存器的地址空間為:0x1C800000~0x1C803FFF。

圖2 TMS320DM643的網(wǎng)絡(luò)接口原理框圖

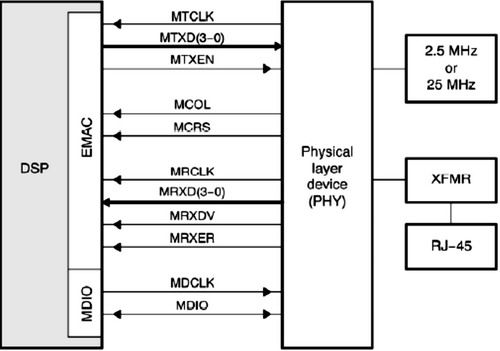

網(wǎng)絡(luò)接口控制模塊

本系統(tǒng)用Broadcom公司的BCM5221作為10/100Base-TX以太網(wǎng)收發(fā)器,BCM5221的MII接口與TMS320DM643的MII接口對接。具體接口如圖3所示。RJ45連接器選用AMP公司的406549-1,其上帶兩個LED指示燈,右邊的LED為綠色,用作指示連接狀態(tài)。左邊的為黃色,正常情況下用來指示數(shù)據(jù)傳輸。

圖3 TMS320DM643與PHY設(shè)備連接框圖

電源模塊

系統(tǒng)包括4組電源:系統(tǒng)外接穩(wěn)壓電源,把220V的交流電源電壓轉(zhuǎn)換成5V直流電壓;PLD模塊電源由兩種電源供電,分別是3.3V和1.5V;TMS320DM643需要兩種電源,分別為CPU核心和周邊的I/O接口供電。周邊I/O電壓要求3.3V,CPU核心電壓只要1.4V;網(wǎng)絡(luò)接口控制模塊采用3.3V電源供電。

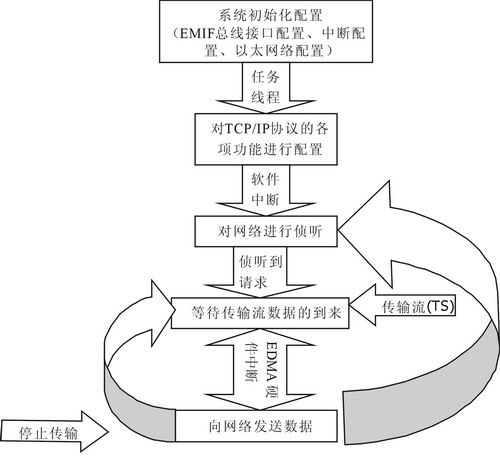

系統(tǒng)軟件設(shè)計

htons(1000),在這里設(shè)置端口號為1000,當(dāng)然也可以設(shè)置其他的端口號。然后把端口號與報路對象綁定bind( stcp, (PSA) &sin1, sizeof(sin1)。最后進入偵聽狀態(tài)listen( stcp, 1)。