由于手機(jī)電視將為2008北京奧運(yùn)提供服務(wù),國(guó)內(nèi)多家單位已積極致力于DAB的研制開(kāi)發(fā),。本文將介紹DAB接收機(jī)的樣機(jī)設(shè)計(jì),。

系統(tǒng)的性能要求

歐洲D(zhuǎn)AB系統(tǒng)規(guī)定了4種模式,本設(shè)計(jì)采用的是第1種模式,,具體參數(shù)如表1所示,。其中,L表示一幀的符號(hào)數(shù),,K表示每個(gè)符號(hào)的子載波個(gè)數(shù),,TF表示一幀的持續(xù)時(shí)間,TNULL表示空符號(hào)持續(xù)時(shí)間,,Ts表示每個(gè)符號(hào)的持續(xù)時(shí)間,,Tu表示有效符號(hào)的持續(xù)時(shí)間,Δ表示保護(hù)間隔的持續(xù)時(shí)間,。

|

|

表1 第1種DAB傳輸模式的具體參數(shù) |

采用這一模式的設(shè)計(jì)要求為:帶寬1.536MHz,,載波頻率174~240MHz,誤碼率不超過(guò)10-4,。

方案原理及設(shè)計(jì)思路

1 方案原理框圖

DAB接收機(jī)原理框圖如圖1所示,。DAB接收機(jī)將從天線接收到的信號(hào)經(jīng)過(guò)高頻頭轉(zhuǎn)為中頻模擬信號(hào),放大后進(jìn)行A/D變換,,得到數(shù)字信號(hào),。其中A/D采樣時(shí)鐘受晶振VCXO的控制,采樣時(shí)鐘偏移由采樣時(shí)鐘同步部分估計(jì)得到,。A/D轉(zhuǎn)換后的數(shù)據(jù)一路做AGC檢測(cè)去控制高頻頭的輸出,,另一路經(jīng)過(guò)R/C變換成FFT所需要的兩路實(shí)虛部數(shù)據(jù)信號(hào)。時(shí)間同步部分估計(jì)得到一個(gè)時(shí)域符號(hào)的同步頭,,并粗略地估計(jì)由于收發(fā)頻率不一致而引起的頻偏,。經(jīng)過(guò)FFT變換后,頻率同步單元定出FFT的窗口位置,,校正帶有頻偏的數(shù)據(jù),。校正后的數(shù)據(jù)經(jīng)過(guò)信道估計(jì),得到當(dāng)前實(shí)時(shí)的信道響應(yīng),,經(jīng)過(guò)信道均衡處理以消除信道多徑衰落的影響,,然后再經(jīng)過(guò)解映射軟判決譯碼和解擾,然后將音頻信號(hào)送入信道解碼器解碼,,接著進(jìn)行信源解碼和音頻綜合,,最后經(jīng)D/A還原成模擬音頻?

|

|

圖1 接收機(jī)原理框圖 |

2 方案的設(shè)計(jì)思路

DAB接收機(jī)主要由數(shù)字下變頻、同步,、OFDM" title="OFDM">OFDM解調(diào)和Viterbi譯碼四大部分構(gòu)成,。

數(shù)字下變頻就是把ADC" title="ADC">ADC輸出的中頻數(shù)字信號(hào)變?yōu)閿?shù)字基帶信號(hào),也就是在數(shù)字上實(shí)現(xiàn)頻譜的下搬移,主要包括希爾伯特變換,、頻譜下搬移及降采樣等,。

同步部分按功能包括符號(hào)定時(shí)同步、載波頻率同步和采樣時(shí)鐘頻率同步,,以FFT為界可以分為時(shí)域同步和頻域同步兩部分,。

OFDM解調(diào)包括FFT和差分解調(diào)等,經(jīng)FFT和差分解調(diào)后的數(shù)據(jù)再經(jīng)過(guò)頻域解交織后進(jìn)行QPSK解映射及量化,,送給后續(xù)Viterbi譯碼器進(jìn)行軟判決譯碼,。

對(duì)OFDM解調(diào)送來(lái)的數(shù)據(jù)提取快速信息信道(FIC)數(shù)據(jù)進(jìn)行解收縮、Viterbi譯碼,、解擾,,得到復(fù)合結(jié)構(gòu)信息(MCI),再利用MCI對(duì)主業(yè)務(wù)信道(MSC)數(shù)據(jù)進(jìn)行譯碼,。

DAB接收機(jī)硬件電路設(shè)計(jì)

1 方案結(jié)構(gòu)框圖

根據(jù)對(duì)DAB接收機(jī)組成部分的分析,,本次設(shè)計(jì)采用FPGA" title="FPGA">FPGA+DSP" title="DSP">DSP的設(shè)計(jì)方案,DAB接收機(jī)完整的結(jié)構(gòu)框圖如圖2所示,。DAB信號(hào)從天線接收后進(jìn)入高頻頭部分,,選出所需的頻率塊,然后將選出的高頻信號(hào)送入混頻器,,變?yōu)橹行念l率為38.912MHz,、帶寬為1.536 MHz的中頻信號(hào),中頻信號(hào)濾掉無(wú)用的頻譜部分后再經(jīng)頻率變換和濾波,,變?yōu)橹行念l率為2.048 MHz,、帶寬為1.536MHz的基帶信號(hào)。然后進(jìn)入ADC,,采樣速率為8.192MHz,,轉(zhuǎn)換成數(shù)字信號(hào)后進(jìn)入FPGA。FPGA完成并串轉(zhuǎn)換,,同步和解調(diào),,以及VCXO所需的控制電路等。處理后的數(shù)據(jù)進(jìn)入DSP,,DSP外部時(shí)鐘為24.5MHz,,所以DSP可進(jìn)行4倍頻,工作于100MHz,。DSP中完成解交織,、Viterbi譯碼、解擾以及音頻解碼,,最后數(shù)據(jù)被送入DAC" title="DAC">DAC,恢復(fù)出原始模擬信號(hào),送入喇叭即可收聽(tīng),。

|

|

圖2 接收機(jī)的結(jié)構(gòu)框圖 |

2 器件的選型

器件的選型要求在滿足系統(tǒng)需求的情況下力爭(zhēng)使成本最低,,功耗最小,設(shè)計(jì)方便且易于調(diào)試,,所以要全面兼顧芯片的運(yùn)算速度,、價(jià)格、硬件資源,、運(yùn)算精度,、功耗以及芯片的封裝形式、質(zhì)量標(biāo)準(zhǔn),、供貨情況和生命周期等,。綜合考慮以上幾方面因素,本次設(shè)計(jì)中ADC選用TLV5535,,DAC選用AKM4352,,F(xiàn)PGA選用EP1S40,DSP選用TMS320VC5510,。

TLV5535是一款性能優(yōu)良的8位ADC,,具有35MSPS的采樣速率,3.3V單電源供電,,典型功耗只有90mW,,模擬輸入帶寬達(dá)600MHz,很適合本設(shè)計(jì),。AKM4352是非常適合便攜式音頻設(shè)備的DAC,,帶寬20kHz,采樣速率8~50kHz,,工作電壓為1.8~3.6V,,通帶波動(dòng)只有±0.06dB,阻帶衰減達(dá)43dB,,性能非常優(yōu)良,。TMS320VC5510是TI公司的一款高性能、低功耗DSP,。它具有很高的代碼執(zhí)行效率,,其最高指令執(zhí)行速度可達(dá)800MIPS,雙MAC結(jié)構(gòu),,可設(shè)置的指令高速緩沖存儲(chǔ)器容量為24KB,,片上RAM共160K×16b,此外還有3組多通道緩沖串行口和可編程的數(shù)字鎖相環(huán)發(fā)生器等,,I/O電壓 3.3V,,內(nèi)核電壓1.6V,。EP1S40是ALTERA公司Stratix系列FPGA,具有非常高的內(nèi)核性能,、存儲(chǔ)能力,、架構(gòu)效率,提供了專用的功能用于時(shí)鐘管理和數(shù)字信號(hào)處理應(yīng)用及差分和單端I/O標(biāo)準(zhǔn),,此外還具有片內(nèi)匹配和遠(yuǎn)程系統(tǒng)升級(jí)能力,,功能豐富且功耗較小。EP1S40的片內(nèi)資源也足以滿足本設(shè)計(jì)所需,。

3 主要模塊的電路設(shè)計(jì)

ADC與FPGA相連,,并在FPGA內(nèi)完成并串變換,譯碼電路也由FPGA來(lái)完成,。FPGA與ADC間的連接包括數(shù)據(jù)線和時(shí)鐘線,,ADC的時(shí)鐘由FPGA來(lái)提供,數(shù)據(jù)線和時(shí)鐘線均與FPGA的I/O引腳直接相連即可,,如圖3所示,。

|

|

圖3 ADC與FPGA連接原理圖 |

DSP通過(guò)異步串行口與DAC連接,如圖4所示,,DAC輸出的模擬信號(hào)經(jīng)濾波后可直接輸出語(yǔ)音信號(hào),。

|

|

圖4 DSP與DAC連接原理圖 |

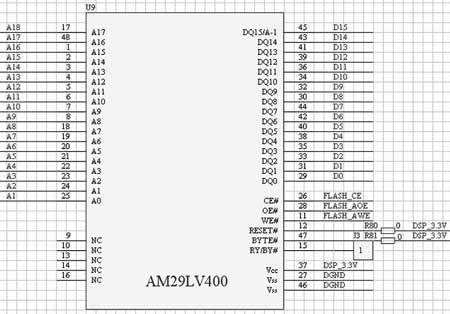

現(xiàn)今的高速DSP內(nèi)存不再基于Flash,而是采用存取速度更快的RAM,。DSP掉電后其內(nèi)部RAM中的程序和數(shù)據(jù)將全部丟失,,所以在脫離仿真器的環(huán)境中,DSP芯片每次上電后必須自舉,,將外部存儲(chǔ)區(qū)的執(zhí)行代碼通過(guò)某種方式搬移到內(nèi)部存儲(chǔ)區(qū),,并自動(dòng)執(zhí)行。常用的自舉方式有并行自舉,、串行自舉,、主機(jī)接口(HPI)自舉和I/O自舉。HPI自舉需要有一個(gè)主機(jī)進(jìn)行干預(yù),,雖然可以通過(guò)這個(gè)主機(jī)對(duì)DSP內(nèi)部工作情況進(jìn)行監(jiān)控,,但電路復(fù)雜、成本高,;串行自舉代碼加載速度慢,;I/O自舉僅占用一個(gè)端口地址,代碼加載速度快,,但電路復(fù)雜,,成本高;并行自舉加載速度快,,雖然需要占用DSP數(shù)據(jù)區(qū)的部分地址,,但無(wú)須增加其他接口芯片,,電路簡(jiǎn)單。因此在TI公司的5000系列DSP中得到了廣泛應(yīng)用,,本次設(shè)計(jì)也是采用并行自舉,。與傳統(tǒng)的EEPROM相比,,F(xiàn)lash具有支持在線擦寫且擦寫次數(shù)多,、速度快、功耗低,、容量大和價(jià)格低廉等優(yōu)點(diǎn),。目前在很多Flash芯片采用3.3V單電源供電,與DSP連接時(shí)無(wú)須采用電平轉(zhuǎn)換芯片,,因此電路連接簡(jiǎn)單,。在系統(tǒng)編程時(shí),利用系統(tǒng)本身的DSP直接對(duì)外掛的Flash編程,,節(jié)省了編程器的費(fèi)用和開(kāi)發(fā)時(shí)間,,使得DSP執(zhí)行代碼可以在線更新。圖5為外部程序數(shù)據(jù)存儲(chǔ)器Flash的電路連接,。

|

|

圖5 外部程序數(shù)據(jù)存儲(chǔ)器Flash的電路連接 |

FPGA與DSP通過(guò)McBSP,、GPIO" title="GPIO">GPIO、EMIF和EHPI口相連,,接口種類多,,便于根據(jù)需要靈活使用。FPGA內(nèi)的程序和數(shù)據(jù)掉電后也會(huì)全部丟失,,所以為其配備了專用配置芯片EPC16,,上電后自動(dòng)將程序下載到FPGA中,簡(jiǎn)單易用,。

總結(jié)

為了方便調(diào)試,,本次設(shè)計(jì)十分靈活,留的系統(tǒng)資源也比較多,,不僅可以實(shí)現(xiàn)模式1,,其他三種模式也可以在此硬件平臺(tái)上實(shí)現(xiàn)。用來(lái)存儲(chǔ)程序和數(shù)據(jù)的Flash既可以用FPGA來(lái)讀寫,,也可以用DSP來(lái)讀寫,。DSP和FPGA分別配了JTAG下載口用于下載程序和檢測(cè)芯片。DSP還連接RS232,,用于發(fā)出控制指令以及監(jiān)控DSP內(nèi)部情況,。FIC解碼完成后可進(jìn)行DAB/DMB的業(yè)務(wù)選擇,依據(jù)選擇業(yè)務(wù)的不同進(jìn)行不同的處理后分別產(chǎn)生聲音和圖像信號(hào),,并分別從喇叭或液晶顯示器輸出,。