引 言

隨著科技的不斷發(fā)展,集成電路的制造工藝和設計水平得到了飛速提高,設計者能夠將非常復雜的功能集成到硅片上。將PCB板上多塊芯片的系統(tǒng)集成到一塊芯片內部,這個芯片就是系統(tǒng)級芯片,即SoC(System on Chip)。SoC芯片的特點主要有兩方面:第一是其高度的復雜性,第二是大量運用可重用的IP(Intellectual Property)模塊。以往的芯片設計往往只專注于某個特定功能的模塊設計,例如壓縮/解壓、無線模塊、網(wǎng)絡模塊等。而一塊SoC芯片的功能可能是多個獨立模塊的總和。另外,芯片的制造需要經(jīng)歷化學、冶金、光學等工藝過程,在這些過程中可能引入物理缺陷導致其不能正常工作。因此對芯片的測試成為必不可少的環(huán)節(jié)。可測性設計(Design ForTest,DFT)是在芯片的設計階段就考慮以后測試的需要,使芯片測試更加容易和充分,并降低測試成本。一個SoC包含各種可復用的功能IP核,其中嵌入式微處理器核是其中的關鍵部分,大部分都嵌有一個或多個微處理器核以獲得最好的性能。所以,對微處理器核可測性問題的研究越來越迫在眉睫。

1 傳統(tǒng)測試方法

20世紀七八十年代之前,集成電路還都是小規(guī)模電路時,測試大都通過加入激勵,探測相應的方式來完成。這種方式在電路規(guī)模不大并且頻率不快的情況下還是可行的,但是隨著集成電路規(guī)模的增長,功能驗證內容增多,或者需要使用異步激勵信號時,這樣的測試方式就存在局限性。為了提高故障點的測試覆蓋率,出現(xiàn)了自動向量生成(ATPG)工具。運用ATPG算法以及強大的計算機,可以檢測到盡可能多的故障點。隨著芯片規(guī)模的增長,芯片門數(shù)相對于引腳數(shù)目的比例變得太懸殊,只通過輸入/輸出引腳進行測試的方法幾乎不能再應用了,于是出現(xiàn)了另外一種基于掃描的測試技術——DFT。但當掃描鏈很長而且數(shù)量很多時,單芯片測試時間還是很長。同時高級測試儀器的價格急速攀升,使得BIST(Built-In Self-Test)即片內測試方法的產(chǎn)生成為必然。

2 幾種常用的BIST方法及其優(yōu)缺點

片內測試是節(jié)省芯片測試時間和成本的有效手段,外部測試的測試速度以每年12%的幅度增長,而片內芯片的速度以每年30%的幅度增長,這一矛盾進一步推動了BIST的應用。由于SoC芯片內部的IP種類繁多,對不同的IP核采用不同的BIST測試方法。采用BIST技術的優(yōu)點在于:降低測試成本、提高錯誤覆蓋率、縮短測試時間、方便客戶服務和獨立測試。目前BIST測試方法主要有MemBIST和LogicBIST。

2.1 MemBIST

MemBIST是面向嵌入式芯片存儲器的測試方式,用于測試存儲器工作是否正常。芯片內部有一個BISTController,用于產(chǎn)生存儲器測試的各種模式和預期的結果,并比較存儲器的讀出結果和預期結果。MemBIST可分為RAMBIST和ROMBIST。目前較常用的存儲器BIST算法有March算法及其變種。業(yè)界常用的工具有Mentor Graphics的MBIST Architecture。

2.1.1 RAMBIST測試結構

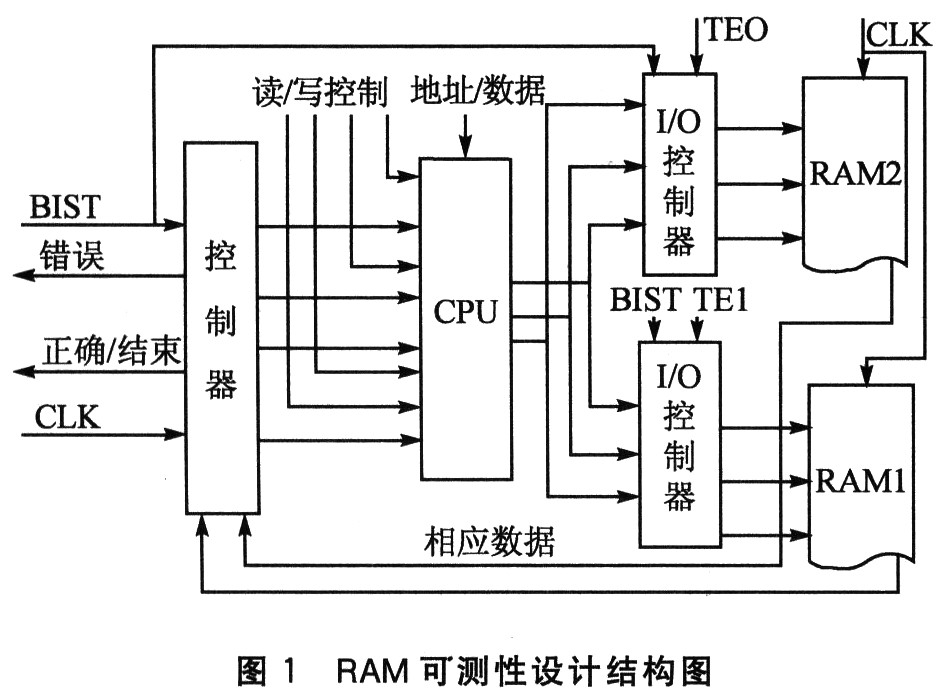

用RAM實現(xiàn)的數(shù)據(jù)Cache和指令Cache均使用普通的BIST方法。因為這兩個RAM的結構完全相同,因此為了減少面積消耗,只使用一組測試電路。在測試時有外部信號TE0、TE1分別控制RAM1、RAM2是否處于測試狀態(tài),TE0、TE1不能同時有效。測試電路結構如圖1所示。

控制器在外部輸入信號BIST的控制下,產(chǎn)生讀寫控制信號、訪問地址和測試碼,對RAM的相應數(shù)據(jù)進行壓縮分析,并將得到的特征值與存放在芯片中的標準特征值比較。通過兩個I/O口報告測試結果,還實現(xiàn)了初步的故障診斷功能。當發(fā)現(xiàn)有故障時,通過TAP控制器,可以將出錯的地址移出芯片,為進一步的故障診斷和修復提供信息。

2.1.2 ROMBIST測試結構

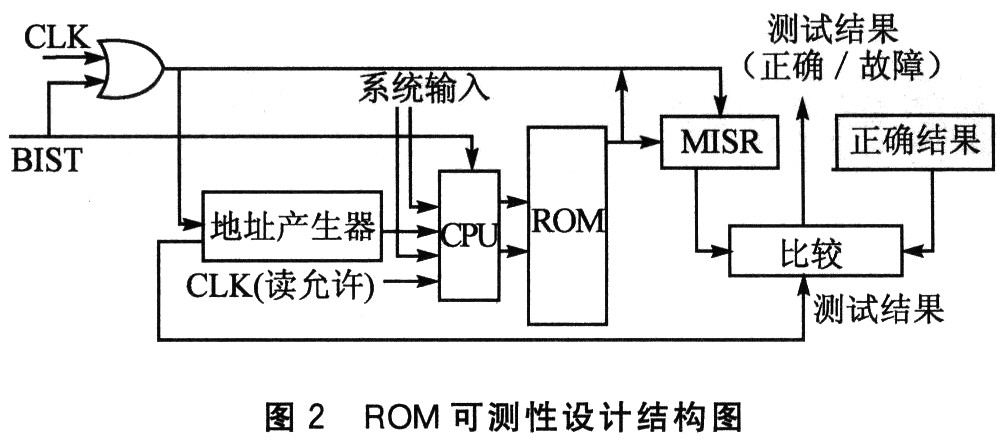

通常使用循環(huán)冗余校驗(CRC)電路實現(xiàn)ROM的測試,這種方法雖然測試結果很可靠,但是需要逐位讀取信息,而對ROM的訪問是每次32位,如果使用該方法則需要一個緩沖機制,并且速度會很慢。在此仍使用RAM測試中并行的數(shù)據(jù)壓縮,故障覆蓋率能夠達到要求,測試電路也比CRC電路簡單。測試電路如圖2所示。

BIST測試信號由TAP控制器的TDT口輸入,是整個測試電路的使能信號,測試過程經(jīng)過觸發(fā)后,完全在電路內部完成,結束后通過一個I/O口報告測試結果。多輸入寄存器(MISR)作為TAP控制器的數(shù)據(jù)寄存器,測試初始化時設置為初始狀態(tài)。

2.2 LogicBIST

LogicBIST方法是利用內部的向量產(chǎn)生器逐個地產(chǎn)生測試向量,將它們施加到被測電路上,然后經(jīng)過數(shù)字壓縮和鑒別產(chǎn)生一個鑒別碼,將這個鑒別碼同預期值進行比較。LogicBIST通常用于測試隨機邏輯電路,一般采用偽隨機測試圖形生成器來產(chǎn)生輸入測試圖形,應用于器件內部機制;采用MISR作為獲得輸出信號產(chǎn)生器。由于MI-SR的結構和多輸入序列的鑒別碼的固有特點,這是一個多對一的映射關系。不同的輸入序列通過MISR之后可能產(chǎn)生相同的鑒別碼,這被稱之為alias。

LogicBIST測試只能得到芯片能否通過測試的結果。一旦芯片不能通過測試,該如何確定芯片內部的故障點在何處呢?這就是診斷工作,不過LogicBIST對故障診斷的支持太弱,如果一塊芯片未能通過,單單憑錯誤的鑒別碼是很難確定故障點在何處的。有時會出現(xiàn)芯片內部多個故障點的共同作用使得鑒別碼反而是正確的現(xiàn)象,這被稱之為漏測試。它產(chǎn)生的概率非常小,也有算法來盡量減小漏測試發(fā)生的概率。其中一種方法是將正確的序列輸入,和正確的鑒別碼作單一映射,其他的錯誤輸人一定得到錯誤的鑒別碼。這種方法對MISR、PRRG以及CUT都需要具體分析,以改變其結構或者PRPG的生成順序。

結 語

本文介紹了SoC片上嵌入式微處理器核可測性技術的研究現(xiàn)狀;介紹了設計時在電路中植入相關功能電路,用于提供自我測試功能的技術,以降低器件測試對自動測試設備(ATE)的依賴程度。BIST技術可以實現(xiàn)自我測試,也可以解決很多電路無法直接測試的問題(因為它們沒有外部引腳)。

可以預見,在不久的將來即使最先進的ATE也無法完全測試最快的電路,這也是采用BIST的原因之一。但是BIST也存在一些缺點,如額外的電路會占用寶貴的面積,會產(chǎn)生額外的引腳和可能出現(xiàn)測試盲點等。BIST技術正成為高價ATE的替代方案,但是目前還無法完全取代ATE,他們將在未來很長一段時間內共存。