隨著工業(yè)技術(shù)進(jìn)步,對數(shù)字控制伺服系統(tǒng)中執(zhí)行效率和集成化程度的要求越來越高。比如用單處理器控制多個伺服系統(tǒng)時,對多通道A/D轉(zhuǎn)換的效率要求較高。以往較多地使用多路模擬開關(guān)與單通道A/D轉(zhuǎn)換器來實(shí)現(xiàn),效率較低,使用模擬開關(guān)帶來的噪聲也比較嚴(yán)重。在此,選用串行多通道A/D轉(zhuǎn)換器AD7890與TMS320F2812處理器的SPI接口組成A/D轉(zhuǎn)換模塊,非常適合應(yīng)用于多軸伺服系統(tǒng)。AD7890是一款8通道12位串行A/D轉(zhuǎn)換器,具有高轉(zhuǎn)換效率(轉(zhuǎn)換時間僅為5.9μs)、高速靈活的串行接口、多通道等優(yōu)點(diǎn)。其中,AD7890-10輸入電壓范圍為-10~+10 V。TMS320F2812處理器上集成了多種先進(jìn)的外設(shè),為實(shí)現(xiàn)電機(jī)及其他運(yùn)動控制領(lǐng)域的應(yīng)用提供了良好的平臺,它所提供的SPI接口通常用于DSP處理器和外部設(shè)備及其他處理器之間的通信。SPI分主、從兩種工作方式,數(shù)據(jù)長度可編程(1~16 b),并能同時進(jìn)行接收和發(fā)送操作,通常用于DSP處理器和外部外設(shè)以及其他處理器之間的通信,這使它能很方便地與AD7890采用主/從模式進(jìn)行通信。

1 AD7890工作模式和原理

AD7890的SMODE引腳是工作模式控制輸入端,它決定了器件是工作于外部時鐘模式(作為從設(shè)備),還是內(nèi)部時鐘模式(作為主設(shè)備)。當(dāng)SMODE置于高電平時,器件工作在外部時鐘模式,由主設(shè)備提供時鐘信號SCLK和接收幀同步信號RFS,AD7890可接收的最大串行時鐘頻率達(dá)10 MHz;當(dāng)SMODE置于低電平時,器件工作在內(nèi)部時鐘模式,自身提供時鐘信號SCLK和接收幀同步信號RFS,其時鐘頻率由CLK引腳輸入時鐘頻率決定。本文以DSP作為主控制器,AD7890作為從設(shè)備,由DSP的SPI口提供串行時鐘。

AD7890通過片內(nèi)高速雙向串行數(shù)據(jù)接口接收控制字和輸出轉(zhuǎn)換結(jié)果。通過向控制寄存器寫數(shù)據(jù)可以確定轉(zhuǎn)換通道、轉(zhuǎn)換開始信號等信息。其控制寄存器包含5位數(shù)據(jù),因此至少需要6個SCLK脈沖才能完成對寄存器的寫操作。其中,A2,A1,A0分別為通道地址選擇最高位、次高位、最低位。通道選擇算法為:通道號=4A2+2A1+A2+1。發(fā)送數(shù)據(jù)的第5個SCLK脈沖下降沿過后的數(shù)據(jù)均為無效數(shù)據(jù)。控制字寫入寄存器后,器件即啟動內(nèi)部延時脈沖,保證在轉(zhuǎn)換開始前跟蹤/保持器有足夠的時間來完成轉(zhuǎn)換通道的建立和切換。該延時脈沖寬度取決于引腳電容的CEXT值。一般引腳電容值取CEXT、120 pF或200 pF。據(jù)測試,此時延時脈沖寬度分別約為7.Oμs和9.6μs。向控制寄存器寫數(shù)據(jù)時CEXT,引腳電平由低變高,電容在第6個時鐘脈沖的下降沿開始放電,電壓降低至2.5 V以下時內(nèi)部延時脈沖結(jié)束,同時A/D轉(zhuǎn)換開始,5.9μs后轉(zhuǎn)換結(jié)束。若此時串行讀操作已完成,且RFS已變高為高電平,則用新的轉(zhuǎn)換結(jié)果更新輸出寄存器。至此,一次A/D轉(zhuǎn)換結(jié)束。圖1為AD7890工作原理圖,從示波器獲取的圖片顯示了CEXT引腳電平、SCLK脈沖與A/D轉(zhuǎn)換過程時間的關(guān)系。

2 AD7890工作時序與讀寫操作方法

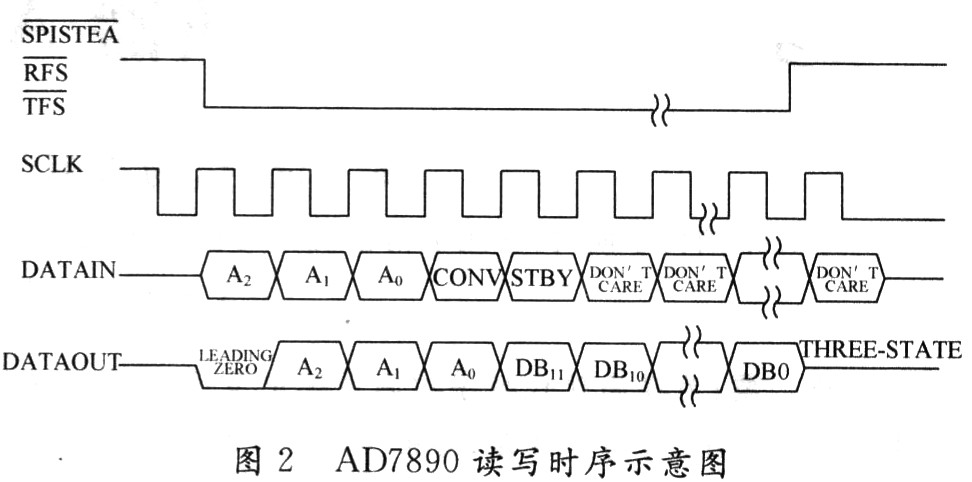

控制AD7890的轉(zhuǎn)換開始有兩種方法。一是,硬件控制,即將CONVST引腳置低,器件產(chǎn)生一個窄低電平脈沖,在脈沖的上升沿A/D轉(zhuǎn)換開始,前提是須向CONV位寫0;二是,軟件控制,即向控制寄存器的cONV位寫1,此時CONVST引腳不起作用。二者區(qū)別在于,采用硬件控制轉(zhuǎn)換開始時,在CONVS麗上升沿啟動轉(zhuǎn)換,此時必須保證內(nèi)部延時脈沖已經(jīng)結(jié)束;對于軟件控制,內(nèi)部延時脈沖結(jié)束時轉(zhuǎn)換立即開始。需要說明的是,在向控制寄存器寫數(shù)據(jù)時,6個寫操作時鐘脈沖結(jié)束前,發(fā)送幀同步信號TFS必須保持低電平,否則寫操作不能成功。而讀取A/D轉(zhuǎn)換結(jié)果期間,接收幀同步信號RFS必須保持低電平。RFS和TFS連在一起,使SPI口的讀、寫操作同時進(jìn)行。以DSP作為主設(shè)備,AD7890作為從設(shè)備,即工作在外部時鐘模式下,此時讀、寫操作時序分別如圖2所示。DSP的SPISTE麗引腳具有從設(shè)備片選功能,該引腳為低時可向從設(shè)備發(fā)送數(shù)據(jù),文中將該引腳作為通用收、發(fā)幀同步信號來控制RFS和TFS。

3 AD7890與TMS320F2812的SPI接口硬件實(shí)現(xiàn)

TMS320F2812是TI公司推出的數(shù)字信號處理器,它在電機(jī)控制方面性能優(yōu)越,使其在工業(yè)控制中得到了非常廣泛的應(yīng)用。它所提供的串行外設(shè)接口(SPI)是一個高速同步的串行輸入/輸出口,包含4個外部引腳:從輸出/主輸入引腳(SPISOMI)、從輸入/主輸出引腳(SPISIMO)、從發(fā)送使能引腳(SPISTE)、串行時鐘引腳(SPICLK)。SPI主要特點(diǎn)是可以同時發(fā)送和接收串行數(shù)據(jù);可以當(dāng)作主機(jī)或從機(jī)工作;提供頻率可編程時鐘;發(fā)送結(jié)束中斷標(biāo)志。

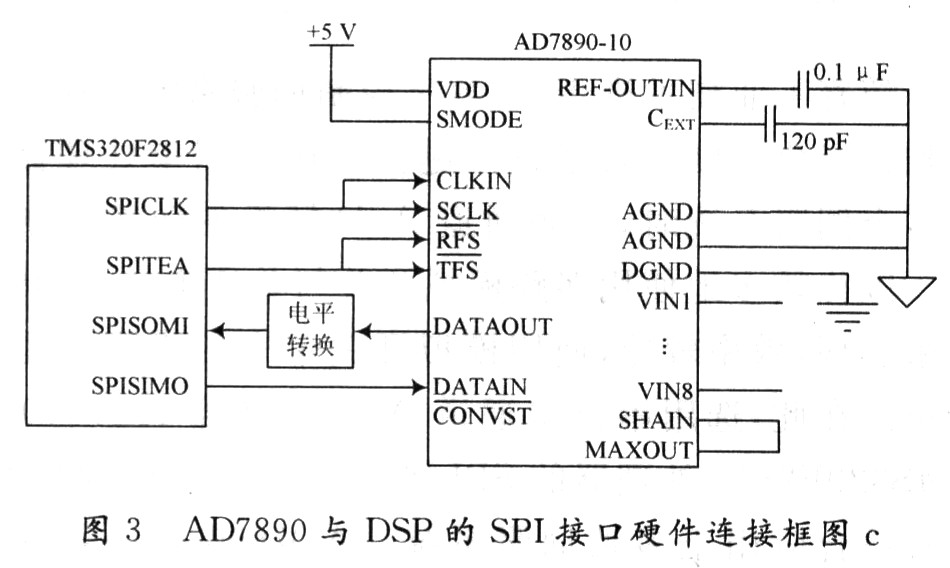

確定DSP的低速外設(shè)時鐘LSPCLK后,通過波特率控制寄存器SPIBRR,確定波特率SCLK。波特率具體計算方法是:當(dāng)SPIBRR=3~127時,SCLK=LSPCLK/(SPIBRR+1);當(dāng)SPIBRR=0,1,2時,SCLK=LSPCLK/4,因此共具有125種可編程波特率。文中,DSP的工作頻率為120 MHz,低速時鐘LSPCLK為30 MHz,故可編程波特率范圍為234.375 kb/s~7.5 Mb/s。通過提高系統(tǒng)低速時鐘,可以提高可編程波特率范圍;通過選較高的波特率,能提高數(shù)據(jù)傳輸速率,即提高A/D的轉(zhuǎn)換效率。AD7890-10與TMS320一F2812的SPI接口硬件連接框圖如圖3所示。

由于AD7890-10數(shù)據(jù)電平為5 V,而TMS320F2812的I/O所能承受的電壓最高為3.3 V,因此必須對A/D轉(zhuǎn)換結(jié)果進(jìn)行電平轉(zhuǎn)換,將其轉(zhuǎn)換為I/0口可承受的電壓。把5 V電平轉(zhuǎn)為3.3 V電平有多種方法。常用的有兩種。一是選用專門的電平轉(zhuǎn)換器件,如TI公司的SN74I.VTHl6245;二是把A/D轉(zhuǎn)換結(jié)果通過系統(tǒng)中CPLD的I/O口再輸出到DSP,前提是所選CPLD可承受輸入電壓為5 V,而輸出為3.3 V。本文采用后一種方法,選用的是Altera公司的EPM7128ST1100-10,給CPLD的I/O口供3.3 V電源即可滿足要求。將A/D數(shù)據(jù)通過一個CPLD的一個I/O口轉(zhuǎn)接,經(jīng)軟件進(jìn)行邏輯處理后輸出至DSP即可。需要注意的是,為避免噪聲干擾,AD7890的所有未用引腳不能懸空,必須接可承受范圍內(nèi)的固定電平。實(shí)驗(yàn)表明,特別是CLKIN引腳不能懸空,否則可能導(dǎo)致A/D轉(zhuǎn)換不能成功。對于AD7890-10,當(dāng)未使用的輸入通道電壓值低于-12 V時會對所選其他通道的轉(zhuǎn)換造成嚴(yán)重干擾。文中采取的方法是將外部時鐘輸入引腳SCLK與內(nèi)部時鐘輸入引腳CLKIN相連,可以有效去除干擾。

4 軟件讀寫實(shí)現(xiàn)

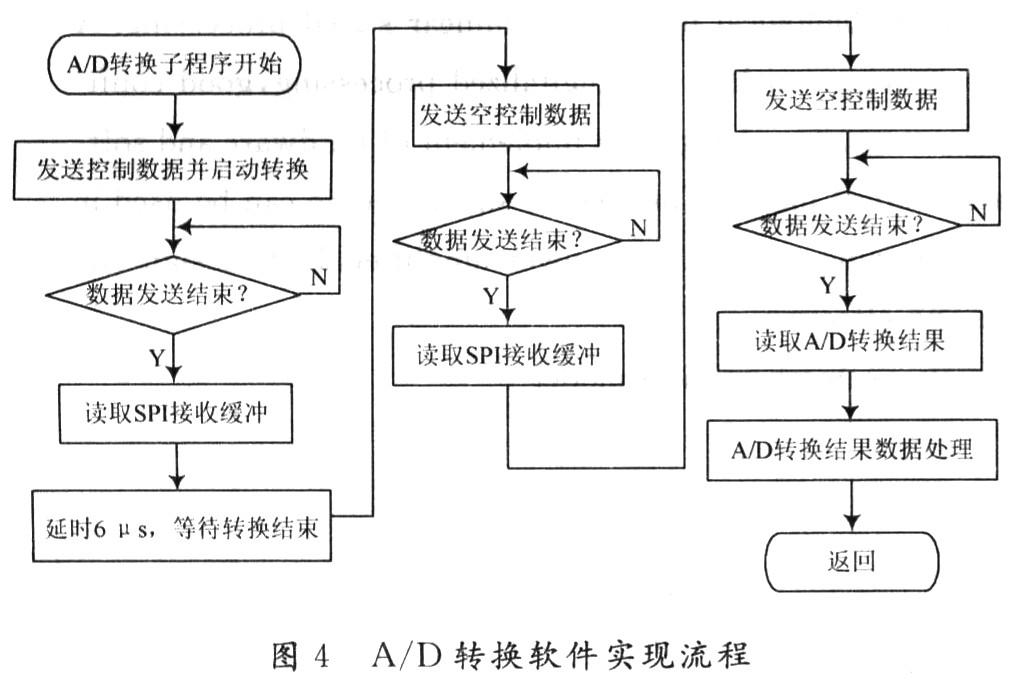

對于SPI接口而言,數(shù)據(jù)與串行時鐘脈沖是同時產(chǎn)生的,即只有數(shù)據(jù)線上有數(shù)據(jù)傳送時才產(chǎn)生時鐘脈沖。所以發(fā)送控制數(shù)據(jù)結(jié)束后,DSP收到的數(shù)據(jù)并不是真實(shí)的A/D轉(zhuǎn)換結(jié)果,但需要讀取接收緩沖寄存器數(shù)據(jù)使SPI復(fù)位。多次實(shí)驗(yàn)表明,對于單次A/D轉(zhuǎn)換,在轉(zhuǎn)換結(jié)束后需要再向AD7890發(fā)送2次空控制數(shù)據(jù)0x0000,之后DSP的SPI接收緩沖寄存器中的數(shù)據(jù)才是正確的A/D轉(zhuǎn)換結(jié)果,即每次A/D采樣循環(huán)需要進(jìn)行三次數(shù)據(jù)交換才能得到有效A/D轉(zhuǎn)換數(shù)據(jù)。采用查詢方式判斷數(shù)據(jù)是否發(fā)送結(jié)束,即SPI狀態(tài)寄存器SPIINT FLAG位為1時表示已完成數(shù)據(jù)發(fā)送。軟件實(shí)現(xiàn)A/D轉(zhuǎn)換的流程框圖如圖4所示。

對于AD7890-10,A/D轉(zhuǎn)換結(jié)果數(shù)據(jù)為二進(jìn)制補(bǔ)碼格式,且包含通道數(shù)據(jù),因此讀取結(jié)果后應(yīng)根據(jù)需要對數(shù)據(jù)進(jìn)行適當(dāng)處理,包括屏蔽通道選擇數(shù)據(jù)和進(jìn)行碼制轉(zhuǎn)換等,以便換算成系統(tǒng)所需要的數(shù)字量。為便于處理,將-10~+10 V電壓對應(yīng)的碼值轉(zhuǎn)換為0~4 096。文中處理方法為:將轉(zhuǎn)換結(jié)果高四位通道數(shù)據(jù)屏蔽后,若A/D輸入為正電壓,則獲取低12位結(jié)果與0x0800相加得到處理后的數(shù)據(jù);若A/D輸入為負(fù)電壓,則將補(bǔ)碼轉(zhuǎn)換成原碼后與0xF800作差獲取處理結(jié)果。

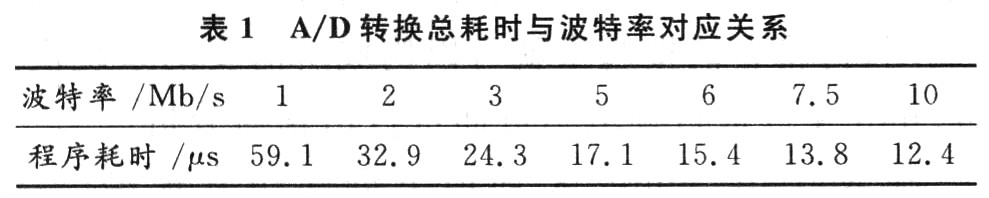

經(jīng)多次測試,得到A/D轉(zhuǎn)換子程序運(yùn)行時間(即一次A/D轉(zhuǎn)換總耗時)與波特率對應(yīng)關(guān)系如表1所示。

從表1中可以看出,為提高轉(zhuǎn)換效率,應(yīng)在可承受范圍內(nèi)選擇盡可能高的波特率,但不應(yīng)超過AD7890-10的上限值10 Mb/s。對文中SPI接口的實(shí)際應(yīng)用表明,A/D轉(zhuǎn)換性能非常穩(wěn)定,效率較高,轉(zhuǎn)換精度高,誤差僅為±1碼,約4.88 mV。

5 結(jié) 語

用DSP的串行外設(shè)接口SPI與串行多通道A/D轉(zhuǎn)換器AD7890組成數(shù)字伺服系統(tǒng)A/D轉(zhuǎn)換功能實(shí)現(xiàn)模塊,能完成8個通道模擬量到數(shù)字量的轉(zhuǎn)換,效率較高,接口簡單,性能穩(wěn)定。通過選擇較高的波特率可以縮短數(shù)據(jù)傳輸時間,提高A/D轉(zhuǎn)換效率。當(dāng)DSP提供的外部時鐘SCLK為AD7890所能承受的最高值10 MHz時,單個通道徹底完成一次A/D轉(zhuǎn)換僅需12.4μs。本文所做的接口設(shè)計為多軸數(shù)字控制系統(tǒng)的A/D轉(zhuǎn)換模塊提供了一種實(shí)用的選擇與參考。