1 引 言

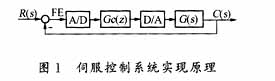

通常,DVD/CD盤片在高速旋轉(zhuǎn)時(shí),由于表面翹曲、不圓度或者外界干擾等因素的存在,使讀數(shù)光束焦深范圍(簡(jiǎn)稱讀數(shù)光點(diǎn))對(duì)目標(biāo)信跡的跟蹤掃描出現(xiàn)誤差。對(duì)此,CD、DVD機(jī)中設(shè)置了伺服控制系統(tǒng),以實(shí)現(xiàn)讀數(shù)光點(diǎn)對(duì)目標(biāo)信跡的動(dòng)態(tài)跟蹤。該系統(tǒng)以PID(比例微積分)閉環(huán)控制理論為基礎(chǔ),采用數(shù)字濾波的方式實(shí)現(xiàn)。該伺服控制系統(tǒng)的實(shí)現(xiàn)原理如圖1所示。

圖1中,Gc(z)為控制濾波器,G(s)為光盤讀寫系統(tǒng)的傳遞函數(shù),R(s)為預(yù)期輸出響應(yīng),C(s)為實(shí)際輸出響應(yīng)。整個(gè)閉環(huán)控制系統(tǒng)實(shí)現(xiàn)的核心是濾波器,它通過(guò)改善誤差(FE)信號(hào)的幅相頻特性來(lái)實(shí)現(xiàn)控制方案。這里,由于濾波器類型和階數(shù)與G(s)密切相關(guān),為了保證伺服控制系統(tǒng)的通用性,必然要設(shè)計(jì)一種通用可配置的濾波器,這正是本文所要討論的重點(diǎn)。

2 系統(tǒng)設(shè)計(jì)

2.1 設(shè)計(jì)原理

數(shù)字濾波器可以用式(1)的差分方程來(lái)表示:

![]()

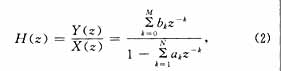

其中,x(n)為輸入序列,y(n)為輸出序列,ak、bk為各自的系數(shù)。其對(duì)應(yīng)的系統(tǒng)函數(shù)為:

當(dāng)ak不都為0時(shí),就是遞歸結(jié)構(gòu)的IIR濾波器;當(dāng)ak都為0時(shí),就是非遞歸結(jié)構(gòu)的FIR濾波器。

2.2 設(shè)計(jì)方法

由于傳統(tǒng)的濾波器設(shè)計(jì)都與濾波器的類型密切相關(guān),不同的類型采用不同的乘加網(wǎng)絡(luò)結(jié)構(gòu)實(shí)現(xiàn),因此,無(wú)法滿足通用的要求。但從濾波器的原始差分表達(dá)式(如式(1)所示)可知,F(xiàn)IR和IIR的區(qū)別僅在于ak是否為零,兩者都進(jìn)行累加乘積計(jì)算,這一特點(diǎn)決定了可以采用編程來(lái)配置濾波器的類型和階數(shù),再用狀態(tài)機(jī)控制累計(jì)乘積的方式實(shí)現(xiàn)濾波器,從而達(dá)到階數(shù)、類型都可配置的目的。

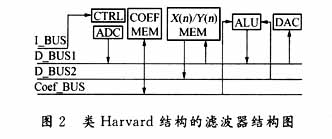

由上述分析可知,所有的x(k)、y(k)、ak、bk均要由存儲(chǔ)器送向運(yùn)算單元進(jìn)行計(jì)算。若采用以運(yùn)算單元為中心的馮諾依曼結(jié)構(gòu),依次從存儲(chǔ)器中取數(shù)據(jù)的做法,則必然會(huì)使速度受到很大影響。因此,我們借用Harvard結(jié)構(gòu)將指令和數(shù)據(jù)分開(kāi)編址、存取的做法,將x(k)、y(k)和ak、bk分別存放在不同的存儲(chǔ)器中,單獨(dú)編址,加快數(shù)據(jù)處理速度。同時(shí),考慮到x(k)、y(k)可能同時(shí)對(duì)存儲(chǔ)器讀寫,將讀、寫數(shù)據(jù)總線分開(kāi),進(jìn)一步提高性能。圖2就是采用類Harvard結(jié)構(gòu)設(shè)計(jì)的濾波器的結(jié)構(gòu)圖。

圖2中共包含一條指令流,三條數(shù)據(jù)流。指令流用于配置濾波器的和實(shí)現(xiàn)濾波器的讀寫控制;數(shù)據(jù)流的D—BUS1用于Y(n)的寫回,D—BUS2用于X(n)、Y(n)的讀出,Coef—BUS用于濾波器系數(shù)的寫回和讀出。因?yàn)橄禂?shù)存儲(chǔ)單元和X(k)、Y(k)存儲(chǔ)單元都采用雙端口SRAM,所以,可同時(shí)進(jìn)行讀、寫操作。

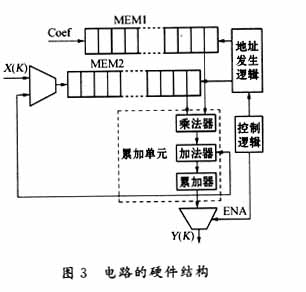

運(yùn)算單元采用算術(shù)累加器(MAC)實(shí)現(xiàn)。MAC由乘法器和加法器組成,其中,乘法器因?yàn)樗俣鹊南拗疲ǔ2捎没诓檎冶恚↙UT)的并行分布算法(DA)實(shí)現(xiàn),但該算法占用硬件資源較多,對(duì)實(shí)現(xiàn)的濾波器的階數(shù)有一定限制,在本電路中不宜采用。在綜合考慮面積和速度兩方面因素后,最終選用Booth乘法器實(shí)現(xiàn)。整個(gè)電路的硬件結(jié)構(gòu)圖如圖3所示。

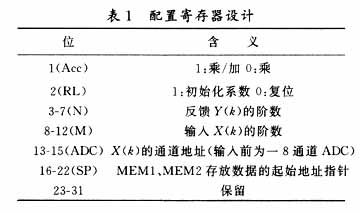

其控制邏輯中的配置寄存器(32bits)設(shè)計(jì)如表1所示。

需要特別說(shuō)明的是,在對(duì)MEM1和MEM2存放數(shù)據(jù)時(shí),濾波器系數(shù)和X(k)、Y(k)必須是一一對(duì)應(yīng)的,從而使每次讀數(shù)據(jù)時(shí)的讀地址相同,簡(jiǎn)化尋址單元的設(shè)計(jì)。濾波器的運(yùn)作是由狀態(tài)機(jī)(邏輯單元)控制的,流程如下:

(1)初始化系數(shù)存儲(chǔ)單元,根據(jù)SP算出X(k)、Y(k)在MEM2中的分界地址SP+N和SP+M+N;

(2)從MEM1、MEM2的(SP+j)單元讀出數(shù)據(jù)送MAC計(jì)算,MEM2讀出的數(shù)據(jù)寫回(SP+j-1)單元,j為0時(shí)的數(shù)據(jù)無(wú)效,不寫回;當(dāng)j為M+N時(shí),轉(zhuǎn)步驟(4);

(3)j加1,重復(fù)步驟(2);

(4)一次Y(k)計(jì)算完成。將當(dāng)前ADC的輸入寫回到MEM2的(SP+M+N)單元;

(5)將本次計(jì)算所得的Y(k)送SP+M,j復(fù)位為0,重復(fù)步驟(2)。

3 實(shí)現(xiàn)與仿真

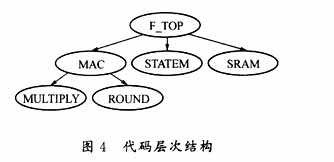

按照上述設(shè)計(jì)思想,用Verilog對(duì)系統(tǒng)進(jìn)行RTL描述,代碼層次結(jié)構(gòu)如圖4所示,其中,F(xiàn)—TOP為頂層wrapper模塊,連接MAC、STATEM、SRAM三個(gè)子模塊。MAC實(shí)現(xiàn)圖3中虛線所示的Booth乘加器,得到的乘積為32 bits數(shù),然后經(jīng)過(guò)舍入調(diào)整(rounding)將其轉(zhuǎn)化為16 bits數(shù);STATEM模塊實(shí)現(xiàn)上文提到的控制流程;SRAM模塊由系數(shù)SRAM和數(shù)據(jù)SRAM(存放X(k)、Y(k))組成,分別對(duì)應(yīng)圖3的MEM1、MEM2,為了方便后面的驗(yàn)證,直接調(diào)用Xilinx的SRAM單元RAMB4—S8—S8。

代碼使用synopsys VCS進(jìn)行仿真,通過(guò)debussy的PLI接口生成fsdb波形文件。在debussy中對(duì)波形(圖5所示是波形仿真圖)進(jìn)行分析。當(dāng)前的配置寄存器的值為0x0000018f,為三階IIR濾波器。READ—EN為讀使能信號(hào),低電平有效。STATE—WE—LOC為寫使能信號(hào),低電平有效。RADDR—LOC和WADDR—LOC是存儲(chǔ)單元的地址,地址范圍從0到5,與三階IIR濾波器對(duì)應(yīng);當(dāng)WADDR—LOC為5時(shí),寫入的是X(k),下一時(shí)鐘周期變?yōu)?,寫入Y(k)(標(biāo)尺線所對(duì)的值0x000a,已經(jīng)過(guò)rounding處理)。XIN—LOC和YIN—LOC是MAC的輸入數(shù)據(jù)。STATE—LOC和YIN—LOC是MAC的輸入數(shù)據(jù)。CUR—STATE為狀態(tài)機(jī)的狀態(tài)變化,可以看出,與前面的狀態(tài)含義和狀態(tài)機(jī)實(shí)現(xiàn)策略一致。這里,讀寫地址在整個(gè)運(yùn)算過(guò)程中都占用兩個(gè)時(shí)鐘周期是為了保證MAC運(yùn)算的正確完成,當(dāng)X(k)和計(jì)算所得的Y(k)寫回時(shí),不涉及MAC運(yùn)算,因此,只分配一個(gè)時(shí)鐘周期。

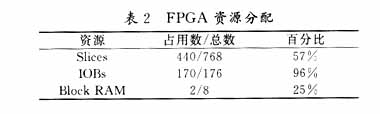

為了確保濾波器以及整個(gè)控制系統(tǒng)設(shè)計(jì)的正確性,我們選用Xilinx Spartan2的XC2S50系列做FPGA驗(yàn)證。首先,在synplify中生成網(wǎng)表文件(edf),然后,通過(guò)Xilinx ISE生成帶延時(shí)信息的單元網(wǎng)表文件(v)和線延時(shí)文件(sdf),用于在VCS中進(jìn)行后仿真,最后生成FPGA下載文件(bit)。XC2S50硬件占用情況如表2所示。表2所示是FPGA資源分配表。

該濾波器在光盤伺服控制電路中的應(yīng)用表明,激 光頭的恢復(fù)時(shí)間、穩(wěn)態(tài)誤差等計(jì)數(shù)參數(shù)均滿足實(shí)際要求。該單元可直接用于伺服芯片的聚焦尋跡模塊。

4 結(jié)束語(yǔ)

文中介紹了一種通用可配置濾波器的設(shè)計(jì)和實(shí)現(xiàn)。通過(guò)對(duì)該濾波器的配置可實(shí)現(xiàn)不同階數(shù)和類型的濾波器,從而加大以數(shù)字濾波為基礎(chǔ)的伺服控制系統(tǒng)應(yīng)用的靈活性。