基于8086 CPU 的單芯片計算機系統(tǒng)的設(shè)計

摘要: 所謂單芯片計算機即是將傳統(tǒng)PC 機箱里的主板上的芯片組、CPU、內(nèi)存、顯卡、聲卡和網(wǎng)卡等最大限度的集成在單個芯片中。單芯片計算機與傳統(tǒng)PC 相比,重量、體積和功耗大幅下降,從而系統(tǒng)性能將得到很大地改善,同時帶來價格的突破性下降,直接促進計算機的迅速普及。本文搭建的單芯片計算機系統(tǒng)基于標(biāo)準(zhǔn)8086 CPU,集成了AMBA 總線、SDRAM、8255、ROM 等外圍IP,并在Altera DE2 FPGA 開發(fā)板上實現(xiàn)了功能演示。

Abstract:

Key words :

1 引言

隨著超大規(guī)模集成電路工藝的發(fā)展,在一顆芯片上集成上百萬甚至上億個晶體管已成為現(xiàn)實。現(xiàn)在,芯片廠商都以面積最小化、功能最大化作為自己的發(fā)展方向,深亞微米效應(yīng)理論及IP 核技術(shù)越來越受到理論界和工業(yè)界的廣泛關(guān)注,系統(tǒng)芯片是當(dāng)前技術(shù)發(fā)展的必然趨勢。計算機的發(fā)展經(jīng)歷了電子管計算機、晶體管計算機、集成電路計算機和大規(guī)模集成電路計算機,它的發(fā)展一直是將越來越多的功能集成在越來越小的空間內(nèi)。可以預(yù)見,在某些特定領(lǐng)域,半導(dǎo)體制造業(yè)朝著整合型單芯片系統(tǒng)的總體趨勢將會日益明顯。

所謂單芯片計算機即是將傳統(tǒng)PC 機箱里的主板上的芯片組、CPU、內(nèi)存、顯卡、聲卡和網(wǎng)卡等最大限度的集成在單個芯片中。單芯片計算機與傳統(tǒng)PC 相比,重量、體積和功耗大幅下降,從而系統(tǒng)性能將得到很大地改善,同時帶來價格的突破性下降,直接促進計算機的迅速普及。

本文搭建的單芯片計算機系統(tǒng)基于標(biāo)準(zhǔn)8086 CPU,集成了AMBA 總線、SDRAM、8255、ROM 等外圍IP,并在Altera DE2 FPGA 開發(fā)板上實現(xiàn)了功能演示。

2 單芯片計算機的發(fā)展概況

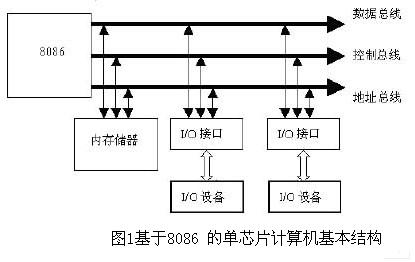

單芯片計算機是一個完整的計算機系統(tǒng),CPU、存儲器和輸入輸出接口,通過總線連接,構(gòu)成了單芯片計算機的基本系統(tǒng)。單芯片計算機的系統(tǒng)級設(shè)計,是以CPU 為核心開展的I/O和外設(shè)集成過程,是基本的SoC 設(shè)計流程。

近幾年,Intel、AMD 和VIA 等微處理器制造商紛紛推出平臺策略,將微處理器和芯片組組合在一起,形成一個完整的解決方案,并計劃將來進一步推出集成所有芯片的單芯片微處理器。Intel 公司頻推平臺策略,計劃進一步推出整合所有芯片的單芯片計算機,還*了一個由500 名工程師組成的研發(fā)團隊,開發(fā)其單芯片電腦產(chǎn)品,希望將目前電腦主板上的32 顆芯片全部集成到單一的芯片中。 而在AMD 四核皓龍?zhí)幚砥髦校膫€獨立的CPU 核集成到單一硅片上,每個核具有單獨的64KB 一級數(shù)據(jù)緩存、64KB 一級指令緩存和512KB 的二級緩存,四個核心共享2MB(或者更大)的三級緩存。這樣每個CPU 核都能夠充分發(fā)揮各自的效能,從而大幅度提升整個處理器的性能。

單芯片計算機的設(shè)計,是一個基于某一種型號CPU 及其外圍I/O 接口的SoC 設(shè)計過程。因此,選擇哪種型號的CPU 就成了設(shè)計的首要問題。綜合設(shè)計難度,工程進度的因素,同時考慮所選CPU 要有一定的代表性,因此最終選擇標(biāo)準(zhǔn)Intel 8086 CPU。基于8086 的單芯片計算機基本結(jié)構(gòu),如圖1 所示。

3 單芯片計算機系統(tǒng)的設(shè)計

8086 CPU 芯片有兩種工作模式,最小模式與最大模式。所謂最小模式,是指系統(tǒng)中只有一個8086 微處理器,在這種情況下,所有的總線控制信號,都直接由8086 CPU 產(chǎn)生,系統(tǒng)的總線控制邏輯電路被減到最少,該模式適用于規(guī)模較小的微機應(yīng)用系統(tǒng)。

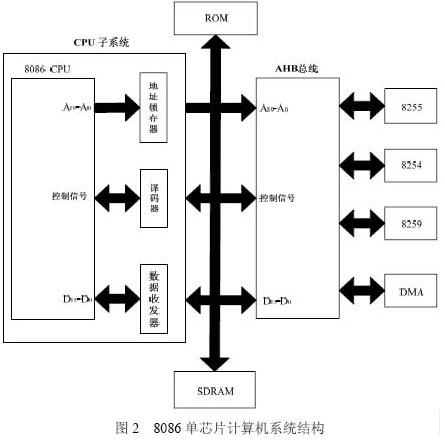

本實驗采用8086 的最小工作模式進行單芯片計算機的設(shè)計。所謂單芯片計算機系統(tǒng)設(shè)計,即除了包含CPU、ROM、RAM、總線、地址鎖存器、數(shù)據(jù)收發(fā)器、外設(shè)地址譯碼電路以外,集成一個或一個以上的外圍I/O 接口,從而構(gòu)成一個完整的系統(tǒng)。搭建的系統(tǒng)結(jié)構(gòu)圖如2 所示。

本論文所設(shè)計的8086 單芯片計算機系統(tǒng)集成了遵從AMBA 協(xié)議的總線、8255 通用并行接口,以及SDRAM 控制器。在這里,以8255 通用并行接口為例,介紹包含8255 應(yīng)用電路的單芯片計算機系統(tǒng)的設(shè)計。8255 作為外圍I/O 設(shè)備通過AHB 總線與8086CPU 進行通信。

單芯片計算機系統(tǒng)的RTL 級設(shè)計是一個SoC 的設(shè)計過程。包括CPU 子系統(tǒng)的設(shè)計、總線的選擇和接口設(shè)計,以及存儲器單元的接口設(shè)計。

3.1 CPU 子系統(tǒng)的設(shè)計

CPU 子系統(tǒng)包括8086 CPU、數(shù)據(jù)收發(fā)控制器、地址鎖存器和存儲器譯碼電路等。

CPU 與存儲器(或I/O 端口)進行交換時,CPU 首先要送出地址信號,然后再發(fā)出控制信號及傳送數(shù)據(jù)。因此需要加入地址鎖存器,先鎖存地址,使在讀寫總線周期內(nèi)地址穩(wěn)定。

數(shù)據(jù)收發(fā)控制器相當(dāng)于一個總線開關(guān),用來控制CPU 的數(shù)據(jù)總線選擇從存儲單元或I/O端口發(fā)送或接受數(shù)據(jù),匹配通信時序。

存儲器譯碼電路與74LS138 原理一樣,利用地址線生成ROM 和RAM 單元的片選信號。CPU 上電復(fù)位后地址為FFFF0H,首先從ROM 里讀出程序,該程序是無條件跳轉(zhuǎn)指令,能夠使CPU 跳轉(zhuǎn)到RAM 的地址。CPU 再從SDRAM 里讀出程序。

3.2 總線的選擇和設(shè)計

總線的集成對縮小芯片的面積以及減少總線的扇出都有非常積極的意義。標(biāo)準(zhǔn)的8086CPU,一般采用的是傳統(tǒng)的三總線結(jié)構(gòu),就是地址總線、數(shù)據(jù)總線、控制總線,基于這個總線架構(gòu),還可以擴展8255、顯示器、鍵盤/鼠標(biāo)、網(wǎng)卡之類的IP。

3.2.1 總線協(xié)議的選擇

傳統(tǒng)的8086 系列CPU 系統(tǒng)總線有ISA 總線、EISA 總線等。ISA 總線是16 位的系統(tǒng)總線,其工作頻率為8MHz,數(shù)據(jù)傳輸速率為16MB/s。EISA 是一種在ISA 總線基礎(chǔ)上擴充的數(shù)據(jù)寬度為32 位的開放總線標(biāo)準(zhǔn)。最大傳輸速率可以達到33MB/s。但是由于I/O 速度比較低,這兩種總線技術(shù)已經(jīng)逐漸被淘汰。

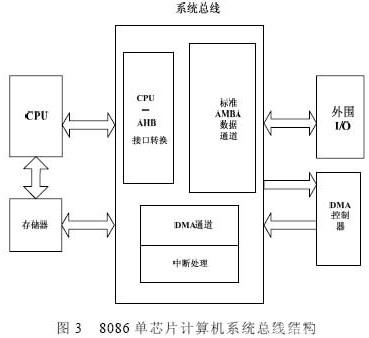

AMBA 擁有眾多第三方支持,在基于ARM 處理器內(nèi)核的SoC 設(shè)計中,已經(jīng)成為廣泛支持的現(xiàn)有互聯(lián)標(biāo)準(zhǔn)之一。2.0 版AMBA 標(biāo)準(zhǔn)定義了三組總線:AHB(AMBA 高性能總線)、ASB(AMBA 系統(tǒng)總線)、和APB(AMBA 外設(shè)總線)。AHB 的總線架構(gòu)的相互連接采用了傳統(tǒng)的帶有主模塊和從模塊的共享總線模式,接口與互連功能分離,這對芯片上模塊之間的互連具有重要意義。因此,本論文所選擇的總線遵從AHB 總線傳輸?shù)幕疽?guī)范,并在此基礎(chǔ)上針對8086CPU 的特點增加和修正了某些總線的接口。整個設(shè)計主要包括兩方面的內(nèi)容:AHB 和8086 傳輸時序的匹配;基于8086CPU 的總線接口的擴展設(shè)計。總線結(jié)構(gòu)圖如圖3 所示。

3.2.2 傳輸時序的匹配

因為AHB 總線和CPU 的傳輸協(xié)議不同,所以需要匹配兩個接口的時序,以保證CPU與其他外圍IP 可以通過總線正常通信。相關(guān)接口控制信號如表1 所示。

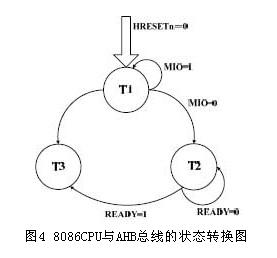

接口模塊首先根據(jù)MIO 信號判斷訪問的是存儲器還是I/O 設(shè)備,如果是I/O 設(shè)備,當(dāng)采樣到READY 信號為高電平時,獲取AHB 的總線控制權(quán),與外圍I/O 設(shè)備進行通信。設(shè)計的狀態(tài)機如圖4 所示。

T1:根據(jù)MIO 信號判斷當(dāng)前CPU 是否需要訪問外圍I/O。如果8086 處理器核訪問的是存儲器單元而不是AHB 總線上的設(shè)備(即MIO 為1),狀態(tài)機則保持T1 狀態(tài),并且不向AHB 總線發(fā)出總線請求信號(即HBUSREQ 信號置為0)。MIO 為低電平則跳轉(zhuǎn)到T2。

T2:狀態(tài)機進入T2 狀態(tài)后,向AHB 總線發(fā)出總線請求信號(即HBUSREQ 信號置為1),向AHB 總線仲裁器請求訪問總線。同時檢測READY 信號,當(dāng)檢測到READY 信號為高電平,即AHB 總線仲裁器把總線訪問權(quán)限交給8086 處理器核,狀態(tài)機在下個時鐘上升沿進入T3 狀態(tài)。反之,如果READY 一直為低電平,表示目前8086 CPU 要訪問的AHB 總線上的從設(shè)備沒有準(zhǔn)備就緒,要求8086 處理器核插入等待狀態(tài),狀態(tài)機一直保持T2 狀態(tài)不變。

T3:CPU 通過AHB 總線與外圍IP 進行通信,直至通信結(jié)束,返回到T1 狀態(tài)。

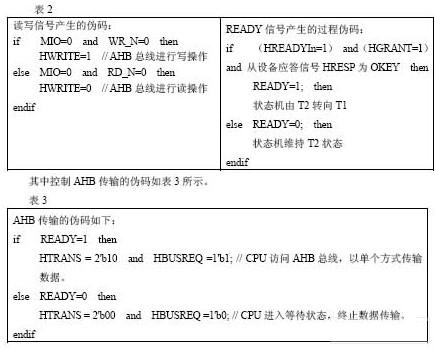

8086 處理器核的讀寫信號受READY 信號控制,當(dāng)READY 信號為高電平時,可進行數(shù)據(jù)的接收和發(fā)送,否則讀寫信號保持。READY 信號由AHB 總線上從設(shè)備傳輸完成信號HREADYIn、AHB 總線允許信號HGRANT 以及從設(shè)備應(yīng)答信號HRESP 三者共同決定。而總線上的讀寫控制信號HWRITE 由組合邏輯產(chǎn)生。其產(chǎn)生過程偽碼如表2 所示。

3.2.3 總線接口擴展

8086CPU 除了數(shù)據(jù)、地址總線以及讀寫和READY 等主要控制信號外,還有中斷請求和應(yīng)答以及外接DMA 設(shè)備的相關(guān)端口信號。而這些信號是標(biāo)準(zhǔn)AHB 總線所不具備的,因此還需要擴展總線接口以匹配8086 CPU。總線接口的擴展設(shè)計主要包括兩部分:中斷處理和DMA 數(shù)據(jù)通道。8086 CPU 關(guān)于中斷和DMA 的端口信號如表4 所示。

系統(tǒng)總線在接收到外設(shè)的中斷請求之后,會向CPU 提出中斷申請,一旦接收到中斷響應(yīng),要向外設(shè)傳送中斷響應(yīng)信號,同時修改譯碼單元,選通該外設(shè),保證在第二個中斷響應(yīng)期間能將中斷類型號通過總線傳送給CPU,使得CPU 能成功跳轉(zhuǎn)到中斷服務(wù)子程序。

DMA 控制器在執(zhí)行數(shù)據(jù)傳輸時,需要掌握AHB 總線的控制權(quán),向片上存儲器或者總線上其他外設(shè)發(fā)出地址和控制信號,即相當(dāng)于AMBA 的主設(shè)備;另一方面,在DMA 控制器啟動工作之前,CPU 需要對其進行預(yù)處理操作,以使其按照特定的配置參數(shù)進行工作,在這個初始化階段,CPU 是AHB 總線上的主設(shè)備,DMA 控制器屬于從設(shè)備。基于DMA控制器的這種兩面性,在總線設(shè)計中配備了專門的DMA 通道與其相匹配:CPU 正常工作時,

DMA 扮演從設(shè)備的角色,接受CPU 對其的初始化;利用HLDA 作仲裁信號,當(dāng)CPU 響應(yīng)外設(shè)DMA 請求時(即HLDA 為高電平),讓出總線控制權(quán)給外設(shè),利用DMA 數(shù)據(jù)通道傳輸數(shù)據(jù),傳輸?shù)膮f(xié)議同樣遵從AMBA 協(xié)議。總線的時序控制模塊狀態(tài)如圖5 所示。

3.3 存儲單元的接口設(shè)計

存儲器子系統(tǒng)包括一個RAM 和一個ROM,8086CPU 支持20 位地址總線,具有1M 字節(jié)存儲空間,分為RAM 區(qū)和ROM 區(qū)。本文利用開發(fā)板的片上ROM 資源配置成16k*16 的格式作為存儲器中的ROM 單元,采用DE2 開發(fā)板上的8M 的SDRAM 配置成256K*16 位總線格式代替存儲器中的RAM 單元。

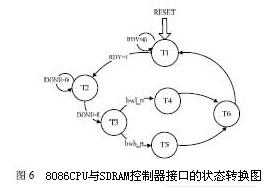

在各種隨機存儲器件中,SDRAM 的價格低,體積小,速度快,容量大,是比較理想的器件。但SDRAM 的控制邏輯比較復(fù)雜,對時序要求也十分嚴格,這就要求有一個專門的控制器:控制SDRAM 的初始化,刷新和預(yù)沖以及基本的讀寫操作。同時,需要匹配SDRAM控制器和8086 CPU 的讀寫時序。該接口具體實現(xiàn)的狀態(tài)機如圖6 所示。

T1:當(dāng)RDY 為高電平時,首先確定是進行讀還是寫操作,這時DONE 為0:讀:設(shè)置WR=0,RD=1; 寫:設(shè)置WR=1,RD=0。

T2:當(dāng)DONE 信號為高電平,表示可以進行讀/寫操作,跳轉(zhuǎn)到T3。

T3:CPU 通過SDRAM 控制器對SDRAM 進行讀寫操作。

T4:當(dāng)?shù)妥止?jié)有效信號bwl_n 為高電平時,執(zhí)行低字節(jié)傳輸。

T5:當(dāng)高字節(jié)有效信號bwh_n 為高電平時,執(zhí)行高字節(jié)傳輸。

T6:CPU 完成讀寫操作,相關(guān)控制信號清零。

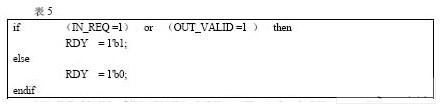

其中,DONE 信號用于指示是否讀寫完成,只有DONE 為高電平時表示讀寫完成,才能進行下次讀寫操作。RDY 信號表示SDRAM 是否做好準(zhǔn)備接受CPU 的訪問,由SDRAM的寫請求信號(IN_REQ =1)和讀有效信號(OUT_VALID =1 )共同控制,其產(chǎn)生過程偽碼如表5 所示。

根據(jù)單芯片計算機系統(tǒng)級設(shè)計的組成結(jié)構(gòu),調(diào)用已經(jīng)編寫完成的8086 IP 軟核、8255 IP軟核、SDRAM 控制器、SDRAM 模型IS42S16400、AHB 總線 IP 軟核以及譯碼器IP 軟核。

連接相應(yīng)的輸入輸出端口,同時對8086 相關(guān)的輸入端口進行賦值,將未使用的輸出端口懸空,完成單芯片計算機系統(tǒng)的RTL 級設(shè)計。

4 單芯片計算機系統(tǒng)的仿真與驗證

單芯片計算機的RTL 級設(shè)計只是全部設(shè)計流程的一部分,為保證最終設(shè)計的成功,必須對其進行全面的軟件仿真與硬件驗證,包括搭建測試平臺,設(shè)計測試方案以及分析仿真結(jié)果,實現(xiàn)FPGA 驗證。

4.1 測試方案的設(shè)計

在包含8255 應(yīng)用電路的單芯片計算機系統(tǒng)搭建完成的基礎(chǔ)上,要求實現(xiàn)八個開關(guān)量控制八個LED 燈亮滅的功能。將八個開關(guān)量連接8255 的PA0~PA7;將八個LED 燈驅(qū)動電路連接8255 的PC0~PC7。在8086 CPU 的控制下,通過總線讀取連接在8255 PA 口的八個開關(guān)量,將開關(guān)值送往SDRAM 存儲,再從SDRAM 讀取開關(guān)量發(fā)送到8255 PC 口,使其驅(qū)動八個LED 燈的亮或滅。

4.2 仿真結(jié)果分析

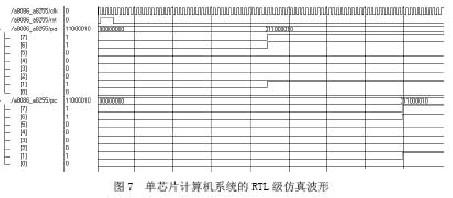

單芯片計算機最小集的RTL 級仿真波形,如圖7 所示。在8086 CPU 的控制下,8255接口讀取連接在8255 PA 口的八個開關(guān)量11000010 以后,將其發(fā)送到8255 的PC 口,驅(qū)動輸出邏輯值11000010。

使用Quartus II 軟件成功編譯設(shè)計,將布局布線生成的結(jié)果下載到FPGA 中,得到與設(shè)計等效的實際電路,對實際的電路用測試系統(tǒng)進行測試,從而驗證設(shè)計的正確性。將FPGA的驗證結(jié)果經(jīng)邏輯分析儀讀取顯示,如圖8 所示。

5 結(jié)束語

本論文在基于集成電路設(shè)計方法學(xué)的指導(dǎo)下,探討了一種基于8086 CPU 核的單芯片計算機平臺的架構(gòu),研究了其與AMBA 總線、SDRAM、8255 等外圍IP 的集成。在此基礎(chǔ)上,設(shè)計基于8086 IP 軟核的單芯片計算機系統(tǒng),并實現(xiàn)了FPGA 功能演示。在后續(xù)的工作中,將考慮進一步擴展CPU 外圍接口IP 軟核;集成DMA 控制器,實現(xiàn)VGA 顯示功能;將DOS 操作系統(tǒng)加入8086 單芯片計算機平臺,并開發(fā)在操作系統(tǒng)下的設(shè)備驅(qū)動程序和應(yīng)用軟件。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。