摘 要:基于ADSP-TS101S" title="ADSP-TS101S">ADSP-TS101S多處理器系統(tǒng)" title="多處理器系統(tǒng)">多處理器系統(tǒng)的空間譜估計" title="空間譜估計">空間譜估計超分辨測向" title="超分辨測向">超分辨測向系統(tǒng)的硬件實現(xiàn),并結(jié)合實例說明了其有效性和實用性。

關(guān)鍵詞:空間譜估計? 超分辨測向? MUSIC算法? ADSP-TS101S? 鏈路" title="鏈路">鏈路口

?

??? 空間譜估計超分辨是一種空域處理技術(shù),具有優(yōu)越的空域參數(shù)(如方位角)估計性能[1]。空間譜估計屬于陣列信號處理的一個重要分支,其基本原理是通過空間陣列接收數(shù)據(jù)的相位差來確定一個或幾個待估計的參數(shù),如方位角、俯仰角及信號源個數(shù)等。空間譜估計超分辨技術(shù)可以大大改善在系統(tǒng)處理帶寬內(nèi)空間信號的角度估計精度、角度分辨力及其他相關(guān)參數(shù)精度,因而在雷達、通信、聲吶等眾多領(lǐng)域有廣闊的應(yīng)用前景。

??? 為了滿足快速掃描及系統(tǒng)處理的實時性要求,本系統(tǒng)采用支持浮點運算的高速處理器ADSP-TS101S,其DSP之間鏈路口的無縫連接可以提供高速率數(shù)據(jù)傳輸;采用空間譜估計中MUSIC算法對從天線陣元接收到的數(shù)據(jù)進行處理,提高測角精度,實現(xiàn)超分辨測向;用多片DSP分工同時進行目標搜索可以提高搜索速度。本文主要研究基于ADSP-TS101S多處理器系統(tǒng)的空間譜估計超分辨測向算法的硬件實現(xiàn)。

1 空間譜估計超分辨測向基本原理

??? 空間譜估計超分辨測向的基本原理為通過對多元天線陣接收的空中無線電信號進行放大、變頻、采樣以及A/D變換后的數(shù)字信號進行數(shù)學(xué)處理來估計信號的來波方向,其中最常用的算法是多重信號分類(MUSIC)算法[1]。MUSIC算法的過程為先計算陣列接收數(shù)據(jù)的協(xié)方差矩陣R,對R進行特征分解求出其特征值和特征向量。根據(jù)特征值可以確定信號源的數(shù)量,利用由特征向量組成的信號子空間和噪聲子空間的正交關(guān)系,對兩個子空間進行適當?shù)奶幚恚_定無線電信號來波方向。

???  ???

???

?

2 ADSP-TS101S的主要性能

??? TigerSHARC是ADI公司的定浮點兼容的高速DSP系列處理器,比SHARC系列處理器具有更多的片上存儲器、更高的并行度、更寬的帶寬、更快的時鐘速率以及更大的靈活度,是專門為數(shù)字信號處理任務(wù)和復(fù)雜通信算法而設(shè)計的。

??? TigerSHARC系列的ADSP-TS101S內(nèi)部集成了靜態(tài)超標量體系結(jié)構(gòu)和大容量的SRAM。處理器工作在300MHz,單周期能執(zhí)行4條指令,能實現(xiàn)每秒2.4億次乘累加操作和每秒1.8億次浮點操作,并且支持兩種方式的集成多處理器連接,很容易實現(xiàn)多片并行處理系統(tǒng),使得該處理器能達到無縫超標量能力和杰出的I/O性能表現(xiàn)[2]。

??? ADSP-TS101S的主要性能有:

??? · 最高運行速度為300MHz,指令周期為3.3ns;

??? · 片內(nèi)帶有6Mbit雙口SRAM;

??? · 支持32位浮點和8位、16位、32位和64位定點運算;

??? · 提供最大1800MFLOPS運算能力;

??? · 帶有雙運算模塊,每個包含一個ALU、一個乘法器、一個移位器和一個寄存器組;

??? · 有14個DMA通道進行數(shù)據(jù)傳輸;

??? · 片上有4個鏈路口,可實現(xiàn)系統(tǒng)加載和多處理器間無縫連接;

??? · 簇式多處理器最高可支持8個ADSP-TS101S。

??? ADSP-TS101S具有高速處理能力,片內(nèi)帶有較大容量存儲器,而且優(yōu)越的浮點運算能力和鏈路口的無縫連接能力特別適合運算復(fù)雜的信號處理系統(tǒng)和多處理器系統(tǒng)。

??? 采用鏈路口連接的多處理器系統(tǒng),可以實現(xiàn)無縫連接,無總線仲裁問題,總的鏈路口通道數(shù)據(jù)傳輸速率高于共享總線方式[3]。各DSP程序可以獨立設(shè)計,而且片間引線少,PCB板設(shè)計容易。除此之外,ADSP-TS101S還可以用匯編語言和C語言編程,而且同一個程序也可以部分用C、部分用匯編語言編程,二者可以相互調(diào)用。

3 系統(tǒng)設(shè)計

??? 本系統(tǒng)主要是實現(xiàn)雷達信號的超分辨測向。其實時性和連續(xù)性要求處理系統(tǒng)應(yīng)具有較高的浮點數(shù)據(jù)處理能力,所以設(shè)計時采用四片ADSP-TS101S構(gòu)成并行處理系統(tǒng),以提高系統(tǒng)的數(shù)據(jù)處理能力。

3.1 硬件系統(tǒng)設(shè)計

??? 輸入中頻解調(diào)后的I、Q兩路數(shù)據(jù),運用空間譜估計算法進行運算處理得到該雷達信號的DOA估計。將方位0°~360°、俯仰0°~90°的搜索范圍分成四個部分,每片ADSP-TS101S分別承擔90°俯仰90°方位即1/4的搜索范圍。

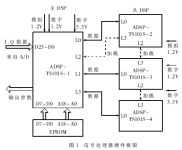

??? 系統(tǒng)的硬件框圖如圖1所示。

?

?

??? ADSP-TS101S-1接收中頻解調(diào)后的I、Q兩路數(shù)據(jù)后,對數(shù)據(jù)進行誤差校正和噪聲抑制得到X(n)。主DSP ADSP-TS101S-1按照空間譜估計超分辨測向的MUSIC算法將X(n)的自相關(guān)函數(shù)X(n)進行特征分解,判斷信號源個數(shù)。主DSP將X(n)的特征向量和信號源個數(shù)通過鏈路口傳輸給三個從DSP。ADSP-TS101S-1、ADSP-TS101S-2、ADSP-TS101S-3、ADSP-TS101S-4分別在自己的搜索范圍內(nèi)進行譜峰搜索。從DSP需將搜索結(jié)果通過鏈路口回傳給主DSP。最后由主DSP將各搜索結(jié)果匯總,判斷輸出信號的DOA估計。四片ADSP-TS101S在各自的范圍內(nèi)同時搜索,大大降低了MUSIC算法在譜峰搜索上花的時間,提高了系統(tǒng)的實時性。

3.2 電源與復(fù)位電路

??? ADSP-TS101S采用三電源供電,其中模擬1.2V為內(nèi)部鎖相環(huán)和倍頻電路供電;數(shù)字1.2V為DSP內(nèi)核供電;數(shù)字3.3V為I/O供電。內(nèi)核最大電流為1.277A,I/O平均電流為0.137A[1]。

??? ADSP-TS101S要求內(nèi)核電源1.2V和I/O電源3.3V同時上電。若不能嚴格同步,應(yīng)保證內(nèi)核比I/O先上電。本系統(tǒng)在數(shù)字3.3V輸入端并聯(lián)了一個十幾微法大電容,而在數(shù)字1.2V輸入端只并聯(lián)了一個零點幾微法小電容,從而保證了3.3V充電時間大于1.2V充電時間,解決了電源供電先后的問題。

??? ADSP-TS101S要求復(fù)位信號的特殊波形,否則不能保證100%正確復(fù)位,設(shè)計時應(yīng)充分引起重視。上電復(fù)位波形要求如圖2所示。圖2中低電平時間tSTART_LO在上電穩(wěn)定后必須大于2ms;高脈沖時間tPULSE1_HI必須大于50個系統(tǒng)時鐘周期,小于100個系統(tǒng)時鐘周期;低脈沖時間tPULSE2_LO必須大于100個系統(tǒng)時鐘周期。

?

3.3 鏈路口加載

??? ADSP-TS101S可以通過鏈路口加載方式實現(xiàn)單片EPROM加載多片ADSP-TS101S,從而降低系統(tǒng)的復(fù)雜度。第一片DSP采用EPROM(Flash)加載方式實現(xiàn)自身加載,其余處理器通過鏈路口實現(xiàn)加載。在通過鏈路口松耦合方式連接的多處理器系統(tǒng)中,實現(xiàn)整個系統(tǒng)的程序加載也是非常關(guān)鍵的一步。具體的軟件設(shè)計可參考相關(guān)資料[3]。

??? 鏈路口加載完成之后,還可以進行數(shù)據(jù)傳輸工作,不會有任何沖突問題。通過鏈路口的復(fù)用方式可以更有效地利用鏈路口資源。值得注意的是,采用鏈路口松耦合方式連接的多處理器系統(tǒng)中,所有處理器的ID號都設(shè)置為0。

3.4 鏈路口通信

??? 由系統(tǒng)硬件設(shè)計可以看出,正確充分地應(yīng)用鏈路口傳輸是本系統(tǒng)的關(guān)鍵。ADSP-TS101S片上有四個鏈路口,每個鏈路口均有8位數(shù)據(jù)總線進行通信,有三個控制引腳控制通信的時鐘、數(shù)據(jù)傳輸方向和確認應(yīng)答信號,可支持多片ADSP-TS101S處理器間點對點的雙向數(shù)據(jù)傳輸[5]。四個鏈路口數(shù)據(jù)吞吐率最高可達1.2GBps,而且其傳輸速率在軟件上也可以控制。數(shù)據(jù)傳輸時,鏈路口可以直接由處理器核控制,也可以由DMA控制器控制。每個鏈路口都有專門的DMA發(fā)送通道和DMA接收通道[6],DMA可以將傳輸?shù)臄?shù)據(jù)自動打包成四個組,方便使用。全0全1的突變是數(shù)據(jù)傳輸最惡劣的情況,對傳輸效果影響極大,所以應(yīng)當盡量想辦法避免。

??? 當鏈路口布線比較長,特別是跨板連接時,傳輸線的阻抗將影響信號的延遲或者會產(chǎn)生振蕩。此時應(yīng)該在鏈路口上加上緩沖區(qū),增強信號的傳輸驅(qū)動能力并進行阻抗匹配,而且鏈路口時鐘輸入控制線上應(yīng)該加50pF左右的電容進行濾波,保證接收端鏈路口輸入時鐘免受窄脈沖干擾的影響。

4 DSP芯片應(yīng)用情況比較

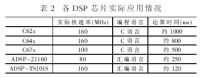

??? 現(xiàn)代信號處理系統(tǒng)中常用的DSP有TI公司的C62x、C64x、C67x,ADI公司的ADSP-21160、ADSP-TS101S、ADSP-TS201S。其中C62x和C64x是定點DSP,其他四種DSP都支持浮點運算。本系統(tǒng)中要求進行浮點運算,而用定點DSP C62x和C64x進行浮點運算,速度顯然達不到實時性要求。C67x、ADSP-21160、ADSP-TS101S、ADSP-TS201S這幾種浮點DSP,性能各不相同。C67x主頻只有167MHz,片內(nèi)只有1Mbit的內(nèi)存。ADSP-21160內(nèi)核時鐘只有100MHz。ADSP-TS101S、ADSP-TS201S都有很高的浮點運算能力。ADSP-TS101S是一款性價比很高的浮點DSP,而且應(yīng)用非常方便。ADSP-TS201S的片上內(nèi)存、內(nèi)核時鐘和浮點運算能力都比ADSP-TS101S更有優(yōu)勢。各DSP芯片性能比較見表1。

?

??? 相同的方案下可選用不同的DSP芯片實現(xiàn)本系統(tǒng)中的超分辨測向,其實際應(yīng)用情況如表2(程序都未曾進行優(yōu)化)。從表2可以看出,由于制作工藝和電源時鐘不理想,各DSP并不能工作在最高核速率。ADI公司的兩款DSP采用匯編語言編程,執(zhí)行同一任務(wù)所用的匯編指令比C語言編譯產(chǎn)生的匯編指令少,因此相同的核速率下,用匯編語言編程的DSP計算速度快。其中兩個定點DSP C62x和C64x運算速度很慢。綜合這些結(jié)果可知,ADSP-TS101S多處理器系統(tǒng)在實用方面有明顯的優(yōu)勢。

?

?

??? 因DSP-TS201S價格相對昂貴,而且進行高速信號處理對制板的要求極高,一般的Protel軟件畫的PCB電路板達不到要求,加上電源和時鐘的因素,影響信號的質(zhì)量,使DSP無法有效工作在最高頻率而實現(xiàn)更快速的運算,不能發(fā)揮其優(yōu)勢,故未進行ADSP-TS201S的實驗。如果條件成熟后,則可以采用這些更高性能的DSP實現(xiàn)超分辨測向。

??? MUSIC算法的譜峰搜索占用了運算的絕大部分時間。以本系統(tǒng)為例,計算數(shù)據(jù)協(xié)方差矩陣和其特征值以及特征向量只需要3ms,而其余一百多毫秒時間全都花在譜峰搜索上。

??? 本文研究了基于ADSP-TS101S多處理器系統(tǒng)的空間譜估計超分辨測向系統(tǒng)的硬件實現(xiàn),同時結(jié)合實例說明了其有效性和實用性。工程實踐表明基于ADSP-TS101S的多處理器系統(tǒng)能夠完成雷達信號的超分辨測向,實現(xiàn)近實時處理。目前該系統(tǒng)工作穩(wěn)定,達到預(yù)期效果。

參考文獻

[1] 王永良,陳輝,彭應(yīng)寧等.空間譜估計理論與算法[M].北京:清華大學(xué)出版社,2004.

[2] 王林,劉書明,張靜.基于ADSP-TS101S的多芯片數(shù)字信號處理系統(tǒng)的實現(xiàn)方案[J].電子設(shè)計應(yīng)用,2004,(9):94-97.

[3] 劉書明,蘇濤,羅軍輝.TigerSHARC DSP應(yīng)用系統(tǒng)設(shè)計[M].北京:電子工業(yè)出版社,2004.

[4] 申軍建,張勐,卓智海.ADSP-TS101S的自動引導(dǎo)方式分析與設(shè)計實現(xiàn)[J].電子設(shè)計應(yīng)用,2004,(5):64-66.

[5] SAWYER N.Analog devices tigerSHARC link.Analog?Device,Inc,2004,10.

[6] 莊德靖,蘇濤.一種新型DSP(TS101)中的鏈路DMA[J].國外電子元器件,2005,(2):21-24.