高速DSP串行外設(shè)接口設(shè)計

摘要: 其中串行外設(shè)接口(Serial Peripheral InteRFace)是Motorola公司提出的一種同步串行外圍接口協(xié)議.主要應(yīng)用在EEPROM、FLASH、實時時鐘、AD轉(zhuǎn)換器.還有數(shù)字處理和數(shù)字解碼器之間。包括主/從2種模式,具有I/O資源占用少、協(xié)議實現(xiàn)簡單、傳輸速度快、能夠同時收發(fā)信息、支持絕大部分處理器芯片等優(yōu)點,是一種高速的全雙工、同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳.同時為PCB的布局上節(jié)約了空間,提供了方便,正是出于這種簡單易用的特性,TMS320LF2407芯片也集成了這種通信協(xié)議。

Abstract:

Key words :

1 引言

DSP(數(shù)字信號處理)的優(yōu)勢除了處理復(fù)雜的運算,特別適用于數(shù)字濾波、語音、視頻、圖象處理、通信以及高速實時測控系統(tǒng)中已成為現(xiàn)代信息處理技術(shù)的重要器件,極大地促進了信號處理和測控各個領(lǐng)域的學(xué)術(shù)研究、產(chǎn)品開發(fā)及應(yīng)用。TI公司TMS320LF2407是一種專用定點DSP芯片,與以往的產(chǎn)品相比.最大不同就是有豐富的外設(shè).像SCI、SPI、EV等等.在處理數(shù)據(jù)優(yōu)勢上添加了事務(wù)管理能力。

其中串行外設(shè)接口(Serial Peripheral InteRFace)是Motorola公司提出的一種同步串行外圍接口協(xié)議.主要應(yīng)用在EEPROM、FLASH、實時時鐘、AD轉(zhuǎn)換器.還有數(shù)字處理和數(shù)字解碼器之間。包括主/從2種模式,具有I/O資源占用少、協(xié)議實現(xiàn)簡單、傳輸速度快、能夠同時收發(fā)信息、支持絕大部分處理器芯片等優(yōu)點,是一種高速的全雙工、同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳.同時為PCB的布局上節(jié)約了空間,提供了方便,正是出于這種簡單易用的特性,TMS320LF2407芯片也集成了這種通信協(xié)議。

2 SPI接口結(jié)構(gòu)和設(shè)計原理

2.1 SPI接口結(jié)構(gòu)

該SPI設(shè)計主要有兩大部分組成:微控制器接口和SPI控制接口。通過控制線、數(shù)據(jù)線、和地址線三大總線把微控制接口與SPI控制接口連接在一起,如果外部有更多的SPI接口模塊。可以由SPI控制接口運用軟件編程與設(shè)置,實現(xiàn)擴展具有SPI接口的外部設(shè)備。

TMS320LF2407中采用的主從控制器連接通信。主控制器通過輸出SPICLK信號來啟動數(shù)據(jù)傳送。對主控制器和從控制器.?dāng)?shù)據(jù)都是在SPICLK的一個邊沿移出移位寄存器,并在相對的另一個邊沿鎖存到移位寄存器。如果CLOCK PHASE位是1.?dāng)?shù)據(jù)的發(fā)送和傳輸就要在SPICLK跳變之前的半個周期發(fā)生。主控制器可以在任一時刻啟動數(shù)據(jù)發(fā)送.因為它控制著SPICLK信號。由軟件決定了主控制器如何檢測從控制器何時準(zhǔn)備發(fā)送數(shù)據(jù),以啟動SPI傳送數(shù)據(jù)。

圖1 SPI內(nèi)部結(jié)構(gòu)

2.2 SPI設(shè)計原理

SPI接口是同步串行總線的一種,在同步時鐘信號SCK下,能夠高速、可靠的傳送數(shù)據(jù)。它分為主從(MASTER/SLAVER)兩種傳輸模式。主模式下的發(fā)送總線即是從模式的接收總線:與之對應(yīng)的是從模式下的發(fā)送總線即是主模式的接收總線。它們可以同時接收和發(fā)送數(shù)據(jù).而且發(fā)送和接收操作可以通過中斷或者查詢方法來完成。

2.2.1 工作時鐘

時鐘極性CPOL和時鐘相位CPHA控制著時鐘信號引腳上4中不同的時鐘方式。在設(shè)備被使能激活后.還未進行數(shù)據(jù)傳輸時或兩個字節(jié)數(shù)據(jù)間歇期間,SCK處于空閑電平,通過時鐘極性控制位可以選擇此空閑電平的電平時0還是1:時鐘相位控制位用來選擇數(shù)據(jù)接收端設(shè)備的采樣時刻。在該采樣時刻,線上數(shù)據(jù)必須同時滿足建立時間和保持時間兩個參數(shù),因此數(shù)據(jù)發(fā)送端設(shè)備應(yīng)提前將數(shù)據(jù)移出到數(shù)據(jù)線上。

4種不同的時鐘方式能根據(jù)外設(shè)需要,能夠提供相對應(yīng)的傳輸協(xié)議來完成數(shù)據(jù)的傳輸工作。它們之間沒有優(yōu)先級.SPI線上的主從設(shè)備必須根據(jù)具體情況設(shè)置匹配的傳輸時序模式.時序只有匹配擻據(jù)傳輸才能正常進行。如果設(shè)置的不匹配.可能導(dǎo)致數(shù)據(jù)接收方和發(fā)送方在同一個時鐘沿作用.導(dǎo)致數(shù)據(jù)輸出失敗。

圖2是CPHA=0時的數(shù)據(jù)傳輸時序.它同時包含了CPOL=0和CPOL=1的情況,當(dāng)CPOL=O時,要傳輸?shù)臄?shù)據(jù)在時鐘信號沒有延時且上升沿出發(fā)送,在時鐘信號下降沿處接收數(shù)據(jù)。當(dāng)CPOL=1時,同樣在沒有延時的情況下傳輸,不同的是下降沿發(fā)送數(shù)據(jù),上升沿接收。圖3是CPHA=1時數(shù)據(jù)傳輸時序。與圖2相似,但采樣時刻延遲了半個周期。

圖2 CPHA="0是SPI總線數(shù)據(jù)傳輸時序"

圖3 CPHA="1時SPI總線數(shù)據(jù)傳輸時序"

3 SPI硬件設(shè)計

寄存器在SPI中起著決定性的作用.無論是在微控制器接口,還是SPI控制接口,寄存器在數(shù)據(jù)傳輸和控制方面都是主要的組成部分。而寄存器最基本最重要的單元是觸發(fā)器.只有改善觸發(fā)器的結(jié)構(gòu),才能提高整個SPI接口的性能。

有的串行接口設(shè)計中采用B結(jié)構(gòu)的觸發(fā)器設(shè)計,這些結(jié)構(gòu)里應(yīng)用的是一種簡單的MOS管做開關(guān).雖然MOS管做開關(guān)有功耗低,占面積小的優(yōu)點。但要提高它的電路工作頻率.開關(guān)速度,制作丁藝卻是越來越困難。而且如果輸入信號不強.就很可能出現(xiàn)信號倒流,這就需要一個較高電壓來控制開關(guān)。這也不利于數(shù)據(jù)傳輸和降低功耗等等。

為了解決由MOS管做開關(guān)時引起的種種難題.來實現(xiàn)在TMS320LF2407串行接口中的信息傳遞的高速率。本設(shè)計綜合考慮速度、工作電壓、噪聲容限等因素的影響.采用了一種新穎的觸發(fā)器結(jié)構(gòu)(圖4A部分),本文接口電路中大都采用了該觸發(fā)器的電路設(shè)計,工作電壓降低到3.3V,大大降低了整體功耗;在開關(guān)方面采用了三態(tài)門,有效的防止了信號倒流,實現(xiàn)了信號傳輸?shù)姆€(wěn)定;添加了一個反饋信號,在需要的時候.能夠把所需反饋信號再次輸入;同時加快r開關(guān)速率,帶負(fù)載的能力也增強。

圖4 A、B兩種觸發(fā)器比較

4 RTL級設(shè)計

隨著數(shù)字系統(tǒng)設(shè)計的復(fù)雜性不斷增加,在設(shè)計初期指定有效的設(shè)計策略對于整個設(shè)計是至關(guān)重要的。行為描述方式是對系統(tǒng)數(shù)學(xué)模型的描述。它包括RTL、算法級、系統(tǒng)級的描述。RTL是指通過描述寄存器之間數(shù)據(jù)流動來描述數(shù)字電路系統(tǒng),是一個數(shù)據(jù)流的概念.寄存器與寄存器之間的數(shù)據(jù)處理由組合邏輯完成。RTL級是Verilog較高抽象層次,在這個抽象層次上,模塊可以根據(jù)設(shè)計的算法來實現(xiàn).而不用考慮具體的實現(xiàn)細(xì)節(jié)。

4.1寄存器整體電路設(shè)計

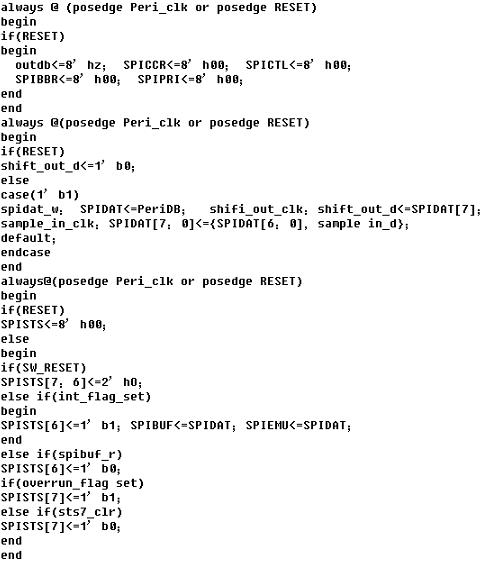

下面是部分Verilog HDL源代碼.描述了數(shù)據(jù)傳輸時相關(guān)寄存器的功能設(shè)置:先是對復(fù)位時各個寄存器的初始值,接下來是對寄存器進行功能設(shè)計.和數(shù)據(jù)傳輸時候產(chǎn)生的中斷使能和標(biāo)志位的設(shè)計。

4.2整體時序仿真

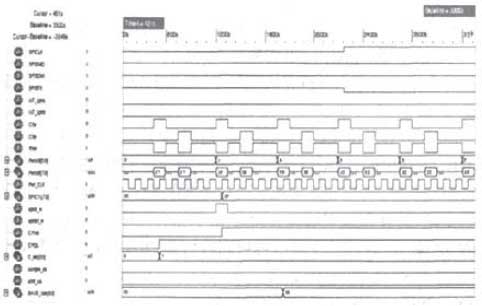

將上述Verilog代碼編譯,再寫上對應(yīng)測試代碼進行驗證。圖5是寄存器的寫操作的整體時序仿真波形圖.驗證了上述代碼正確可行。

圖5寫操作整體時序仿真

5 結(jié)論

本文作者的創(chuàng)新點是改進了硬件觸發(fā)器的結(jié)構(gòu).用三態(tài)門和傳輸門取代那種單一MOS管的結(jié)構(gòu)。首次應(yīng)用到TMS320LF2407芯片串行外設(shè)接口上,降低工作電壓到3.3V,加快數(shù)據(jù)傳輸,而且還有相應(yīng)的反饋信號,進一步完善了觸發(fā)器結(jié)構(gòu)。同時有很好的可移植性好。具有充分的可裁剪性,本設(shè)計運行可靠,達(dá)到預(yù)期的效果。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。