在今年電腦硬體的熱門話題中,USB3.0絕對是最受矚目的。自從西元2000年USB2.0釋出后,這項應(yīng)用已深植各項電子產(chǎn)品中,在各式各樣的連接埠規(guī)格中, USB應(yīng)可算是使用最廣泛的了。USB3.0的資料傳輸速率比現(xiàn)有的USB2.0快上十倍,剛好迎合日益大增的高畫質(zhì)、大容量儲存需求。無論是外接式硬碟、隨身碟、相機(jī)記憶卡均可大幅縮減儲存的時間。除了在電腦上的應(yīng)用之外,手機(jī)與相機(jī)的傳輸也幾乎都是使用USB規(guī)格,甚至許多產(chǎn)品更直接把充電端與USB結(jié)合,難怪各界皆如此期待USB3.0的廣泛使用,好讓使用者享受4.8Gbps的傳輸快感。USB3.0介面分成主機(jī)(Host)端與裝置(Device)端,必須先有Host端的支援,周邊的Device端才能搭配;而晶片大廠英特爾及超微自2010年起亦已開始研發(fā)將支援USB3.0為南橋規(guī)格,加上微軟Windows 7也確定研發(fā)支援USB3.0的drivers,預(yù)估USB 3.0取代USB2.0已是既定趨勢。

為實現(xiàn)十倍于USB2.0的傳輸速度,USB 3.0控制晶片必須使用更先進(jìn)的制程來設(shè)計與制造,但這也造成USB 3.0的控制晶片對ESD的耐受能力快速下降。除此之外,USB 3.0會被大量用來傳輸影音資料,對資料傳輸容錯率會有越嚴(yán)格的要求,使得使用額外的保護(hù)元件來防止ESD事件對資料傳輸?shù)母蓴_變得很必要。除了傳輸速度的要求之外,另一個使用者最普遍的USB應(yīng)用就是隨插即用、隨拔即關(guān)。然而這個熱插拔動作卻也經(jīng)常是造成電子系統(tǒng)工作異常、甚至造成USB連接埠元件毀壞的元兇,因為如靜電放電(ESD)等暫態(tài)雜訊就是來自這個熱插拔動作。

要用在USB3.0連接埠的ESD防護(hù)元件必須同時符合下面三項要求:

第一、ESD防護(hù)元件本身的寄生電容必須要小,為不影響USB3.0 4.8Gbps的傳輸速率,其寄生電容必須小于0.3pF。

第二、防護(hù)元件對ESD的耐受能力必須要高,最少要能承受IEC 61000-4-2接觸模式8kV ESD的轟擊。

第三、也是最重要的一項要求,防護(hù)元件在ESD事件發(fā)生期間所提供的箝制電壓必須要夠低,不能造成傳輸資料的損壞。

以上三項要求缺一不可,缺少了任何一個要項,USB3.0連接埠就無法被完善地保護(hù)。然而要同時符合以上三項要求的ESD防護(hù)元件,其本身的設(shè)計難度就相當(dāng)高。

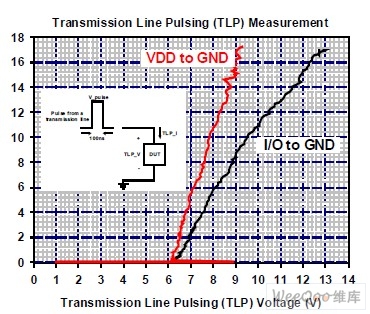

晶焱科技擁有先進(jìn)的ESD防護(hù)設(shè)計技術(shù),特別針對USB3.0的防護(hù)需求,推出AZ1065系列的ESD防護(hù)元件。為避免防護(hù)元件的寄生電容影響USB3.0 4.8Gbps差動(Differential)訊號的高速傳輸,AZ1065的寄生電容已低于0.3pF。在極低的電容特性下,任一接腳在室溫時仍皆可承受IEC 61000-4-2接觸模式10kV ESD的轟擊。最重要是,以相同寄生電容來比較,AZ1065擁有最低的ESD箝制電壓,可有效防止資料傳輸時被ESD事件所干擾,才能讓擁有USB 3.0連接埠的電子系統(tǒng)有機(jī)會通過Class-A的IEC 61000-4-2系統(tǒng)級靜電放電保護(hù)測試。利用傳輸線脈沖系統(tǒng)(TLP)測量AZ1065后,可以觀察到如圖一的ESD箝制電壓特性。在IEC 61000-4-2接觸模式6kV的ESD沖擊下(TLP電流等效約為17A),箝制電壓僅有13.4V,將得以有效避免系統(tǒng)產(chǎn)品于靜電測試時發(fā)生資料錯誤、當(dāng)機(jī)甚至損壞的情況。

附圖一 AZ1065-06F的ESD箝制電壓測試曲線

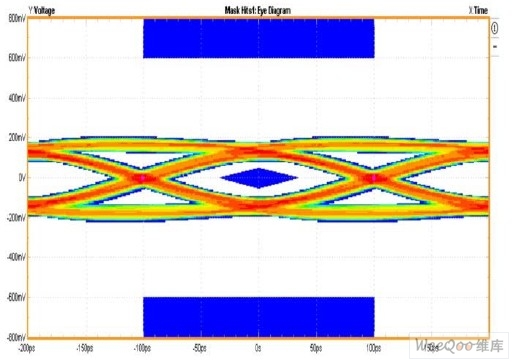

在電子產(chǎn)品的USB3.0應(yīng)用中,AZ1065-06F將是靜電放電防護(hù)的最佳解決方案。圖二所示即為裝有ESD防護(hù)元件AZ1065-06F的USB3.0連接埠順利通過5Gbps的Eye Diagram測試結(jié)果。

附圖二 AZ1065-06F 5Gbps的Eye Diagram測試結(jié)果

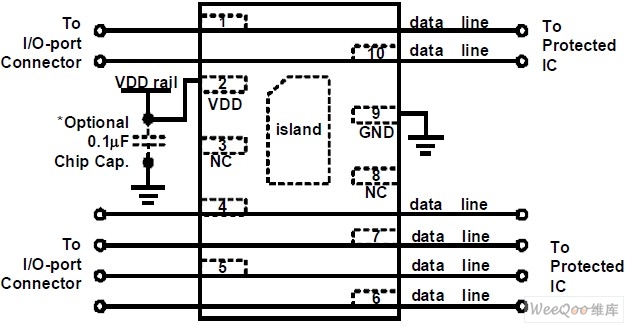

在電子產(chǎn)品朝向輕薄短小的發(fā)展趨勢下,產(chǎn)品的印刷電路板(PCB)也隨之越來越小,但在產(chǎn)品功能強(qiáng)大的要求之下,線路也變得更加復(fù)雜,因此PCB的面積已變得寸土寸金,造成產(chǎn)品設(shè)計時相當(dāng)大的困擾。AZ1065系列產(chǎn)品提供六個極低電容的接腳,可同時保護(hù)USB3.0的兩組差動對(TX and RX)及USB2.0的差動對(D+ and D-),具有縮小PCB面積與降低布局(Layout)復(fù)雜度等優(yōu)點,可節(jié)省系統(tǒng)成本。更特別的是AZ1065-06F首先采用交錯型式的接腳,以提供PCB Layout時可利用穿透式(Feedthrough)的設(shè)計,圖三即為AZ1065-06F的接線方式。此種首創(chuàng)的元件接腳方式將可免除繞線時的諸多困擾,不但對縮短產(chǎn)品設(shè)計階段的PCB Layout工作有相當(dāng)大的幫助,同時差動訊號線的Layout也將更為對稱,減少訊號傳輸錯誤的機(jī)會。

附圖三 以AZ1065-06F作為USB3.0 ESD防護(hù),線路可利用穿透式Layout達(dá)成