基于JTAG仿真器的DSP中斷檢測處理技術

摘要: 數字信號處理技術是一門發(fā)展很快的新興學科,它的應用十分廣泛,如通訊、控制、圖像和語音處理、測量與控制、醫(yī)學等。[2]數字信號處理平臺主要有 DSP、單片機、通用 /工控計算機、FPGA/CPLD等,文章主要介紹了在進行數字信號處理時,利用 JTAG(Joint TEST Advisory GROUP)技術的仿真器在 CCS平臺下對 TMS320 C54x系列 DSP芯片實現在線編程,進行在線調試時中斷檢測處理技術及其應用。

Abstract:

Key words :

摘要:數字信號處理技術是一門發(fā)展很快的新興學科,它的應用十分廣泛,如通訊、控制、圖像和語音處理、測量與控制、醫(yī)學等。[2]數字信號處理平臺主要有 DSP、單片機、通用 /工控計算機、FPGA/CPLD等,文章主要介紹了在進行數字信號處理時,利用 JTAG(Joint TEST Advisory GROUP)技術的仿真器在 CCS平臺下對 TMS320C54x系列 DSP芯片實現在線編程,進行在線調試時中斷檢測處理技術及其應用。

1、引言

在采用集成化的開發(fā)調試平臺CCS結合基于JTAG技術的仿真器實現 DSP系統(tǒng)的實時性分析過程中設定中斷檢測點是非常重要的,中斷檢測點可以中斷程序的執(zhí)行以進行特定的操作,例如可以進行數據文件的輸入輸出,可以刷新圖表和數據窗口等,便于在實時性分析中更有效的觀察數據處理的顯示結果。 2、基于 JTAG技術的仿真器

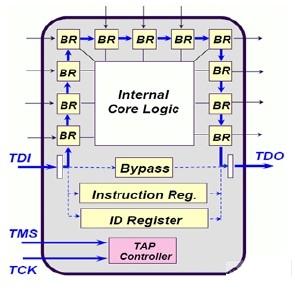

JTAG技術即邊界掃描技術,是一種專用的電子系統(tǒng)測試技術,就是通常所指的 IEEE1149.1標準,已經在各行業(yè)中得到了廣泛的應用,如圖 1,一個符合 IEEE1149.1標準的 JTAG器件,有別于不同的邏輯器件,內部都包括一個 TAP(測試訪問端口)控制器,其次在芯片內部經由一個掃描鏈路將所有的輸入和輸出管腳全部串入一個掃描鏈路。

圖 1 JTAG器件

基于 IEEE1149.1標準的邊界掃描技術最先應用于大規(guī)模集成電路以及系統(tǒng)級芯片設計的 DFT技術,不僅可以保證集成電路芯片的外圍管腳部分邏輯的正確,同時也對于嵌入在芯片內部的自測試機制等起到整合和控制等方面的作用。其次,通過芯片的 JTAG接口可以實現包括 FPGA、DSP以及處理器等在內的集成電路芯片的在線編程,同時也可以實現芯片的在線調試,前者是應用這一模式實現設計的下載,后者利用虛擬在線調試技術就是將芯片運行過程中部分的內部邏輯信息透過 JTAG接口傳送到計算機中進行分析和判讀。第三,基于 JTAG標準的邊界掃描技術可以應用在印刷電路板的連通性測試領域,通過將 JTAG器件的邊界掃描鏈連接在一起,并且控制合適的數據信息在該掃描鏈中傳遞,從掃描鏈的輸出端進行監(jiān)控就可以判別有關印刷電路板連通性以及元器件功能等方面的問題。

基于 JTAG技術的仿真器是用來進行芯片硬件仿真,如程序單步執(zhí)行、設置中斷檢測點等,通過硬件仿真可以了解芯片里面程序的詳細運行情況。 JTAG仿真器主要用來對芯片進行仿真操作,同時也可以通過 JTAG接口對芯片編程(將程序寫入芯片)。它的接口方式有LPT(并行)口,PCI或ISA卡,USB口。JTAG仿真器一端通過USB口與PC機連接, 另一端通過 JTAG插頭與 DSP目標板連接;建議首先連接 JTAG仿真器到 PC機, 再連接到 DSP目標板。[8] 3、基于 TMS320 C54XDSP芯片的信號發(fā)生器

3.1 TMS320 C54x系列 DSP芯片

TMS320 C54x系列 DSP芯片是使用靜態(tài) CMOS技術制造的。該芯片采用改進哈佛結構,對程序內存和數據內存使用分離的總線;可以同時取指令和操作數,提高了運行效率和通用性先進的 CPU設計和為應用設計的硬件邏輯提高了芯片的性能;為快速的后續(xù)發(fā)展設計了模塊化的結構;為先進的 IC處理技術提供了高性能和低功耗;高度專門的指令結構提供了快速運算和優(yōu)化的高階語言操作;具有單指令循環(huán)和塊指令循環(huán)功能;塊內存移動指令提供了更好的程序和數據管理;擁有兩個或三個操作數讀取能力的指令;從中斷快速返回的指令擁有多種片上外設和內存配置方案等特點。

3.2信號發(fā)生器

一 )連接硬件,首先給 DSP目標扳加電,指示燈亮。

一 CCS運行環(huán)境。

一 )建立新項目,并在項目中添加相關文件。

一 Project 菜單中 open選項,在彈出的對話框中選擇信號發(fā)生器的編譯工程。

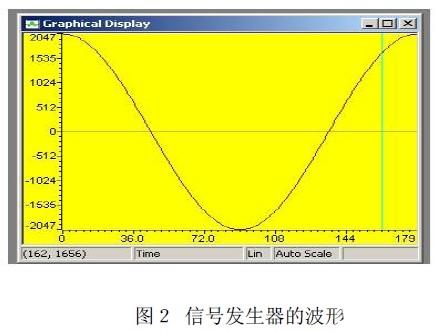

一 Project 菜單中 Rebuild All選項,編譯鏈接該工程,沒有錯誤后,選擇 File菜單中 Load Program選項,選擇 *.C文件,進行加載程序。選擇 View菜單中 graph選項中 Time/Frequency設置圖形屬性,選擇 Start Address 為 DACdata ,設 Acquisition Buffer Size為 180 ,設 Display Data Size為180 ,設 Dsp Data Type為 16-bit signed integer。點擊 OK ,觀察信號發(fā)生器的波形,如圖2:

4、DSP/BIOS 應用及實時性分析

4.1 DSP/ BIOS的分析特性:

程序跟蹤:顯示寫入目標日志的事件并在程序執(zhí)行過程忠反映動態(tài)控制流程。

性能監(jiān)控:跟蹤、統(tǒng)計目標板資源的使用情況。

文件流:將目標板上的 I/O對象與主機上的文件聯系在一起。其中:

1)DSP/ BIOS==Statistics View 統(tǒng)計表用于對程序的執(zhí)行周期進行統(tǒng)計。

2)DSP/BIOS==Execution Graph 執(zhí)行圖以圖示方式來反映程序執(zhí)行時各進程間的配合,以分析程序執(zhí)行的實時性。

3)DSP/BIOS==RTA Control Panel 控制儀表可以實時調整信息搜集和由此造成的對 CPU的干擾之間,通過禁止不同的隱式儀表類型,用戶會丟失一些信息來換取減少開銷。

4)DSP/ BIOS==CPU Load Graph ,CPU負荷圖窗口,CPU活動分為兩部分:工作時間和 IDLE時間。即 CPU負荷定義為執(zhí)行一個應用程序時,CPU花費的指令周期數的百分比。

4.2 DSP/BIOS 實時性分析

一 )連接硬件,首先給 DSP目標扳加電,指示燈亮。

一 CCS運行環(huán)境。

一 )建立新項目,并在項目中添加相關文件。

一 )選擇Project 菜單中 open選項,在彈出的對話框中選擇編譯工程*.cmd。

一 )選擇Project 菜單中 Rebuild All選項,編譯鏈接該工程,沒有錯誤后,選擇 File菜單中 Load Program選項,選擇文件,進行加載程序。

一 )選擇DSP/BIOS 菜單中CPU Load Graph , Execution Graph , Statistics View ,RTA Control Panel , Message Log 選項。

一 RTA Control Panel Properties 對話框,將 CPU Load Graph 改為 Every 0.5 Seconds 。[5]

一 )執(zhí)行程序,執(zhí)行圖窗口如圖3下:

如圖3 執(zhí)行圖窗口

5、DSP的中斷檢測處理:

1 )連接硬件,首先給 DSP目標扳加電,指示燈亮。

2 ) CCS運行環(huán)境。

3 )建立新項目,并在項目中添加相關文件。

4 )選擇Project 菜單中open選項,在彈出的對話框中選擇編譯工程。

5 )選擇Project 菜單中 Rebuild All選項,編譯鏈接該工程,沒有錯誤后,選擇 File菜單中 Load Program選項,選擇文件,進行加載程序。

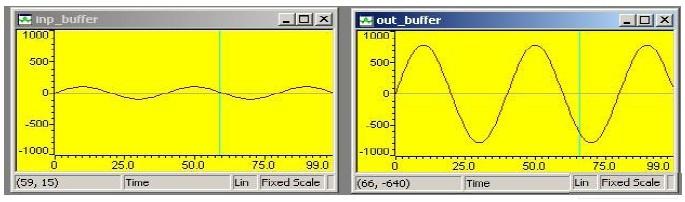

6 )選擇File菜單中File I/O 選項,在對話框中Address 輸入為Inp_buffer ,Legth為 100 ,進行鏈接,加載程序。

7 )將光標移至設定行 data IO ( ),設置中斷點和探測點,選擇 Debug菜單中 Breakpoints選項和 Probe Points 選項。

8 )選擇View菜單中Watch Windows 選項和graph 選項,在graph 選項中 Time /Frequency選項中設置輸入圖形屬性,設 Start Address 為inp_buffer ,Graph Title 為 inp_buffer ,Acquisition Buffer Size為 100,Display Data Size 為 100 , Maximum Y_Value 為 1000 , Autoscale為 off ,同時設置輸出波形的屬性。[4]

9 )執(zhí)行程序,觀察輸入輸出波形。如圖4:

圖4設有中斷檢測點的輸入輸出波形

6、結束語

文章討論了運用 JTAG仿真器在 CCS軟件平臺下對 TMS320 C54x系列 DSP芯片實現在線編程,在線調試時中斷檢測的處理,這樣基于 JTAG仿真器的 DSP中斷檢測處理技術可以滿足實時性分析的一些需求,提高了研究分析的精確性和針對性。但如果信號的測量需要更高精度、長時間的校準分析、更高性能的結果,最好選用嵌入式的仿真器及其相關專有的軟件。

此內容為AET網站原創(chuàng),未經授權禁止轉載。