上一小節(jié)簡單介紹了,共模抑制比的定義,以及引起它的原因。下面就介紹一下,它的影響。本系列貼子的目的是說清楚運(yùn)放參數(shù)的定義,分析引起這個(gè)問題的原因,介紹明白這個(gè)參數(shù)對(duì)電路的影響,最后盡力介紹一些經(jīng)驗(yàn)方法來盡可能的減少和避免這些影響。

簡單來說,CMRR是運(yùn)放的一個(gè)直流精度參數(shù),它的好壞,會(huì)引起運(yùn)放的放大電路的輸出誤差的好壞。

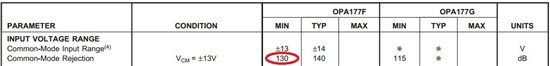

下表是OPA177的datasheet中標(biāo)出的共模抑制比CMRR,注意表中標(biāo)定的值是指,在輸入共模電壓范圍內(nèi)的直流共模抑制比。它的最小值為130dB,是非常高的值。

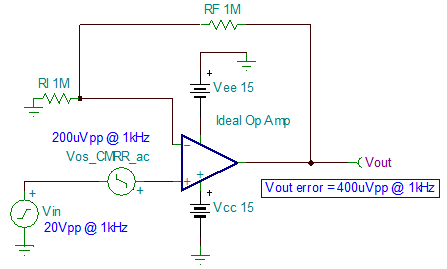

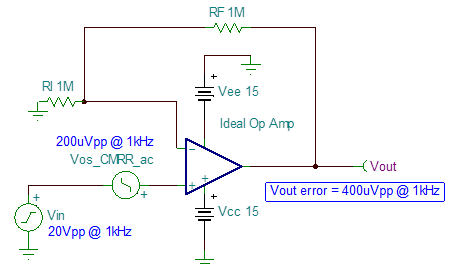

由于CMRR是有限值,當(dāng)運(yùn)放輸入端有共模電壓Vcm時(shí),它會(huì)引入一個(gè)輸入失調(diào)電壓,我們稱之為Vos_CMRR。如下圖所示

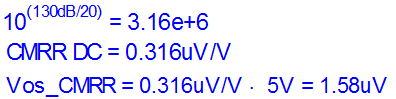

當(dāng)共模電壓為5V時(shí),這個(gè)失調(diào)電壓為1.58uV。計(jì)算過程如下,直流共模抑制比轉(zhuǎn)化為比率為:

對(duì)于上圖中的G=2的電路,則輸出端誤差為3.16uV。對(duì)于基準(zhǔn)源為2.5V,雙極性輸入的24位ADC來說,為相當(dāng)于引起了11個(gè)LSB的直流誤差了,直接影響到最后四位的精度了。

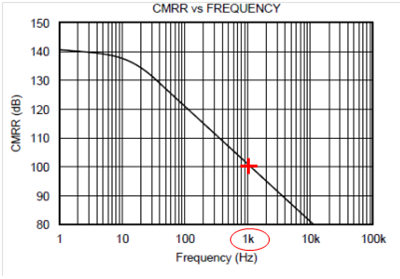

下面介紹另一個(gè)不好的影響,運(yùn)放的CMRR是隨頻率的增加而降低。Datasheet中通常會(huì)給出一個(gè)曲線圖來表示這一變化。如下圖,這一點(diǎn)是一個(gè)非常令人不爽的特性。

我們可以計(jì)算一下這一特性的影響,如下圖所示,當(dāng)共模信號(hào)為一個(gè)20Vpp@1KHz的正弦信號(hào)時(shí),它引入的輸入失電壓將是Vos_CMRR_AC=200uV@1kHz。對(duì)于Gain=2的放大電路,它的輸入誤差信號(hào)將為 400uV@1kHz。

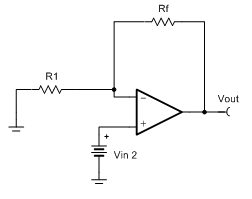

有一點(diǎn)需要引起注意,對(duì)于反向比例放大電路,如下圖,它的同向端是接入到地的,由于“虛短”。此放運(yùn)放的共模信號(hào)將為0,并且不隨信號(hào)的變化而改變。因此共模信號(hào)引起的誤差很小。

而對(duì)于同向比例放大電路,如下圖,它的同向端是接是接的信號(hào),由于“虛短”。此放運(yùn)放的共模電壓就是信號(hào)的電壓。如果信號(hào)本身是一個(gè)頻率很高的信號(hào),幅值也很大。那么由這個(gè)信號(hào)引 入的Vos_CMRR_AC執(zhí)必會(huì)非常大。此時(shí)應(yīng)選用在信號(hào)頻率上 CMRR依然很高的運(yùn)放。經(jīng)過上面的分析,即使這樣,Vos_CMRR_AC的影響可能也會(huì)是非常嚴(yán)重的。

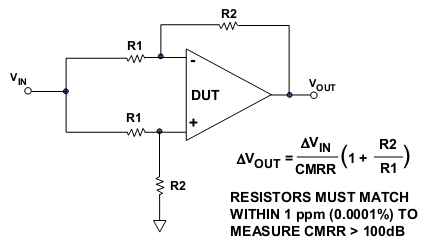

最后簡單介紹一下運(yùn)放的CMRR測(cè)試,通常人們會(huì)想到有下圖的方法來測(cè)試CMRR,這種方法看似簡單,但存在一個(gè)很大的問題,就是它需要的電阻匹配度非常高,為發(fā)測(cè)CMRR>100dB的運(yùn)放,需要1ppm以下的電阻。這幾乎不實(shí)用。

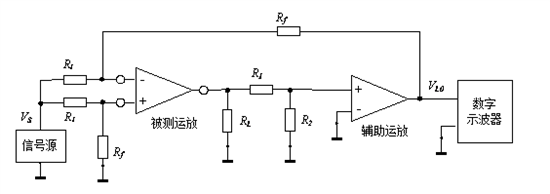

簡單易行的方式是下圖的方式。它對(duì)電阻的匹配度要求要低的多。

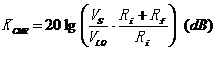

設(shè)信號(hào)源輸出電壓為VS,測(cè)得輔助運(yùn)放輸出電壓為VL0,則有