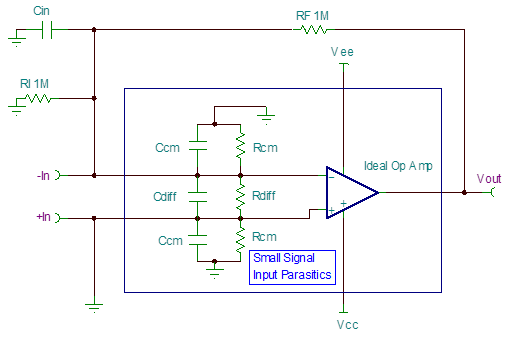

下圖形象的說明了運(yùn)放的輸入端阻抗的特性。主要有兩個(gè)參數(shù),輸入阻抗和輸入電容。對(duì)于電壓反饋型運(yùn)入,輸入阻抗主要由輸入級(jí)的決定,一般BJT輸入級(jí)的運(yùn)放。的共模輸入阻抗會(huì)大于40MΩ。差模輸入阻抗大于200GΩ。對(duì)于JFET和CMOS輸入級(jí)的運(yùn)放,輸入阻抗要大的多。這個(gè)阻抗通常表現(xiàn)為電阻性。作為常識(shí)被我們所熟知。

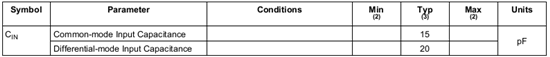

更值得我們多加關(guān)注的是運(yùn)放的輸入電容。這個(gè)參數(shù)通常在datasheet的表格中所列出,但常被忽視。運(yùn)放的輸入電容,通常分為共模輸入電容Ccm和差模輸入電容Cdiff。如下面是OPA376的datasheet中列出的輸入電容。

對(duì)于有EMI抑制特性的運(yùn)放,如LMV832,它的輸入電容會(huì)被設(shè)計(jì)的正大的些。下面是帶EMI抑制功能的LMV832的輸入電容值。

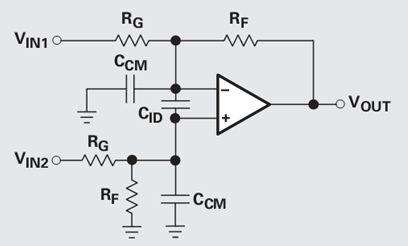

運(yùn)放的輸入共模電容Ccm 和差模電容 Cdiff會(huì)形成運(yùn)放的輸入電容 Cin。在許多應(yīng)用中,運(yùn)算放大器的輸入電容都不會(huì)造成問題。但在某些應(yīng)用中會(huì)引起放大電路的不穩(wěn)定。尤其是反向輸入端的電容,是放大電路不穩(wěn)定的幾大罪魁禍?zhǔn)字弧H缦聢D所示是運(yùn)放在有輸入電容的影響下的模型。

這個(gè)反向輸入端的電容會(huì)在運(yùn)放的環(huán)路增益中引入一個(gè)極點(diǎn)。正是這個(gè)極點(diǎn)的存在,在某些條件下,可能會(huì)引起放大電路的不穩(wěn)定。

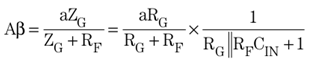

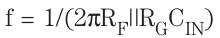

運(yùn)放輸入電容引入的極點(diǎn)如下式。即使這個(gè)極點(diǎn)0-dB交截越頻率之內(nèi),而是非常靠近0-dB交越頻率,它也有可能引起問題。在這個(gè)極點(diǎn)的頻率點(diǎn)上,相位會(huì)有45度的相位延遲,它很可能減少放大電路的相位裕度。如放大電路的0-dB交截越頻率是2MHz。在2MHz處的相位裕度是89°。 如果這個(gè)極點(diǎn)的頻率點(diǎn)也在2MHz處,它將使相位裕度減少45°。而變?yōu)?phi; = 89° – 45° = 44°。 44度的相位裕度就顯得的不夠了。

通常放大電路的輸入電容不只由運(yùn)放的輸入電容組成,還包括布線引起的雜散電容和引腳電容。應(yīng)盡量避免運(yùn)算放大器反相輸入端存在外部雜散電容,尤其是在高速應(yīng)用中。反相輸入周圍區(qū)域應(yīng)去除接地層,從而最大程度地減小PC板雜散電容,此外,該引腳的所有連接都應(yīng)盡量短。

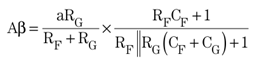

在一些應(yīng)用,常會(huì)加入反饋電容來增加放大電路的穩(wěn)定,加入反饋電容后的電路的環(huán)路增益為,可見反饋補(bǔ)償電容給環(huán)路增益中引入了一個(gè)零點(diǎn)。

關(guān)于運(yùn)放電路穩(wěn)定性,可以參閱Tim Green的系列文章。

Operational Amplifier Stability。