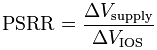

這一小節(jié)談?wù)勥\(yùn)放的電源抑制比,。在理想運(yùn)放中,運(yùn)放的特性不會隨電源電壓的變化而變化,。當(dāng)然,分析理想運(yùn)放時(shí),,我們使用的電源,,也會被假設(shè)成理想電源。但實(shí)際情況并非如此,,實(shí)際的運(yùn)放,,電源電壓發(fā)生變化時(shí),總會引起運(yùn)放參數(shù)的變化,。這就引出運(yùn)放的一個(gè)重要參數(shù),,運(yùn)放的電源抑制比PSRR。維基百科中給出了PSRR的詳細(xì)定義,,就是當(dāng)運(yùn)放的電源電壓發(fā)生變化時(shí),,會引起運(yùn)放的輸入失調(diào)電壓的變化,(又是失調(diào)電壓),,這兩個(gè)變化的比就是運(yùn)放的PSRR,。如下式

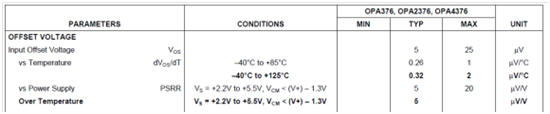

通常用dB表示,。PSRR = 20log(⊿Vcc/⊿Vios)。有些數(shù)據(jù)手冊中,,也會通過失調(diào)電壓對電源變化的比來表示,。單位一般用uV/V。如下圖,,是OPA365的datasheet中的表示,,這個(gè)也不難理解。我們不用為找不到上式定義的比率dB值,,而感動(dòng)傷心,。這兩種表示方法,都可以讓我們清楚的理解到運(yùn)放對電源電壓變化的抑制能力,。

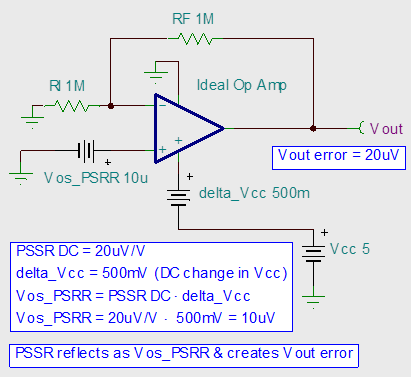

PSSR為有限值的原因,,也是來源于運(yùn)放差分輸入管的不完全匹配。下面著重討論它的影響,。如下圖是對OPA376運(yùn)放的一個(gè)計(jì)算實(shí)例,。當(dāng)電源電壓變化500mV時(shí),就會引起輸入失調(diào)電壓10uV的變化,,如果放大倍數(shù)為2,,剛輸出端變會產(chǎn)生20uV的變化。一些電路放大的倍數(shù)更大,,則輸出失調(diào)電壓變更大,。這足以使一個(gè)輸送給16bitsADC的信號產(chǎn)生誤差。(16位ADC的一個(gè)LSB對應(yīng)的變化為15ppm of FSR),。