隨著醫(yī)療、消費電子和工業(yè)市場上的便攜式手持儀器儀表日趨向尺寸更小、重量更輕、電池(或每次充電)續(xù)航時間更長、成本更低且通常功能更多方向發(fā)展,低功耗已經(jīng)成為如今電池供電模數(shù)轉(zhuǎn)換器應(yīng)用的一項關(guān)鍵要求。即使是在非電池供電的應(yīng)用中,低功耗的好處也不容忽視,因為低功耗系統(tǒng)無需散熱器或風(fēng)扇也能工作,因而尺寸更小、成本更低,而且更加可靠,同時也"更加綠色環(huán)保".此外,許多設(shè)計人員在設(shè)計產(chǎn)品時都面臨一個挑戰(zhàn),即在增強產(chǎn)品功能或性能的同時降低或者至少不得超過當前的功耗預(yù)算。

當今市場上品種繁多的ADC則使得選擇符合特定系統(tǒng)要求的最佳器件變得更加困難。如果說低功耗是必須的條件,那么除了評估速度和精度等常見的轉(zhuǎn)換器性能特性之外,還需要考慮更多性能指標。了解這些指標以及設(shè)計決策會對功耗預(yù)算有何影響,對于確定系統(tǒng)功耗和電池壽命計算非常重要。

ADC的平均功耗是轉(zhuǎn)換期間所用功耗、不轉(zhuǎn)換時所用功耗以及各模式下所用時間的函數(shù),如等式1所示。

PAVG = 平均功耗。

PCONV = 轉(zhuǎn)換期間的功耗。

PSTBY = 待機或關(guān)斷模式下的功耗。

tCONV = 轉(zhuǎn)換所用時間。

tSTBY = 處于待機或關(guān)斷模式的時間。

轉(zhuǎn)換期間所用功耗通常遠大于待機功耗,因此如果處于待機模式的時間增加,平均功耗會顯著降低。逐次逼近(SAR)型轉(zhuǎn)換器尤其適合此類工作模式

影響系統(tǒng)電源使用情況的最大因素之一是板上電源的選擇。對于便攜式應(yīng)用,系統(tǒng)通常由3 V紐扣式鋰電池直接供電。這樣就無需使用低壓差穩(wěn)壓器,從而節(jié)省電能、空間和成本。非電池應(yīng)用也可受益于具有低VDD電源電壓范圍的轉(zhuǎn)換器,因為功耗與輸入電壓成正比。為VDDADC選擇最低可接受VDDVDD將可降低功耗。

針對低功耗應(yīng)用的所有ADC都具有關(guān)斷或待機模式,以便在閑置期間節(jié)省電能。ADC可以在單次轉(zhuǎn)換之間關(guān)斷,或者以高吞吐速率突發(fā)執(zhí)行一陣轉(zhuǎn)換,在這些突發(fā)之間關(guān)斷ADC.對于單通道轉(zhuǎn)換器,工作模式的控制功能可以集成到通信接口,或者在完成一次轉(zhuǎn)換后自動進行。

將模式控制集成到通信接口的好處是可以減少引腳數(shù)量。這樣可以降低功耗,因為要驅(qū)動的輸入更少,同時漏電流也更小。此外,引腳數(shù)量越少,封裝尺寸也就越小,同時MCU所需的I/O也越少。無論采用何種控制方法,只要謹慎使用這些模式都能顯著節(jié)省電能。

顧名思義,關(guān)斷模式會關(guān)閉部分ADC電路,從而降低功耗。關(guān)斷后電路重新啟動轉(zhuǎn)換所需的時間決定可有效使用此類模式的吞吐速率。對于帶有內(nèi)部基準電壓源的ADC,重新啟動時間將由基準電容重新充電所需的時間決定。采用外部基準電壓源的模數(shù)轉(zhuǎn)換器需要足夠的時間在重新啟動時正確跟蹤模擬輸入。

對于當今市場上的所有ADC,功耗均與吞吐速率成正比。功耗由靜態(tài)功耗和動態(tài)功耗組成。靜態(tài)功耗是恒定的,動態(tài)功耗則和吞吐速率呈線性變化關(guān)系。因此,在滿足應(yīng)用要求的前提下盡可能選擇最低的吞吐速率可以省電。

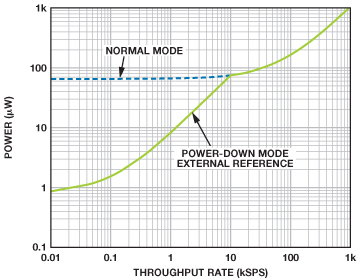

圖1所示為AD7091R,的典型功耗與吞吐速率的函數(shù)關(guān)系,該器件是ADI公司最近推出的超低功耗ADC.圖中還比較了利用器件的關(guān)斷模式(尤其是在較低吞吐速率條件下)可以帶來怎樣的額外省電效果。AD7091R的吞吐速率和關(guān)斷模式利用率取決于器件的重新啟動時間,以及基準電容的重新充電時間,因為AD7091R具有片內(nèi)基準電壓源。基準電容重新充電所需的時間取決于電容大小,以及片內(nèi)基準電壓源重新啟動時電容的剩余電荷水平。

圖1. AD7091R ADC功耗與吞吐速率的關(guān)系

ADC中啟動轉(zhuǎn)換請求的最常見方法是采用專用轉(zhuǎn)換輸入引腳或通過串行接口進行控制。采用專用輸入引腳(CONVST)時,轉(zhuǎn)換在下降沿啟動。然后,由片內(nèi)振蕩器控制轉(zhuǎn)換,轉(zhuǎn)換完成后,可通過串行接口回讀結(jié)果。因此,轉(zhuǎn)換始終以恒定的最佳速度運行,允許器件在轉(zhuǎn)換完成時進入低功耗模式,從而節(jié)省電能。

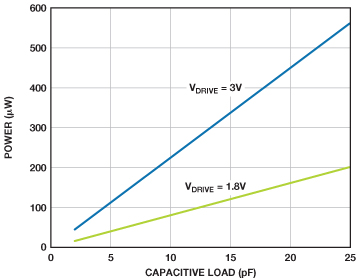

當ADC中的采樣時刻由片選(CS)上的下降沿啟動時,轉(zhuǎn)換由內(nèi)部采樣時鐘(SCLK)信號控制。SCLK頻率將會影響轉(zhuǎn)換時間和可實現(xiàn)的吞吐速率,進而影響功耗。SCLK速率越快,轉(zhuǎn)換時間就越短。轉(zhuǎn)換時間越短,器件處于低功耗模式的時間比例相對于正常模式就越大,因此可以實現(xiàn)顯著的省電效果。也就是說,如果每次轉(zhuǎn)換需要N SCLK周期,那么對于每秒執(zhí)行S次轉(zhuǎn)換,SCLK開關(guān)的總時間為S S × N/fSCLK每秒內(nèi)的靜態(tài)時間如等式2所示。

因此,對于給定的每秒采樣次數(shù),隨著fSCLK增加,每秒內(nèi)的靜態(tài)時間也會增加。

例如,假設(shè)完成轉(zhuǎn)換并讀取結(jié)果需要16個SCLK周期,則對于采樣速率為100 kSPS且SCLK為30 MHz的系統(tǒng),靜態(tài)時間所占比例為94.67%,也就是說轉(zhuǎn)換所用時間占5.33%(每秒內(nèi)53.3 ms)。當SCLK為10 MHz時,同一系統(tǒng)的靜態(tài)時間僅占84%,也就是說轉(zhuǎn)換用時為160 ms.因此,要實現(xiàn)最佳功耗性能,轉(zhuǎn)換器應(yīng)以可支持的最高SCLK頻率工作。

針對低功耗應(yīng)用而設(shè)計時,有個很重要的參數(shù)卻往往被忽視,即輸出引腳(尤其是SCLK、CS和SDO等通信接口引腳)上的容性負載,因為這些I/O變量會在轉(zhuǎn)換過程中不斷改變狀態(tài)。輸出端上的容性負載等于驅(qū)動器IC本身的引腳電容、輸入引腳的引腳電容以及PCB走線電容之和。走線電容通常都很小,處于飛法范圍內(nèi),因此意義不大。為容性負載充電所需的功率(PL)是負載(CL)、驅(qū)動電壓(VDRIVE)以及充電頻率(f)的函數(shù),其定義如等式3所示。

因此,整個系統(tǒng)的功率等于負載電容(CLn)和開關(guān)頻率(fn)乘積之和乘以驅(qū)動電壓的平方。

由于ADC驅(qū)動SDO引腳,主機微控制器驅(qū)動CS、CONVST和SCLK引腳,因此可通過盡可能減少所有器件的引腳電容來實現(xiàn)最低功耗。

對于CS和CONVST引腳,開關(guān)頻率僅取決于吞吐速率。如前所述,SCLK頻率應(yīng)設(shè)置為可支持的最大頻率,以便降低功耗。這并不矛盾:重要的是SCLK并不是自由運行--它應(yīng)該僅在盡可能短的時間內(nèi)激活,以便在SDO線路上傳播每個位檢驗的結(jié)果并控制轉(zhuǎn)換過程。這點依器件和分辨率而定,但通常為每位一個周期,再加上一些開銷;對于12位轉(zhuǎn)換器SPI接口,每次采樣約為16個SCLK周期。因此,SCLK的最小頻率為所需周期數(shù)乘以吞吐速率。

SDO線路的頻率取決于吞吐速率和轉(zhuǎn)換結(jié)果。雖然這個無法進行控制,但是設(shè)計人員應(yīng)該了解它會對轉(zhuǎn)換功耗造成什么影響。當結(jié)果為101010…序列時,功耗最大;當結(jié)果為全1或全0時,功耗最小。

除了降低吞吐速率之外,減小VDRIVE電壓也可明顯降低功耗。模數(shù)轉(zhuǎn)換器通過單電源引腳或單獨的電源來為模擬電路和數(shù)字接口供電。使用單獨的VDRIVE電源時,設(shè)計靈活性更高并且無需電平轉(zhuǎn)換器,因為模數(shù)接口電壓可與SPI主機的電壓相匹配。為VDRIVE 選擇可用的最低電壓時,系統(tǒng)功耗將最低。

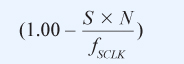

圖2比較了12位ADC在VDRIVE值為3 V和1.8 V時標準SPI接口(含CS、SDO和SCLK)的典型功耗要求與總?cè)菪载撦d的關(guān)系,其中吞吐速率為100 kSPS、每次轉(zhuǎn)換16個SCLK周期以及最差情況SDO輸出為1010.

圖2. 典型接口功耗與容性負載的關(guān)系

ADC電路設(shè)計的其它典型構(gòu)成要素包括基準電壓源和運算放大器。不言而喻,應(yīng)針對低功耗認真選擇這些元件。有些基準電壓源帶有關(guān)斷模式,以便在非活動期間降低功耗。放大器選擇視應(yīng)用而定,因此應(yīng)考慮到系統(tǒng)吞吐速率,以確保所選放大器能夠使ADC性能達到最佳,同時使功耗降至最低。

12位AD7091R專為低功耗應(yīng)用而設(shè)計,具有一個SPI接口和一個片內(nèi)精密2.5 V基準電壓源,采樣速率為1 MSPS.轉(zhuǎn)換通過CONVST引腳啟動。片內(nèi)振蕩器控制轉(zhuǎn)換過程,使之能夠優(yōu)化功耗。引腳電容很小,最大值為5 pF.寬輸入電壓范圍(2.7 V至5.25 V)允許集成到更廣泛的應(yīng)用中,而不僅僅是電池供電應(yīng)用。單獨的1.65 V至5.25 V VDRIVE電源則可降低功耗,并提高系統(tǒng)集成能力。

采樣速率為1 MSPS且VDD為3 V時,AD7091R功耗為349 μA(典型值)。由于其功率與吞吐速率成正比,因此100 kSPS時靜態(tài)電流為55 μA.不執(zhí)行轉(zhuǎn)換但基準電壓源激活時,靜態(tài)電流為21.6 μA;在關(guān)斷模式下,電流僅為264 nA.AD7091R采用10引腳MSOP或LFCSP封裝。

驅(qū)動AD7091R的典型放大器包括AD8031(針對快速吞吐速率應(yīng)用)和AD8420(針對較低帶寬應(yīng)用)。采用2.7 V電源供電時,AD8031的靜態(tài)功耗為750 μA(典型值);采用5 V電源供電時,AD8420的靜態(tài)功耗為70 μA(典型值)。

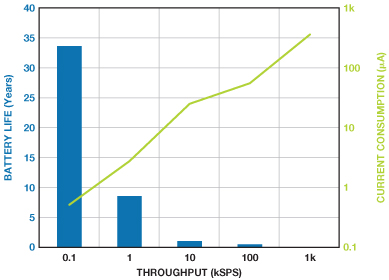

圖3所示為通過CR2032鋰電池供電時AD7091R的典型功耗和計算得出的電池壽命。可以清楚看出,隨著吞吐速率降低,電池壽命明顯延長。

圖3. AD7091R電池壽命和功耗與吞吐速率的關(guān)系

與多數(shù)其它ADC相比,AD7091R可以在功耗預(yù)算上實現(xiàn)顯著節(jié)省效果。例如,與最接近的可用競爭產(chǎn)品(一款不帶內(nèi)部基準電壓源的器件)相比時,對于1 MSPS吞吐速率,AD7091R可使功耗降低3倍(對于3 V電源,其功耗典型值為1 mW,而比較產(chǎn)品的功耗典型值為3.9 mW)。這相當于將CR2032電池壽命延長400小時。考慮需要外部基準電壓源的其它器件時,節(jié)省效果更為明顯。

結(jié)論

除延長電池壽命之外,降低功耗還有其它很多好處。產(chǎn)生的熱量變少,進而使尺寸變小。穩(wěn)定性因溫度應(yīng)力降低而得以提高。由于采用更小的元件,因此PCB尺寸得以縮小;另外,由于無需散熱器之類的配件,因此元件數(shù)量得以減少;這些使系統(tǒng)成本降低。

本文概述了系統(tǒng)設(shè)計人員在采用ADC的設(shè)計中優(yōu)化功耗時應(yīng)考慮到的幾個重要因素和好處。