0 引言

石英晶體諧振器(以下簡(jiǎn)稱石英晶體)廣泛用作時(shí)間頻率基準(zhǔn)和為時(shí)序邏輯電路提供同步脈沖。石英晶體的測(cè)試方法主要有阻抗計(jì)法,、π網(wǎng)絡(luò)最大傳輸法,、π網(wǎng)絡(luò)零相位法,其中π網(wǎng)絡(luò)零相位法是國(guó)際電工委員會(huì)(IEC)推薦的標(biāo)準(zhǔn)方法,。π網(wǎng)絡(luò)零相位法石英晶體測(cè)試設(shè)備在發(fā)達(dá)國(guó)家已廣泛使用,。典型儀器是美國(guó)S&A公司生產(chǎn)的250B零相位測(cè)試系統(tǒng),其測(cè)試頻率范圍為0.5~200 MHz,,串聯(lián)諧振頻率測(cè)試精度±2 ppm,。阻抗計(jì)型石英晶體測(cè)試設(shè)備在中國(guó)仍然占主導(dǎo)地位。阻抗計(jì)型石英晶體測(cè)試設(shè)備具有制造成本較低,,操作簡(jiǎn)單的特點(diǎn),。但其串聯(lián)諧振頻率測(cè)量范圍較小,測(cè)量精度較低,。因此,,研制寬范圍、高精度的石英晶體頻率測(cè)試系統(tǒng),,具有服務(wù)生產(chǎn)的實(shí)際意義,。

π網(wǎng)絡(luò)零相位法石英晶體測(cè)試系統(tǒng)所能測(cè)量的頻率范圍和精度直接依賴于π網(wǎng)絡(luò)的掃頻信號(hào)源,為了使石英晶體測(cè)試系統(tǒng)的測(cè)量范圍達(dá)到20 kHz~400 MHz,需要研究設(shè)計(jì)一個(gè)信號(hào)源,,該信號(hào)源的輸出頻率范圍為0~400 MHz,,并且輸出頻率精度高、穩(wěn)定度高,、頻率分辨率高,、頻率切換速度快。

1 π網(wǎng)絡(luò)零相位法高頻石英晶體測(cè)試系統(tǒng)設(shè)計(jì)

1.1 石英晶體電參數(shù)等效模型

石英晶體具有壓電效應(yīng),,當(dāng)外加交變電場(chǎng)的頻率等于其固有頻率時(shí),石英晶體將產(chǎn)生機(jī)械諧振,,該機(jī)械振動(dòng)通過壓電效應(yīng)與振蕩電路相耦合產(chǎn)生電諧振,,這種情況下石英晶體可以等效為圖1所示的RLC諧振電路。其中,,C0是靜電容,,L1為動(dòng)態(tài)電感,Rr是串聯(lián)諧振電阻,,C1為動(dòng)態(tài)電容,。

1.2 π網(wǎng)絡(luò)零相位法石英晶體頻率測(cè)試原理

IEC推薦的π網(wǎng)絡(luò)模型如圖2所示,π網(wǎng)絡(luò)由對(duì)稱的雙π型回路組成,,R1,,R2和R3構(gòu)成輸入衰減器,R4,,R5和R6構(gòu)成輸出衰減器,,它們的作用是使π網(wǎng)絡(luò)的阻抗與測(cè)量?jī)x表的阻抗相匹配,并衰減來自測(cè)量?jī)x器的反射信號(hào),。Y為被測(cè)石英晶體,。VA為π網(wǎng)絡(luò)輸入信號(hào),VB為π網(wǎng)絡(luò)輸出信號(hào),,實(shí)際測(cè)量對(duì),,不斷改變輸入信號(hào)的頻率,測(cè)量輸入信號(hào)和輸出信號(hào)的相位差,,當(dāng)石英晶體處在諧振狀態(tài)時(shí),,整個(gè)π網(wǎng)絡(luò)呈純電阻性,輸入信號(hào)和輸出信號(hào)之間相位差為零,。因此,,π網(wǎng)絡(luò)零相位法可通過檢測(cè)π網(wǎng)絡(luò)兩端信號(hào)的相位差是否為零來判斷待測(cè)石英晶體是否諧振,從而測(cè)出石英晶體的串聯(lián)諧振頻率,。當(dāng)π網(wǎng)絡(luò)兩端信號(hào)的相位差為零時(shí),,石英晶體處在諧振狀態(tài),石英晶體串聯(lián)諧振頻率等于π網(wǎng)絡(luò)輸入信號(hào)頻率。

1.3 測(cè)試系統(tǒng)設(shè)計(jì)

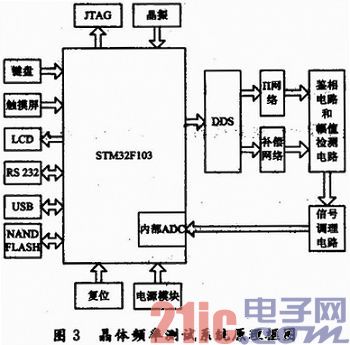

本系統(tǒng)基于霄網(wǎng)絡(luò)零相位法設(shè)計(jì)而成,,由DDS電路,、π網(wǎng)絡(luò)電路、鑒相電路,、模擬信號(hào)處理電路,、串口電路、LCD電路,、觸摸屏電路,、鍵盤電路、512 MB NANDFLASH存儲(chǔ)器電路等組成,。圖3是晶體頻率測(cè)試系統(tǒng)原理框圖,。

高頻石英晶體測(cè)試系統(tǒng)以一款A(yù)RM芯片STM32F103作為核心單元。STM32F103內(nèi)核為32 b的Cortex-M3 CFU,,最高可達(dá)72 MHz工作頻率,。STM 32F103通過內(nèi)置高速SPI總線與DDS芯片AD9912相連,控制AD9912輸出掃頻信號(hào),。

當(dāng)被測(cè)晶體放入π網(wǎng)絡(luò)電路后,,在不同的掃頻信號(hào)作用下,π網(wǎng)絡(luò)兩端輸入和輸出信號(hào)的相位差不同,。π網(wǎng)絡(luò)兩端的輸入信號(hào)和輸出信號(hào)分別送入鑒相電路,,在鑒相電路的輸出端得到與π網(wǎng)絡(luò)兩端輸入和輸出信號(hào)的相位差成正比的電壓信號(hào)。鑒相電路的輸出電壓信號(hào)和輸入信號(hào)相位差之間的關(guān)系如圖4所示,。

鑒相電路的輸出電壓信號(hào)經(jīng)過信號(hào)調(diào)理電路轉(zhuǎn)變?yōu)檫m合于進(jìn)行ADC采集的信號(hào),。信號(hào)通過STM32F103內(nèi)置的12位ADC通道采集到處理器內(nèi)部。測(cè)量過程時(shí),,DDS輸出信號(hào)的頻率由小變大,,π網(wǎng)絡(luò)兩端輸入信號(hào)和輸出信號(hào)的相位差絕對(duì)值由大變小并逐漸接近于零,之后又由小變大,。而ADC采集的結(jié)果則由小變大,,到達(dá)最大值后,又由大變小,。因此,,這個(gè)最大值1.8 V處對(duì)應(yīng)的DDS輸出信號(hào)頻率即為石英晶體的串聯(lián)諧振頻率。

2 DDS技術(shù)在測(cè)試系統(tǒng)中的應(yīng)用

2.1 DDS技術(shù)

DDS有2個(gè)突出的特點(diǎn),,一方面,,DDS工作在數(shù)字域,一旦更新頻率控制字,,輸出的頻率就相應(yīng)改變,,其跳頻速率高,;另一方面,由于頻率控制字的范圍寬,,頻率分辨率高,。與傳統(tǒng)的頻率合成器相比,DDS具有低成本,、低功耗,、高分辨率和頻率快速轉(zhuǎn)換等優(yōu)點(diǎn),廣泛應(yīng)用于電子儀器儀表領(lǐng)域,。

AD9912是ADI公司于2007年新推出的一款DDS芯片,,內(nèi)部時(shí)鐘速度可高達(dá)1 GSPS,并集成了14位數(shù)模轉(zhuǎn)換器,,因此可以直接輸出400 MHz信號(hào),。AD9912采用48位頻率控制字,輸出頻率分辨率小于4μHz,。AD9912兼容多種系統(tǒng)時(shí)鐘輸入方式,石英晶體,、晶體振蕩器和外部時(shí)鐘都可以作為其系統(tǒng)時(shí)鐘輸入,。由于具有片上系統(tǒng)時(shí)鐘鎖相環(huán)(PLL),允許系統(tǒng)時(shí)鐘輸入低至25 MHz,。

2.2 信號(hào)源硬件設(shè)計(jì)

筆者選擇ADI公司的AD9912作為信號(hào)源的核心,。STM32F103通過內(nèi)置高速SPI總線控制AD9912輸出0~400 MHz的掃頻信號(hào)。AD9912的工作原理如圖5所示,。

AD9912的外圍電路主要由5大模塊組成:電源,、時(shí)鐘源、SPI通信接口,、啟動(dòng)配置邏輯,、輸出信號(hào)處理電路。

AD9912的電源分為模擬3.3 V,、數(shù)字3.3 V,、模擬1.8 V和數(shù)字1.8 V四大類。模擬3.3 V和數(shù)字3.3 V經(jīng)過濾波器互相隔離,。模擬1.8 V和數(shù)字1.8 V經(jīng)過濾波器互相隔離,。AD9912的參考時(shí)鐘選用25 MHz的高性能恒溫石英晶體,AD9912內(nèi)部的PLL電路對(duì)該參考時(shí)鐘進(jìn)行40倍倍頻得到1 000 MHz時(shí)鐘信號(hào)作為AD9912的系統(tǒng)時(shí)鐘,。32管腳CLKMODESEL為時(shí)鐘模式選擇管腳,,如果使用石英晶體作為系統(tǒng)時(shí)鐘輸入,該管腳應(yīng)該接地,,如果使用振蕩器或者外部時(shí)鐘源作為系統(tǒng)時(shí)鐘輸入,,該管腳應(yīng)被上拉至1.8 V。由于選用的是石英晶體,該管腳接地,。

SPI通信接口硬件連接如圖6所示,。

啟動(dòng)配置邏輯包含S1,S2,,S3,,S4四個(gè)管腳。其中S4為邏輯0時(shí),,選擇時(shí)鐘模式:使用石英晶體作為系統(tǒng)時(shí)鐘輸入,,并且由AD9912內(nèi)部的PLL電路進(jìn)行倍頻得到時(shí)鐘信號(hào);S4為邏輯1時(shí),,選擇時(shí)鐘模式:由外部直接輸入時(shí)鐘信號(hào),。因此,把S4設(shè)置為邏輯0,。S1,、S2和S3的8種不同邏輯組合,用來選擇8組預(yù)置的16位頻率控制字,。允許在未配置I/O寄存器的情況下,,產(chǎn)生8種頻率不同的信號(hào)。由于本測(cè)試系統(tǒng)需要的是掃描信號(hào),,不需要某固定頻率的信號(hào),,因此,把S1,,S2和S3設(shè)置為邏輯0,,使DDS在啟動(dòng)時(shí)不輸出信號(hào)。

AD9912的輸出信號(hào)為差分信號(hào),,采用射頻變壓器將差分信號(hào)轉(zhuǎn)換為單端信號(hào),,并經(jīng)過低通濾波電路和功率放大電路后輸入至π網(wǎng)絡(luò)和補(bǔ)償網(wǎng)絡(luò)。AD9912輸出信號(hào)處理電路如圖7所示,。其中,,DAC_OUT和DAC_OUTB是AD9912輸出的差分信號(hào)。

2.3 信號(hào)源軟件設(shè)計(jì)

處理器STM32F103控制AD9912輸出頻率信號(hào),,主要是通過SPI向AD9912的寄存器中寫入對(duì)應(yīng)的值,。

由于選用25 MHz的高性能恒溫石英晶體作為參考時(shí)鐘,需要使能系統(tǒng)時(shí)鐘PLL,,應(yīng)將寄存器0x0010的第4位設(shè)置為邏輯0,。

寄存器0x01A0~0x01AD為輸出信號(hào)控制字,其中0x01A0~0x01A5為保留寄存器,,0x01A6~0x01AB為頻率控制字,,0x01AC~0x01AD為相位控制字,。

輸出信號(hào)頻率與頻率控制字關(guān)系為:

fDDS=(FTW/248)fs (1)

式中:fDDS為AD9912輸出信號(hào)頻率;FTW為頻率控制字,;fs為AD9912的系統(tǒng)時(shí)鐘頻率,。

由式(1)得到:

FTW=round[248(fDDS/fs)] (2)

例如,當(dāng)fs=1 GHz,,fDDS=19.44 MHz,,則FTW=5 471 873 547 255(即0x04FA05143BF7)。

輸出信號(hào)相位與相位控制字關(guān)系為:

△φ=2П(△phase/214) (3)

式中:△φ為AD9912輸出信號(hào)相位,;△phase為相位控制字,。由于信號(hào)源需要應(yīng)用于高頻石英晶體測(cè)試系統(tǒng)中,所以,,不能只輸出一個(gè)固定頻率的信號(hào),,必須輸出掃頻信號(hào)。測(cè)試之前,,通過健盤或觸摸屏輸入待測(cè)晶體的標(biāo)稱頻率,、起始掃描頻率、終止掃描頻率,、掃描步進(jìn)頻率,,處理器根據(jù)式(2)算法,由掃描步進(jìn)頻率計(jì)算出掃描步進(jìn)控制字(以下稱為FTWstep),。圖8所示為信號(hào)源應(yīng)用于高頻石英晶體測(cè)試系統(tǒng)的軟件流程圖。

3 實(shí)驗(yàn)結(jié)果

信號(hào)源的精度和穩(wěn)定度直接影響到測(cè)試系統(tǒng)測(cè)量石英晶體頻率的精度和穩(wěn)定度,。因此,,使用CNT-90型頻率計(jì)測(cè)量本系統(tǒng)信號(hào)源輸出的信號(hào)頻率。實(shí)驗(yàn)結(jié)果表明,,信號(hào)源輸出信號(hào)頻率的精度高于±0.1 ppm,,頻率的穩(wěn)定度高于±0.1ppm,實(shí)驗(yàn)數(shù)據(jù)如表1所示,。

表中,,f為設(shè)定的頻率值;f為實(shí)際測(cè)量的頻率平均值,;△f/f為相對(duì)偏差,。

4 結(jié)語

本設(shè)計(jì)成功地把DDS技術(shù)應(yīng)用到高頻石英晶體測(cè)試系統(tǒng)中。實(shí)現(xiàn)了基于DDS技術(shù)的寬帶信號(hào)源,。該信號(hào)源具有輸出頻率范圍寬,、精度高、穩(wěn)定度高,、頻率分辨率高,,頻率切換速度快的特點(diǎn),,從而滿足了高頻石英晶體測(cè)試系統(tǒng)對(duì)信號(hào)源的要求。