0引言

電容式傳感器是將被測(cè)的非電量變化轉(zhuǎn)換為電容量變化的一類傳感器,由于它具有靈敏度高、功耗低、溫度漂移小等優(yōu)點(diǎn),因此廣泛應(yīng)用在壓力、濕度、溫度和加速度等測(cè)量中。MEMS(微電子機(jī)械系統(tǒng))傳感器體積小的特點(diǎn)決定了敏感電容器的電容值不可能大,一般為pF量級(jí),而由這些物理量引起的微電容的變化更加微小,一般為fF甚至aF量級(jí)。如此小的變化量對(duì)檢測(cè)電路的設(shè)計(jì)是一個(gè)挑戰(zhàn)。傳統(tǒng)的用分立元件搭制檢測(cè)電路的方法將無(wú)法適應(yīng)傳感器電容不斷減小的趨勢(shì),因此設(shè)計(jì)匹配的接口集成電路是十分必要的。常用的低值電容測(cè)量電路都是把電容的變化轉(zhuǎn)變?yōu)殡妷夯蝾l率。目前大多數(shù)國(guó)外MEMS傳感器廠家采用開(kāi)關(guān)電容電路作為電容信號(hào)的接口。這一電路的特點(diǎn)是精度高、可實(shí)現(xiàn)與傳感器的高度集成,但電路結(jié)構(gòu)相對(duì)復(fù)雜,對(duì)于工藝精度要求較高。其次是采用振蕩法將敏感電容變化轉(zhuǎn)換為頻率或周期,電路簡(jiǎn)單,易于實(shí)現(xiàn),輸出的頻率信號(hào)具有準(zhǔn)數(shù)字輸出的特點(diǎn),便于測(cè)量。本文介紹的電路正是基于這種原理。

1微電容檢測(cè)

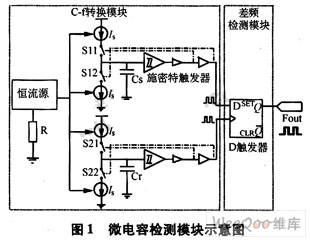

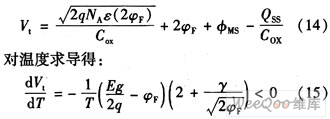

已推導(dǎo)的基于施密特觸發(fā)器檢測(cè)電容的方法不同,為了避免輸出頻率受電源電壓、溫度變化和工藝波動(dòng)的影響,本實(shí)驗(yàn)室開(kāi)發(fā)的微電容式傳感器檢測(cè)電路在張弛振蕩器的基礎(chǔ)上設(shè)計(jì)了一種差頻電路,其模塊示意圖如圖1所示。本文對(duì)敏感電容檢測(cè)電路的流水芯片進(jìn)行了測(cè)試和分析,并搭建了圖1所示結(jié)構(gòu)的整個(gè)電路,仿真并測(cè)試了該電路的溫漂特性。

2接口電路的分析與改進(jìn)

2.1振蕩器電路

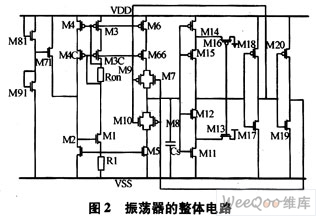

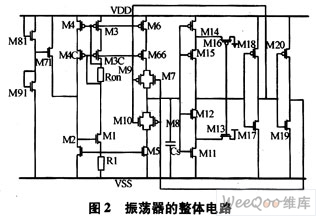

圖2是本實(shí)驗(yàn)室已經(jīng)流片的敏感電容振蕩電路。該電路由開(kāi)啟電路、恒流源、CMOS開(kāi)關(guān)、施密特觸發(fā)器以及反相器組成。

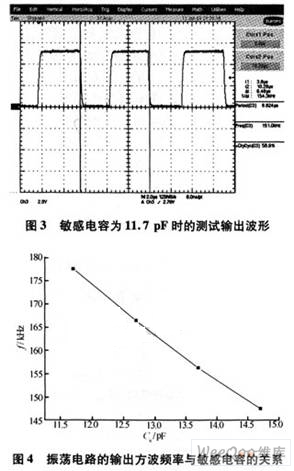

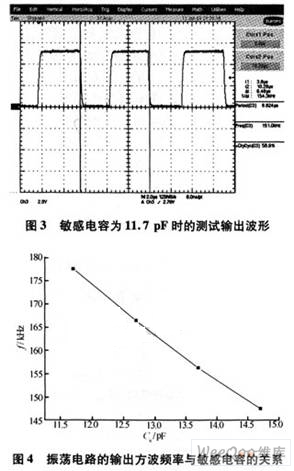

由圖3和圖4可見(jiàn),該電路實(shí)現(xiàn)了輸出波形的頻率與敏感電容的變化成反比的關(guān)系,從振蕩器的輸出端讀取頻率完全可以檢測(cè)到傳感器電容的變化。但是存在兩個(gè)問(wèn)題:一是輸出頻率過(guò)大,不方便單片機(jī)讀數(shù);二是輸出頻率仍然受電源電壓、溫度變化和工藝波動(dòng)的影響。

2.2差頻電路

在檢測(cè)電路中利用D觸發(fā)器實(shí)現(xiàn)差頻功能。D觸發(fā)器為下降沿觸發(fā)的CMOS主從觸發(fā)器。敏感電容轉(zhuǎn)換的波形從D端輸入,參考電容轉(zhuǎn)換的波形從CK端輸入,輸出為兩個(gè)波形的頻率之差。這樣可以提高電路的靈敏度,改善單邊電路的溫度、電源電壓抑制等對(duì)電路性能的影響。

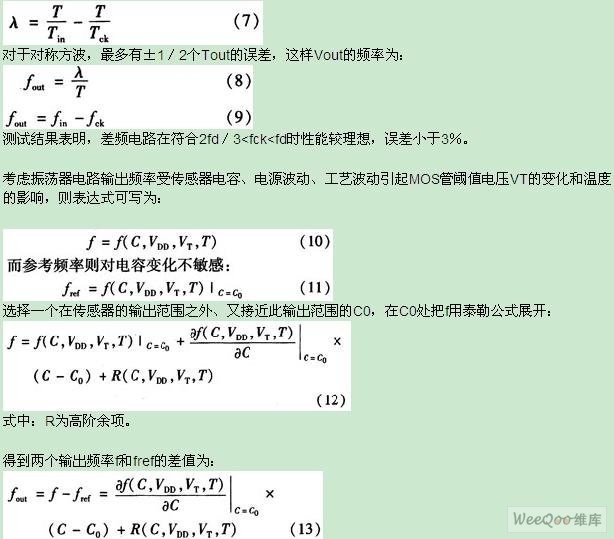

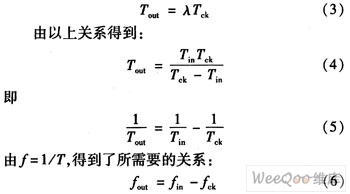

下面分析D觸發(fā)器的差頻原理。由前面設(shè)定的條件,信號(hào)頻率大于時(shí)鐘頻率,定義輸入信號(hào)的周期與時(shí)鐘信號(hào)的周期之差為△T,即

首先假設(shè)存在一個(gè)整數(shù),使得各方波之間滿足以下關(guān)系:

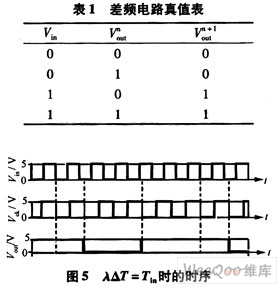

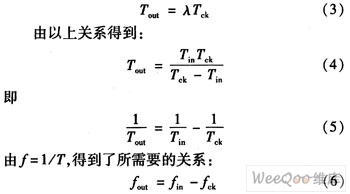

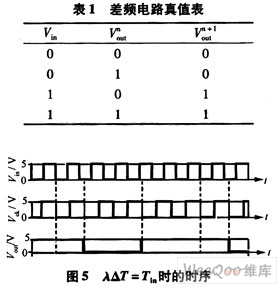

在t0刻,Vin和Vck同為下降沿,Vout應(yīng)跟隨Vck的原狀態(tài)輸出高電平。那么,由△T=Tin-Tck,在Vck第2個(gè)下降沿到來(lái)時(shí),比Vin的第2個(gè)下降沿要遲一個(gè)△T,此時(shí)Vin為高電平。由下降沿觸發(fā)的D觸發(fā)器的真值表(見(jiàn)表1)可知,此時(shí)Vout必輸出低電平,見(jiàn)圖5。

經(jīng)n個(gè)周期,使得(n-1)△T≤Tin/2,n△T>Tin/2時(shí),Vck下降時(shí)Vin為高電平,輸出跳變?yōu)楦唠娖健=?jīng)過(guò)λTck的時(shí)間,Vin比Vck多走了一個(gè)周期,再次同時(shí)達(dá)到下降沿,但Vout仍為輸出高電平。(λ+1)Tck時(shí),Vck下降沿到來(lái),此時(shí)Vin為高電平。Vout再次跳變到低電平。取兩次Vout下降沿的距離作為Vout的周期,得

對(duì)于t0時(shí)刻Vin的上升沿與Vck下降沿重合的情況,分析與上面完全類似,可得到相同的結(jié)果。

下面考慮更一般的情況。當(dāng)Tin不是△T的整數(shù)倍時(shí),仍假設(shè)t0時(shí)刻輸入不同頻率,不同占空比時(shí)Vout和Vck同為下降沿,分析過(guò)程同上,不同的是,在Vout經(jīng)過(guò)λTck的時(shí)間后,由于Tin不是△T的整數(shù)倍,Vin和Vck無(wú)法再次同時(shí)達(dá)到下降沿,對(duì)于下一周期的分析將無(wú)法套用以上的過(guò)程。

因此考慮一個(gè)相對(duì)長(zhǎng)的時(shí)間內(nèi),t0到t0+T之間各信號(hào)頻率的關(guān)系。Vin走了T/Tin個(gè)下降沿,T/Tin或T/Tin+1個(gè)上升沿,Vck走了T/Tck個(gè)下降沿。Vin比Vck多走了T/Tin-T/Tck個(gè)周期。按以分析方法可得出,Vout會(huì)有T/Tin-T/Tck個(gè)下降沿,可以認(rèn)為Vout周期為:

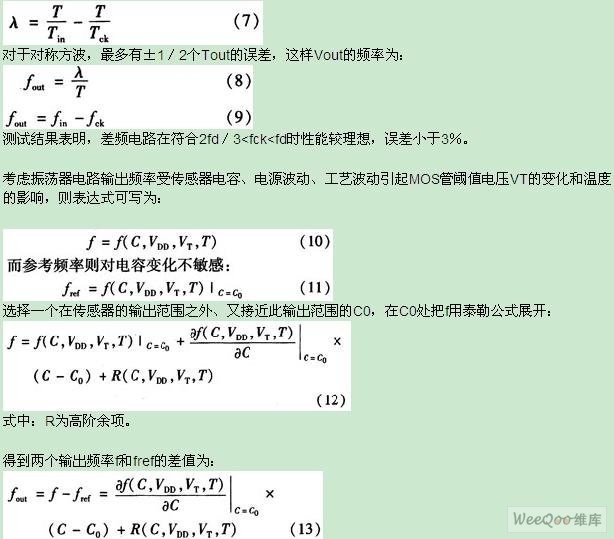

由式(13)可以看出,通過(guò)兩個(gè)相同電路的頻率求差,電源、閾值電壓和溫度對(duì)頻率的影響中各自最主要的一項(xiàng)被消去,大大降低了對(duì)電容-頻率特性的影響。

2.3接口電路的溫漂特性

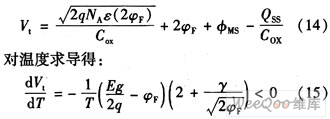

根據(jù)半導(dǎo)體理論,MOS管閾值電壓可表示為:

分別將-40℃~60℃代入式(14)、式(15),最終得到各溫度下對(duì)應(yīng)的閾值電壓值。從而知道閾值電壓的絕對(duì)值隨溫度的升高而減小,又已知輸出頻率受工藝波動(dòng)成正比關(guān)系,由此推斷輸出頻率隨溫度升高而降低。這將在后面的仿真測(cè)試中得到進(jìn)一步驗(yàn)證。

3設(shè)計(jì)和模擬結(jié)果

作為傳感器的接口電路,希望在環(huán)境溫度變化的情況下可以得到穩(wěn)定的輸出頻率。在溫度變化范圍在-40℃~60℃、參考電容為14.5 pF的情況下,對(duì)圖1檢測(cè)電路分別進(jìn)行了仿真和測(cè)試。觀察圖6、圖7可以發(fā)現(xiàn):輸出頻率與溫度近似成反比關(guān)系,進(jìn)一步驗(yàn)證了上述對(duì)溫漂特性分析結(jié)論的正確性;差頻后的溫度系數(shù)大約為14 Hz/℃,對(duì)于靈敏度為46 fF/hPa的氣壓傳感器,相對(duì)于10.04:Hz/fF的靈敏度溫度的影響是可以忽略的;差頻前的測(cè)試數(shù)據(jù)曲線與仿真的數(shù)據(jù)曲線有一個(gè)距離,這是與電流源在實(shí)際工作中的電流值偏小有關(guān),但并不影響整體電路輸出結(jié)果的檢測(cè);測(cè)試曲線的斜率絕對(duì)值大于仿真曲線斜率絕對(duì)值,這是由于仿真中只考慮了溫度變化引起的閾值電壓變化,而實(shí)際測(cè)試中溫度變化引起的工藝參數(shù)和器件參數(shù)的變化以及搭建電路受到的測(cè)試環(huán)境的各種干擾都將影響測(cè)試的數(shù)據(jù)。這可以在后續(xù)工作中通過(guò)考慮封裝提高可靠性。結(jié)果表明,差頻結(jié)構(gòu)可濾去絕大部分影響,以至將溫度的影響完全抑制在精度的允許范圍內(nèi)。

本電路的目的是為本實(shí)驗(yàn)室新一代傳感器提供一個(gè)讀出接口。通過(guò)前期對(duì)傳感器的準(zhǔn)確測(cè)試,傳感器的基本電容約為10 pF,變化從7 pF到14 pF。該電路的參考電容值為14.5 pF,為了使傳感器一級(jí)輸出頻率大于參考頻率并滿足2fd/3

4 結(jié)束語(yǔ)

通過(guò)SPICE仿真,可以看出,改進(jìn)后的電路結(jié)構(gòu)滿足了提出的各項(xiàng)目標(biāo)。由于該電路是用頻率的變化反映敏感電容的變化,具有準(zhǔn)數(shù)字輸出的特點(diǎn),只要用一個(gè)計(jì)數(shù)功能的單片機(jī),即可實(shí)現(xiàn)信號(hào)的采集。

工藝的波動(dòng)會(huì)對(duì)電路的電容-頻率轉(zhuǎn)換特性產(chǎn)生影響,從而引起流片結(jié)果個(gè)體間的差異。因此,必須對(duì)每個(gè)傳感器分別定標(biāo),這樣,工藝的波動(dòng)才不會(huì)使單個(gè)傳感器產(chǎn)生偏差。

![]()

![]()