中心機(jī)和前端受控模塊之間相距較遠(yuǎn),而且需要傳輸較大的數(shù)據(jù)量。一般的485串行接口已無法滿足要求,而光纖具有傳輸速度快、傳輸距離遠(yuǎn)、抗干擾能力強(qiáng)和重量輕等優(yōu)點(diǎn),在高速通信中得到了廣泛應(yīng)用。因此這里選擇光纖作為通信介質(zhì)。通信接口模塊連接的受控模塊眾多,各模塊具有不同的通信協(xié)議和接口形式,并且部分?jǐn)?shù)據(jù)對通信延時的要求很高,因此適宜采用靈活性強(qiáng)且可以并行發(fā)送數(shù)據(jù)的FPGA來實(shí)現(xiàn)該模塊功能。

1 通信協(xié)議設(shè)計(jì)

1.1 傳輸數(shù)據(jù)類型分析

通信接口模塊需要處理的數(shù)據(jù)分為3種:中心機(jī)發(fā)給前端受控模塊的控制命令(上行數(shù)據(jù));前端受控模塊發(fā)送給中心機(jī)的狀態(tài)信息(下行數(shù)據(jù));中心機(jī)控制通信接口模塊實(shí)現(xiàn)信息轉(zhuǎn)發(fā)控制的命令。通信接口模塊對前兩種數(shù)據(jù)分開處理,兩者之間互不干擾。后一種數(shù)據(jù)則是通過設(shè)置通信接口模塊內(nèi)的參數(shù)實(shí)現(xiàn)。

控制命令分為兩種,即周期性命令和非周期性命令。周期性命令在周期性的定時信號的控制下發(fā)送到各個設(shè)備,如周期性命令由于某些原因在下一周期到來之前沒有發(fā)送,則舊命令就會被清除掉。非周期性命令任何時間都可以發(fā)送,與定時信號無關(guān)。非周期命令發(fā)送次數(shù)較少,但較重要,一般為初始化命令或重要參數(shù)的設(shè)置命令,不允許有丟失。

狀態(tài)信息也有周期性和非周期性之分,但狀態(tài)信息所要傳輸?shù)臄?shù)據(jù)較少、周期較長,相對于高速的光纖接口則可視為非周期數(shù)據(jù),狀態(tài)信息可以用統(tǒng)一的方式處理,并且各模塊使用固定的優(yōu)先級順序傳輸。

1.2 前端受控模塊接口協(xié)議

根據(jù)各模塊對傳輸數(shù)據(jù)量及對時間準(zhǔn)確度的要求,使用了3種接口協(xié)議:三線同步串行接口、通用異步串行接口和邏輯電平接口。

(1)三線同步串行接口。需要高速傳輸和對實(shí)時性要求較高的模塊采用三線同步串行接口。三線同步串行接口包含數(shù)據(jù)、時鐘、幀結(jié)束等3個信號線。相對于通用異步串行接口具有傳輸速度快的優(yōu)點(diǎn),相對于使用隨路時鐘方式的串行接口具有實(shí)現(xiàn)簡單的優(yōu)點(diǎn)。根據(jù)不同設(shè)備的控制命令字或狀態(tài)信息數(shù)據(jù)長度不同,設(shè)置同步串行接口的數(shù)據(jù)發(fā)送/接收長度和有效時鐘邊沿個數(shù)。為保證在較高速度下的通信傳輸質(zhì)量,三線制同步串行接口采用LVDS電平。LVDS電路是一種具有低電平電壓擺幅差分信號傳輸結(jié)構(gòu)的電路,具有工作時驅(qū)動電流恒定、低功耗、低EMI、抗噪聲干擾等特點(diǎn),工作頻率最高可達(dá)幾GHz。

2)通用異步串行接口。對于數(shù)據(jù)率和實(shí)時性要求不高的模塊,采用通用異步串行接口。恰好大部分慢速傳輸數(shù)據(jù)的模塊都用單片機(jī)實(shí)現(xiàn)控制,而單片機(jī)都有通用異步串行接口。異步串行接口較同步串行接口使用較少的連接線。只需一對雙絞線就可以完成傳輸,并且可以進(jìn)行長距離傳輸。同樣為保證信號傳輸質(zhì)量,通信電平采用RS485。RS485采用差分傳輸,具有抗干擾能力強(qiáng)、傳輸距離遠(yuǎn)的優(yōu)點(diǎn)。

(3)邏輯電平接口。部分前端模塊沒有專用的通信接口,其控制接口和狀態(tài)信息是按照邏輯電平信號實(shí)現(xiàn)的。對于控制命令,由于前端受控模塊的控制接口沒有鎖存功能,需要在通信接口模塊上對輸出信號進(jìn)行寄存,直到下次命令發(fā)生更改。對于邏輯電平信號輸入的狀態(tài)信息,由于信號電平變化較少,僅在檢測到有效電平變動時通信接口模塊才回傳狀態(tài)信息。

1.3 光纖通信協(xié)議

光纖通信協(xié)議分為物理層、數(shù)據(jù)鏈路層和應(yīng)用層。物理層定義了傳輸介質(zhì)和信號傳輸方式,物理層處理包括光電轉(zhuǎn)換、串行解串和8B/10B編解碼等。數(shù)據(jù)鏈路層定義了幀格式和數(shù)據(jù)傳輸規(guī)則,鏈路層處理包括成幀和解幀。光纖通信協(xié)議結(jié)構(gòu)如圖1所示。

2012/08/31/e7ecca93-0309-4867-be8f-e93c949a8fb8.jpg" />

2012/08/31/e7ecca93-0309-4867-be8f-e93c949a8fb8.jpg" />協(xié)議使用8B/10B編碼保證數(shù)據(jù)通道的直流平衡,完成時鐘的恢復(fù)。同時利用8B/10B編碼的控制字符作為數(shù)據(jù)幀傳輸?shù)钠鹗肌⒔Y(jié)束標(biāo)識,并作為傳輸信道的同步控制。在每一數(shù)據(jù)幀的起始位置添加幀起始控制字符,在數(shù)據(jù)幀的結(jié)束位置添加幀結(jié)束控制字符,在數(shù)據(jù)傳輸過程中有中斷或在無數(shù)據(jù)傳輸?shù)目臻e時段填充同步控制字符。

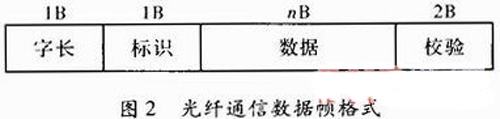

控制命令和狀態(tài)數(shù)據(jù)都以數(shù)據(jù)幀的方式在光纖上傳輸。數(shù)據(jù)幀格式如圖2所示。標(biāo)識字說明數(shù)據(jù)幀的性質(zhì)和傳輸?shù)降脑O(shè)備,不同的應(yīng)用有不同的標(biāo)識,且每個標(biāo)識有唯一對應(yīng)的設(shè)備,一個設(shè)備可能有多個標(biāo)識字。字長為從標(biāo)識到校驗(yàn)的長度。數(shù)據(jù)為命令或狀態(tài)信息。校驗(yàn)字為從字長到數(shù)據(jù)的所有字節(jié)的循環(huán)冗余校驗(yàn)碼(CRC)。

2 通信接口模塊實(shí)現(xiàn)

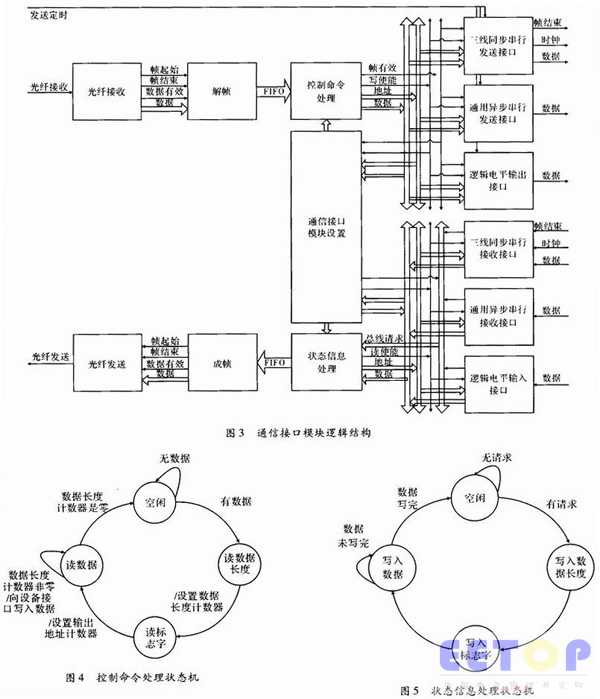

通信接口模塊以FPGA為控制核心,外圍添加電平轉(zhuǎn)換芯片實(shí)現(xiàn)。通信接口模塊對上行控制命令和下行狀態(tài)信息進(jìn)行獨(dú)立處理。在FPGA內(nèi)實(shí)現(xiàn)的邏輯框圖如圖3所示。

光纖接收和光纖發(fā)送模塊實(shí)現(xiàn)光纖通信協(xié)議的物理層處理。成幀和解幀模塊實(shí)現(xiàn)光纖通信協(xié)議的鏈路層處理。控制命令處理和狀態(tài)數(shù)據(jù)處理實(shí)現(xiàn)用戶數(shù)據(jù)處理。三線同步串行接口、通用異步串行接口和邏輯電平接口實(shí)現(xiàn)針對各個前端受控模塊的數(shù)據(jù)傳輸。

2.1 光纖接口

按照光纖通信協(xié)議,光纖接口包括物理層和鏈路層處理,即圖3中的光纖發(fā)送/接收、成幀/解幀邏輯模塊,發(fā)送和接收是相反方向的處理。光纖接收/發(fā)送邏輯模塊實(shí)現(xiàn)串行解串編解碼和8B/10B編解碼。串行器將并行數(shù)據(jù)變?yōu)榇袛?shù)據(jù)發(fā)送至光纖接口;解串器將從光纖接口接收到的串行數(shù)據(jù)變?yōu)椴⑿袛?shù)據(jù)。同時通過8B/10B編碼將發(fā)送時鐘編碼到數(shù)據(jù)中一同發(fā)送,解串器則從數(shù)據(jù)流中恢復(fù)時鐘。串行器采用

SN65LV1023A器件,解串器采用SN65LV1224B器件。8B/10B編解碼則在FPGA中實(shí)現(xiàn)。成幀/解幀模塊實(shí)現(xiàn)數(shù)據(jù)長度檢驗(yàn)、數(shù)據(jù)校驗(yàn)、添加幀頭和幀尾。

2.2 控制命令處理邏輯

控制命令處理邏輯首先檢測FIFO緩沖器是否有數(shù)據(jù),如有數(shù)據(jù)則開啟一次控制命令處理。數(shù)據(jù)處理時,根據(jù)標(biāo)志字將數(shù)據(jù)寫入相應(yīng)的設(shè)備接口,一幀數(shù)據(jù)處理完成后,通過設(shè)置幀有效信號,啟動接口模塊發(fā)送。控制狀態(tài)機(jī)如圖4所示

2.3 狀態(tài)數(shù)據(jù)處理邏輯

由于各個前端受控模塊下行數(shù)據(jù)量較少、數(shù)據(jù)間時間間隔較大,而FPGA內(nèi)部數(shù)據(jù)處理速度遠(yuǎn)快于外部接口,因此不存在某一受控模塊始終占據(jù)總線的情況。這樣不需要考慮按照請求到來時間順序進(jìn)行處理請求,而是狀態(tài)數(shù)據(jù)處理邏輯接到受控模塊接口的總線請求后,按照固定的優(yōu)先級處理。

2.4 三線制同步串行口

三線制同步串行接口的邏輯結(jié)構(gòu)如圖6所示。三線制同步串行口接收模塊可分為數(shù)據(jù)接收和數(shù)據(jù)接收緩存兩部分。數(shù)據(jù)接收部分由移位寄存器組成。移位寄存器受接收的時鐘信號控制,實(shí)現(xiàn)串并轉(zhuǎn)換,數(shù)據(jù)接收完成后,直接輸出到數(shù)據(jù)接收緩存。數(shù)據(jù)接收緩存設(shè)置2級異步FIFO,實(shí)現(xiàn)跨時鐘域變換。當(dāng)緩存中有數(shù)據(jù)時,向狀態(tài)信息處理模塊發(fā)出請求,等待讀出數(shù)據(jù)。

三線制同步串行口發(fā)送模塊同樣可分為兩部分:數(shù)據(jù)發(fā)送緩存和數(shù)據(jù)發(fā)送。數(shù)據(jù)發(fā)送部分主要是由移位寄存器、移位計(jì)數(shù)器組成。根據(jù)不同的數(shù)據(jù)長度設(shè)置不同長度的移位寄存器,實(shí)現(xiàn)數(shù)據(jù)的并行輸入和串行移出。移位計(jì)數(shù)器控制數(shù)據(jù)移出的個數(shù),同時控制時鐘信號和幀同步信號的產(chǎn)生。數(shù)據(jù)緩存部分根據(jù)傳輸數(shù)據(jù)的不同而不同。對于周期性控制命令設(shè)置一級緩存,當(dāng)新數(shù)據(jù)來時緩存被新數(shù)據(jù)覆蓋。對于非周期控制命令設(shè)置4級FIFO,由于非周期控制命令較少,4級緩存已經(jīng)足夠。數(shù)據(jù)緩存部分優(yōu)先發(fā)送非周期控制命令

2.5 通用異步串口

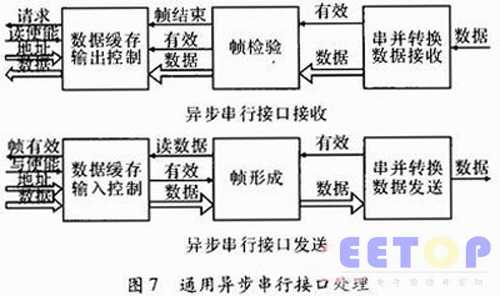

通用異步串行接口的邏輯結(jié)構(gòu)如圖7所示。通用異步串行接口的接收模塊可分為數(shù)據(jù)接收、幀檢驗(yàn)和數(shù)據(jù)緩存3部分。數(shù)據(jù)接收部分包括移位寄存器和接收控制邏輯。按照通用異步串行接口的時序,接收控制邏輯將移動移位寄存器,實(shí)現(xiàn)字節(jié)數(shù)據(jù)的接收和串并轉(zhuǎn)換。幀檢驗(yàn)?zāi)K按照特定前端受控模塊的通信數(shù)據(jù)幀格式對數(shù)據(jù)進(jìn)行檢驗(yàn),對檢驗(yàn)成功的數(shù)據(jù)寫入到數(shù)據(jù)緩沖區(qū)中。數(shù)據(jù)緩存中存儲數(shù)據(jù)后向狀態(tài)信息處理模塊發(fā)出請求,等待數(shù)據(jù)讀出。

通用異步串口的發(fā)送模塊同樣分為3部分:數(shù)據(jù)緩存、幀形成、數(shù)據(jù)發(fā)送。數(shù)據(jù)緩存接收控制命令處理模塊的數(shù)據(jù)并緩存。由于通用異步串口發(fā)送的命令都是非周期命令,使用128 Byte的FIFO作為數(shù)據(jù)緩存。在幀形成模塊中為數(shù)據(jù)添加校驗(yàn)、幀頭和幀尾。數(shù)據(jù)發(fā)送模塊針對字節(jié)數(shù)據(jù)按照通用異步通信的時序要求,將數(shù)據(jù)并串轉(zhuǎn)換發(fā)送出去。

3 仿真結(jié)果

FPGA選用Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx" title="Xilinx">Xilinx公司XC3S500E器件,該器件具有足夠的差分接口、邏輯和存儲器資源,能滿足該設(shè)計(jì)的要求。首先在ISE中利用Verilog HDL語言編寫邏輯代碼并用ISim對各個模塊進(jìn)行了詳細(xì)的功能仿真。光纖通信接口的仿真結(jié)果如圖8所示。該仿真利用光纖收發(fā)模塊進(jìn)行自環(huán),檢驗(yàn)?zāi)K輸入輸出的正確性。從光纖接口接收到相應(yīng)控制命令后三線同步串行接口,通用異步串行接口的數(shù)據(jù)輸出仿真結(jié)果如圖9和圖10所示。仿真表明,程序輸出數(shù)據(jù)發(fā)送正確且數(shù)據(jù)處理時延很小。

4 結(jié)束語

文中以FPGA為控制核心,實(shí)現(xiàn)了中心機(jī)控制多個遠(yuǎn)程受控模塊的通信接口模塊。該設(shè)計(jì)具有電路簡單、協(xié)議設(shè)計(jì)靈活,邏輯結(jié)構(gòu)擴(kuò)展性強(qiáng)等優(yōu)點(diǎn)。仿真表明,該設(shè)計(jì)能夠滿足通信數(shù)據(jù)傳輸?shù)墓δ芤螅壳耙褢?yīng)用到具體設(shè)備中。