A 時(shí)序約束的概念和基本策略

時(shí)序約束主要包括周期約束(FFS到FFS,即觸發(fā)器到觸發(fā)器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態(tài)路徑約束(IPAD到 OPAD)等3種。通過附加約束條件可以使綜合布線工具調(diào)整映射和布局布線過程,使設(shè)計(jì)達(dá)到時(shí)序要求。例如用OFFSET_IN_BEFORE約束可以告 訴綜合布線工具輸入信號在時(shí)鐘之前什么時(shí)候準(zhǔn)備好,綜合布線工具就可以根據(jù)這個(gè)約束調(diào)整與IPAD相連的Logic Circuitry的綜合實(shí)現(xiàn)過程,使結(jié)果滿足FFS的建立時(shí)間要求。

附加時(shí)序約束的一般策略是先附加全局約束,然后對快速和慢速例外路徑附加專門約束。附加全局約束時(shí),首先定義設(shè)計(jì)的所有時(shí)鐘,對各時(shí)鐘域內(nèi)的同步元 件進(jìn)行分組,對分組附加周期約束,然后對FPGA/CPLD輸入輸出PAD附加偏移約束、對全組合邏輯的PAD TO PAD路徑附加約束。附加專門約束時(shí),首先約束分組之間的路徑,然后約束快、慢速例外路徑和多周期路徑,以及其他特殊路徑。

B 附加約束的基本作用

1、提高設(shè)計(jì)的工作頻率

對很多數(shù)字電路設(shè)計(jì)來說,提高工作頻率非常重要,因?yàn)楦吖ぷ黝l率意味著高處理能力。通過附加約束可以控制邏輯的綜合、映射、布局和布線,以減小邏輯和布線延時(shí),從而提高工作頻率。

2、獲得正確的時(shí)序分析報(bào)告

幾乎所有的FPGA設(shè)計(jì)平臺都包含靜態(tài)時(shí)序分析工具,利用這類工具可以獲得映射或布局布線后的時(shí)序分析報(bào)告,從而對設(shè)計(jì)的性能做出評估。靜態(tài)時(shí)序分 析工具以約束作為判斷時(shí)序是否滿足設(shè)計(jì)要求的標(biāo)準(zhǔn),因此要求設(shè)計(jì)者正確輸入約束,以便靜態(tài)時(shí)序分析工具輸出正確的時(shí)序分析報(bào)告。

3、指定FPGA/CPLD引腳位置與電氣標(biāo)準(zhǔn)

FPGA/CPLD的可編程特性使電路板設(shè)計(jì)加工和FPGA/CPLD設(shè)計(jì)可以同時(shí)進(jìn)行,而不必等FPGA/CPLD引腳位置完全確定,從而節(jié)省了 系統(tǒng)開發(fā)時(shí)間。這樣,電路板加工完成后,設(shè)計(jì)者要根據(jù)電路板的走線對FPGA/CPLD加上引腳位置約束,使FPGA/CPLD與電路板正確連接。另外通 過約束還可以指定IO引腳所支持的接口標(biāo)準(zhǔn)和其他電氣特性。為了滿足日新月異的通信發(fā)展,Xilinx新型FPGA/CPLD可以通過IO引腳約束設(shè)置支 持諸如AGP、BLVDS、CTT、GTL、GTLP、HSTL、LDT、LVCMOS、LVDCI、LVDS、LVPECL、LVDSEXT、 LVTTL、PCI、PCIX、SSTL、ULVDS等豐富的IO接口標(biāo)準(zhǔn)。另外通過區(qū)域約束還能在FPGA上規(guī)劃各個(gè)模塊的實(shí)現(xiàn)區(qū)域,通過物理布局布線 約束,完成模塊化設(shè)計(jì)等。

C 周期(PERIOD)的含義

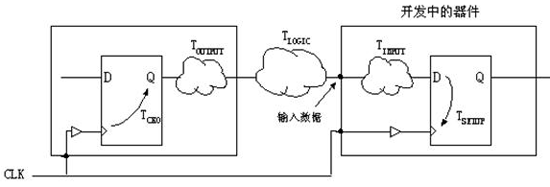

周期的含義是時(shí)序中最簡單也是最重要的含義,其它很多時(shí)序概念會因?yàn)檐浖滩煌杂胁町悾芷诘母拍畲_是最通用的,周期的概念是 FPGA/ASIC時(shí)序定義的基礎(chǔ)概念。后面要講到的其它時(shí)序約束都是建立在周期約束的基礎(chǔ)上的,很多其它時(shí)序公式,可以用周期公式推導(dǎo)。周期約束是一個(gè) 基本時(shí)序和綜合約束,它附加在時(shí)鐘網(wǎng)線上,時(shí)序分析工具根據(jù)PERIOD約束檢查時(shí)鐘域內(nèi)所有同步元件的時(shí)序是否滿足要求。PERIOD約束會自動(dòng)處理寄 存器時(shí)鐘端的反相問題,如果相鄰?fù)皆r(shí)鐘相位相反,那么它們之間的延遲將被默認(rèn)限制為PERIOD約束值的一半。如下圖所示,

時(shí)鐘的最小周期為:

TCLK = TCKO +TLOGIC +TNET +TSETUP -TCLK_SKEW

TCLK_SKEW =TCD2 -TCD1

其中TCKO為時(shí)鐘輸出時(shí)間,TLOGIC為同步元件之間的組合邏輯延遲,TNET為網(wǎng)線延遲,TSETUP為同步元件的建立時(shí)間,TCLK_SKEW為時(shí)鐘信號TCD2和TCD1延遲的差別。

D 數(shù)據(jù)和時(shí)鐘之間的約束

為了確保芯片數(shù)據(jù)采樣可靠和下級芯片之間正確地交換數(shù)據(jù),需要約束外部時(shí)鐘和數(shù)據(jù)輸入輸出引腳之間的時(shí)序關(guān)系(或者內(nèi)部時(shí)鐘和外部輸入/輸出數(shù)據(jù)之 間的關(guān)系,這僅僅是從采用了不同的參照系罷了)。約束的內(nèi)容為告訴綜合器、布線器輸入數(shù)據(jù)到達(dá)的時(shí)刻,或者輸出數(shù)據(jù)穩(wěn)定的時(shí)刻,從而保證與下一級電路的時(shí) 序關(guān)系。

這種時(shí)序約束在Xilinx中用Setup to Clock(edge),Clock(edge) to hold等表示。在Altera里常用tsu (Input Setup Times)、th (Input Hold Times)、tco (Clock to Out Delays)來表示。很多其它時(shí)序工具直接用setup和hold表示。其實(shí)他們所要描述的是同一個(gè)問題,僅僅是時(shí)間節(jié)點(diǎn)的定義上略有不同。下面依次介 紹。

E 關(guān)于輸入到達(dá)時(shí)間

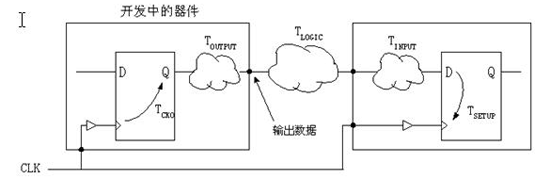

Xilinx的"輸入到達(dá)時(shí)間的計(jì)算"時(shí)序描述如下圖所示:

定義的含義是輸入數(shù)據(jù)在有效時(shí)鐘沿之后的TARRIVAL時(shí)刻到達(dá)。則,

TARRIVAL=TCKO+TOUTPUT+TLOGIC 公式1

根據(jù)上面介紹的周期(Period)公式,我們可以得到:

Tcko+Toutput+Tlogic+Tinput+Tsetup-Tclk_skew=Tclk; 公式2

將公式1代入公式2: Tarrival+Tinput+Tsetup-Tclk_skew=Tclk, 而Tclk_skew滿足時(shí)序關(guān)系后為負(fù),所以

TARRIVAL +TINPUT+TSETUP

這就是Tarrival應(yīng)該滿足的時(shí)序關(guān)系。其中TINPUT為輸入端的組合邏輯、網(wǎng)線和PAD的延遲之和,TSETUP為輸入同步元件的建立時(shí)間。

F 數(shù)據(jù)延時(shí)和數(shù)據(jù)到達(dá)時(shí)間的關(guān)系

TDELAY為要求的芯片內(nèi)部輸入延遲,其最大值TDELAY_MAX與輸入數(shù)據(jù)到達(dá)時(shí)間TARRIVAL的關(guān)系如上圖所示。也就是說: TDELAY_MAX+TARRIVAL=TPERIOD 公式4

所以:

TDELAY

G 要求輸出的穩(wěn)定時(shí)間

從下一級輸入端的延遲可以計(jì)算出當(dāng)前設(shè)計(jì)輸出的數(shù)據(jù)必須在何時(shí)穩(wěn)定下來,根據(jù)這個(gè)數(shù)據(jù)對設(shè)計(jì)輸出端的邏輯布線進(jìn)行約束,以滿足下一級的建立時(shí)間要求,保證下一級采樣的數(shù)據(jù)是穩(wěn)定的。計(jì)算要求的輸出穩(wěn)定時(shí)間如下圖所示:

公式的推導(dǎo)如下:

定義:TSTABLE = TLOGIC +TINPUT +TSETUP

從前面帖子介紹的周期(Period)公式,可以得到(其中TCLK_SKEW=TCLK1-TCLK2):

TCLK=TCKO+TOUTPUT+TLOGIC+TINPUT+TSETUP+TCLK_SKEW

將TSTABLE的定義代入到周期公式,可以得到:

TCLK=TCKO+TOUTPUT+TSTABLE+TCLK_SKEW

所以:TCKO +TOUTPUT+TSTABLE

這個(gè)公式就是TSTABLE必須要滿足的基本時(shí)序關(guān)系,即本級的輸出應(yīng)該保持怎么樣的穩(wěn)定狀態(tài),才能保證下級芯片的采樣穩(wěn)定。有時(shí)我們也稱這個(gè)約束 關(guān)系是輸出數(shù)據(jù)的保持時(shí)間的時(shí)序約束關(guān)系。只要滿足上述關(guān)系,當(dāng)前芯片輸出端的數(shù)據(jù)比時(shí)鐘上升沿提早TSTABLE 時(shí)間穩(wěn)定下來,下一級就可以正確地采樣數(shù)據(jù)。其中TOUTPUT為設(shè)計(jì)中連接同步元件輸出端的組合邏輯、網(wǎng)線和PAD的延遲之和,TCKO為同步元件時(shí)鐘 輸出時(shí)間。

H 實(shí)施時(shí)序約束的方法和命令

實(shí)施上述約束的基本方法是,根據(jù)已知時(shí)序信息,推算需要約束的時(shí)間值,實(shí)施約束。具體地說是這樣的,首先對于一般設(shè)計(jì),首先掌握的是TCLK,這個(gè) 對于設(shè)計(jì)者來說是個(gè)已知量。前面介紹公式和圖中的TCKO和TSETUP(注:有的工具軟件對TCKO和TSETUP的定義與前面圖形不同,還包含了到達(dá) 同步器件的一段logic的時(shí)延)是器件內(nèi)部固有的一個(gè)時(shí)間量,一般我們選取典型值,對于FPGA,這個(gè)量值比較小,一般不大于1~2ns。比較難以確定 的是TINPUT和TOUTPUT兩個(gè)時(shí)間量。

約束輸入時(shí)間偏移,需要知道TINPUT,TINPUT為輸入端的組合邏輯、網(wǎng)線和PAD的延遲之和,PAD的延時(shí)也根據(jù)器件型號也有典型值可選, 但是到達(dá)輸入端的組合邏輯電路和網(wǎng)線的延時(shí)就比較難以確定了,只能通過靜態(tài)時(shí)序分析工具分析,或者通過底層布局布線工具量取,有很大的經(jīng)驗(yàn)和試探的成分在 里面。

約束輸出時(shí)間偏移,需要知道TOUTPUT,TOUTPUT為設(shè)計(jì)中連接同步元件輸出端的組合邏輯、網(wǎng)線和PAD的延遲之和,仍然是到達(dá)輸出端的組 合邏輯電路和網(wǎng)線的延時(shí)就比較難以確定,需要通過靜態(tài)時(shí)序分析工具分析,或者通過底層布局布線工具量取,有很大的經(jīng)驗(yàn)和試探的成分在里面。

約束的具體命令根據(jù)約束工具不同而異,首先說使用Xilinx器件的情況下,實(shí)施上述約束的命令和方法。Xilinx把上述約束統(tǒng)稱 為:OFFSET約束(偏移約束),一共有4個(gè)相關(guān)約束屬性:OFFSET_IN_BEFORE、OFFSET_IN_AFTER、 OFFSET_OUT_BEFORE和OFFSET_OUT_AFTER。其中前兩個(gè)屬性叫做輸入偏移(OFFSET_IN)約束,基本功能相似,僅僅是 約束取的參考對象不同而已。后兩個(gè)屬性叫做輸出偏移(OFFSET_OUT)約束,基本功能相似,也是約束取的參考對象不同而已。為了便于理解,舉例說 明。

輸入偏移約束:時(shí)鐘周期為20ns,前級寄存器的TCKO選擇1ns,前級輸出邏輯延時(shí)TOUTPUT為3ns,中間邏輯TLOGIC的延時(shí)為 10ns,那么TARRIVAL=14ns,于是可以在數(shù)據(jù)輸入引腳附加NET DATA_IN OFFET=IN 14ns AFTER CLK約束,也可以使用OFFSET_IN_BEFORE對芯片內(nèi)部的輸入邏輯進(jìn)行約束,其語法如下:

NET DATA_IN OFFET=IN TDELAY BEFORE CLK

其中TDELAY為要求的芯片內(nèi)部輸入延遲,其最大值與輸入數(shù)據(jù)到達(dá)時(shí)間TARRIVAL的關(guān)系:TDELAY_MAX + TARRIVAL = TPERIOD,所以TDELAY < TPERIOD - TARRIVAL = 20 - 14 =6 ns。

輸出偏移約束:設(shè)時(shí)鐘周期為20ns,后級輸入邏輯延時(shí)TINPUT為4ns、建立時(shí)間TSETUP為1ns,中間邏輯TLOGIC的延時(shí)為 10ns,那么TSTABLE=15ns,于是可以在數(shù)據(jù)輸入引腳附加NET DATA_OUT OFFET=OUT 15ns BEFORE CLK約束,也可以直接對芯片內(nèi)部的輸出邏輯直接進(jìn)行約束,NET DATA_OUT OFFET=OUT TOUTPUT_DELAY AFTER CLK,其中TOUTPUT_DELAY為要求的芯片內(nèi)部輸出延遲,其最大值與要求的輸出數(shù)據(jù)穩(wěn)定時(shí)間TSTABLE的關(guān)系為:

TOUTPUT_DELAY_MAX+TSTABLE= TPERIOD。 TOUT_DELAY< TPERIOD - TSTABLE = 20 - 15 = 5ns