0 引言

綠色環(huán)保節(jié)能是全球化的熱潮,而嵌入式計(jì)算機(jī)系統(tǒng)被廣泛應(yīng)用于便攜式和移動(dòng)性較強(qiáng)的產(chǎn)品,低功耗設(shè)計(jì)不僅是綠色環(huán)保的要求,也是嵌入式計(jì)算機(jī)系統(tǒng)體積和質(zhì)量的約束。隨著市場(chǎng)對(duì)嵌入式計(jì)算機(jī)系統(tǒng)在體積和性能方面要求的不斷提升,小體積、高性能與有限的電池能量之間的矛盾曰益突出,系統(tǒng)低功耗設(shè)計(jì)是解決這一矛盾的有效手段。基于ARM的嵌入式計(jì)算機(jī)系統(tǒng)在保證系統(tǒng)性能的情況下通過硬件和軟件兩方面低功耗的設(shè)計(jì)來(lái)最大限度地降低嵌入式計(jì)算機(jī)系統(tǒng)的功耗。

1 系統(tǒng)組成

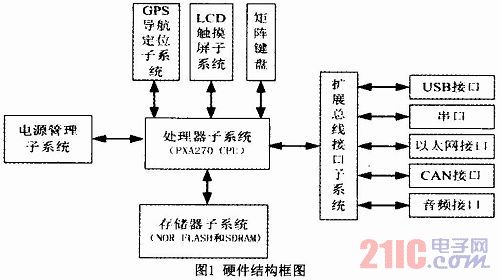

嵌入式計(jì)算機(jī)系統(tǒng)采用ARM9微處理器PXA270為核心,外圍擴(kuò)展了許多標(biāo)準(zhǔn)的IO接口來(lái)實(shí)現(xiàn)系統(tǒng)功能,如顯示、數(shù)據(jù)采集、定位、通信等功能。系統(tǒng)主要由處理器子系統(tǒng)、存儲(chǔ)器子系統(tǒng)、電源管理子系統(tǒng)、GPS導(dǎo)航定位子系統(tǒng)、LCD觸摸屏子系統(tǒng)、矩形鍵盤和擴(kuò)展總線接口子系統(tǒng)等組成,擴(kuò)展的標(biāo)準(zhǔn)IO接口包括USB接口、串口、以太網(wǎng)接口、CAN接口、音頻接口等,硬件結(jié)構(gòu)框圖如圖1所示。由于嵌入式計(jì)算機(jī)系統(tǒng)不能一直有充足的電源供應(yīng),需用電池來(lái)供電,所以設(shè)計(jì)過程中需要從各個(gè)細(xì)節(jié)考慮降低功率消耗,從而延長(zhǎng)電池使用時(shí)間。如圖1所示,系統(tǒng)隨著實(shí)現(xiàn)功能的增多相應(yīng)的功耗也會(huì)增大,根據(jù)系統(tǒng)組成主要的功耗在于微處理器、LCD觸摸屏、集成電路、電阻和有源器件等,設(shè)計(jì)過程中需要從全局來(lái)考慮功耗的設(shè)計(jì),下面將詳細(xì)描述功耗產(chǎn)生的原因和低功耗的設(shè)計(jì)與實(shí)現(xiàn)。

2 功耗產(chǎn)生的原因

如圖1所示的嵌入式計(jì)算機(jī)系統(tǒng)硬件架構(gòu)中,功耗主要來(lái)源于以下幾個(gè)方面:微處理器、LCD觸摸屏、集成電路、電阻和有源器件等。其中微處理器是系統(tǒng)功率消耗的主要來(lái)源,它幾乎占據(jù)了除LCD觸摸屏以外的整個(gè)系統(tǒng)功耗的一半以上,所以選擇低功耗的微處理器對(duì)于系統(tǒng)的功耗大小有舉足輕重的影響。LCD觸摸屏是嵌入式系統(tǒng)中功耗的另一個(gè)主要來(lái)源。除了微處理器和LCD觸摸屏之外,集成電路是系統(tǒng)組成的主要器件,對(duì)應(yīng)的電路中只要有電流流過,就會(huì)產(chǎn)生功耗。集成電路的功耗主要包括開關(guān)功耗、靜態(tài)功耗、動(dòng)態(tài)功耗、短路功耗和漏電功耗,對(duì)于目前大多數(shù)采用CMOS工藝的集成電路來(lái)說,主要的功耗是動(dòng)態(tài)功耗,是指電路翻轉(zhuǎn)時(shí)產(chǎn)生的功耗,它是由于電路翻轉(zhuǎn)時(shí)存在跳變沿,在翻轉(zhuǎn)的瞬間,電流較大,所以動(dòng)態(tài)功耗較大。除此之外,電阻和有源器件也是系統(tǒng)中功耗產(chǎn)生的一個(gè)原因,尤其在有源器件的狀態(tài)變化時(shí)產(chǎn)生較大的電流和電壓,引起較大的功率消耗。另外,CMOS電路中最大的功耗來(lái)自于內(nèi)部和外部的電容充放電產(chǎn)生的功耗。

據(jù)功耗產(chǎn)生的原因,結(jié)合實(shí)際的應(yīng)用環(huán)境,本設(shè)計(jì)的嵌入式計(jì)算機(jī)系統(tǒng)通過硬件和軟件的低功耗設(shè)計(jì)來(lái)實(shí)現(xiàn)系統(tǒng)的低功耗,下面詳細(xì)描述。

3 硬件的低功耗設(shè)計(jì)與實(shí)現(xiàn)

3.1 低功耗的微處理器選擇

如前所述,嵌入式計(jì)算機(jī)系統(tǒng)的微處理器是系統(tǒng)功耗的主要來(lái)源,所以在選擇微處理器即CPU時(shí),不僅要注意微處理器的性能優(yōu)劣(比如時(shí)鐘頻率)及提供的接口和功能多少,對(duì)于嵌入式計(jì)算機(jī)系統(tǒng)來(lái)說也要注重微處理器的功耗特性。微處理器的功耗包括內(nèi)核消耗功耗和外部接口消耗功耗,內(nèi)核消耗功耗主要體現(xiàn)在供電電壓和時(shí)鐘頻率的高低;外部接口消耗功耗體現(xiàn)在專門I/O控制器的功耗。

在本系統(tǒng)的設(shè)計(jì)中通過對(duì)微處理器的性能和功耗的比較和衡量,我們選擇了低功耗的微處理器PXA270,PXA270的主頻可以設(shè)置在104MHz到624MHz之間;PXA270嵌入式處理器在個(gè)人的互聯(lián)網(wǎng)客戶端架構(gòu)處理器(PCA)中集成無(wú)線MMX技術(shù),使得它擁有高性能、低功耗的多媒體加速能力,能夠很好地支持MPEG4和MP3解碼;同時(shí)加入了Intel Speed Step動(dòng)態(tài)電源管理技術(shù),在保證CPU性能的情況下,最大限度地降低小型嵌入式計(jì)算機(jī)系統(tǒng)的功耗。

3.2 接口電路的低功耗設(shè)計(jì)

嵌入式計(jì)算機(jī)系統(tǒng)的接口電路的低功耗設(shè)計(jì)主要體現(xiàn)在以下幾個(gè)方面:

(1)選擇靜態(tài)電流較低的外圍芯片,設(shè)計(jì)中除考慮系統(tǒng)的功能實(shí)現(xiàn)以外,在外圍接口芯片如USB接口、串口、以太網(wǎng)接口、CAN接口、音頻接口的設(shè)計(jì)芯片都盡量選擇靜態(tài)電流較低的芯片來(lái)實(shí)現(xiàn)系統(tǒng)功能。

(2)恰當(dāng)?shù)剡x擇上拉電阻/下拉電阻。對(duì)于嵌入式計(jì)算機(jī)系統(tǒng)的接口電路設(shè)計(jì),許多信號(hào)管腳都涉及上拉電阻或下拉電阻,在設(shè)計(jì)中考慮能正常驅(qū)動(dòng)后級(jí)信號(hào)的情況下,上拉電阻或下拉電阻盡量選擇較大的阻值。如同樣是在3.3V的系統(tǒng)中用10kΩ的上拉電阻比用4.7kΩ的上拉電阻,當(dāng)輸出為低時(shí),每只腳上的電流消耗少0.37mA,若系統(tǒng)設(shè)計(jì)中存在100個(gè)這樣的管腳,就減少了37mA的電流。系統(tǒng)的接口電路中多數(shù)情況為低的信號(hào)設(shè)計(jì)上用下拉電阻來(lái)節(jié)省功耗。

(3)懸空腳盡量接地或上拉到VCC。系統(tǒng)中的集成電路基本都是CMOS器件,CMOS器件由于其懸空的輸入端的阻抗極高,很可能感應(yīng)一些電荷導(dǎo)致器件被高壓擊穿,而且還會(huì)導(dǎo)致輸入端信號(hào)電平隨機(jī)變化,導(dǎo)致CPU在休眠時(shí)不斷地被喚醒,從而無(wú)法進(jìn)入休眠狀態(tài)或出現(xiàn)其他莫名其妙的故障,所以設(shè)計(jì)上未使用的懸空腳要盡量接地或上拉到VCC,減少不必要的功耗。

(4)慎重選擇Buffer。在以往的設(shè)計(jì)中,設(shè)計(jì)人員習(xí)慣用Buffer來(lái)增加電路的驅(qū)動(dòng)能力,這些Buffer肯定會(huì)導(dǎo)致更多的功耗。在系統(tǒng)設(shè)計(jì)中,仔細(xì)檢查每個(gè)芯片的最大輸出電流IOH和IOL是否足以驅(qū)動(dòng)下級(jí)芯片,通過選取合適的前后級(jí)芯片來(lái)避免不必要的Buffer,來(lái)盡量減少系統(tǒng)的功率消耗。

3.3 電源供給電路的低功耗設(shè)計(jì)

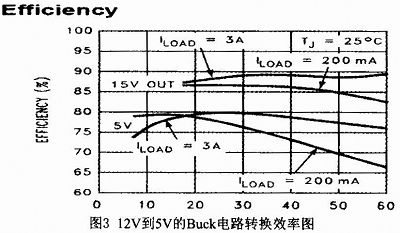

嵌入式計(jì)算機(jī)系統(tǒng)的電源供給電路需考慮合適的電壓變換結(jié)構(gòu)。一般來(lái)說,電壓變換結(jié)構(gòu)包括線性穩(wěn)壓和DC/DC變換電路兩種主要方式,其中線性穩(wěn)壓的特點(diǎn)是電路結(jié)構(gòu)簡(jiǎn)單,所需元件數(shù)量少,輸入和輸出壓差可以很大,但其致命弱點(diǎn)就是效率低、功耗高。其效率完全取決于輸出電壓大小。DC/DC變換電路的特點(diǎn)是效率高、升降壓靈活,但缺點(diǎn)是電路相對(duì)復(fù)雜,干擾較大。一般常見的DC/DC變換電路由Boost和Buck兩種電路,其中Boost電路用于升壓,Buck電路用于降壓。

圖2所示是嵌入式計(jì)算機(jī)系統(tǒng)采用的12V轉(zhuǎn)換到5V的DC/DC變換電路圖,其控制芯片采用國(guó)家半導(dǎo)體(NS)的LM2576,實(shí)際是采用Buck電路,其MOSFET和相關(guān)的控制電路位于芯片內(nèi)部。

圖3所示為12V到5V轉(zhuǎn)換電路的轉(zhuǎn)換效率圖,如圖所示當(dāng)輸入為12V,輸出為5V時(shí),轉(zhuǎn)換效率約為77%(ILOAD=3A),差不多為線性穩(wěn)壓器轉(zhuǎn)換效率的一倍。

在嵌入式計(jì)算機(jī)系統(tǒng)的電源部分設(shè)計(jì)選擇了DC/DC轉(zhuǎn)換電路(LM7256S)將12V轉(zhuǎn)換為5V,12V轉(zhuǎn)換為3.3V供系統(tǒng)使用,這種處理方式有效的節(jié)約了能源,降低了整機(jī)的功耗。

4 軟件的低功耗設(shè)計(jì)與實(shí)現(xiàn)

4.1 動(dòng)態(tài)設(shè)置時(shí)鐘頻率

對(duì)于已經(jīng)搭建好的硬件系統(tǒng)來(lái)說,系統(tǒng)已經(jīng)定型,從硬件設(shè)計(jì)上已不能做更多的考慮,這時(shí)我們只能從軟件入手來(lái)實(shí)現(xiàn)系統(tǒng)的低功耗設(shè)計(jì)。而對(duì)于軟件的低功耗設(shè)計(jì)最切實(shí)可行的就是實(shí)現(xiàn)動(dòng)態(tài)電源管理,所謂動(dòng)態(tài)的電源管理就是在系統(tǒng)運(yùn)行期間通過對(duì)系統(tǒng)的時(shí)鐘或電壓的動(dòng)態(tài)控制來(lái)達(dá)到節(jié)省功率的目的,這種動(dòng)態(tài)控制是與系統(tǒng)的運(yùn)行狀態(tài)密切相關(guān)的。

在嵌入式計(jì)算機(jī)系統(tǒng)中,軟件設(shè)計(jì)上動(dòng)態(tài)地通過設(shè)置時(shí)鐘頻率來(lái)降低系統(tǒng)的功耗,換句話說就是為系統(tǒng)選取合適的工作模式。系統(tǒng)采用的微處理器是ARM處理器PX270,PXA270處理器的內(nèi)部的各種頻率都是通過外部晶振頻率經(jīng)內(nèi)部鎖相環(huán)(PLL)倍頻后產(chǎn)生的,可通過內(nèi)部的寄存器設(shè)置各種工作頻率來(lái)控制功耗。PXA270處理器共有四種工作模式:正常模式、空閑模式、休眠模式、待命模式,各種模式的功耗如表1所示。

由表1可見,PXA270在全速運(yùn)行的時(shí)候比在空閑或者休眠的時(shí)候消耗的功率大得多。省電的原則就是讓正常運(yùn)行模式遠(yuǎn)比空閑、休眠模式少占用時(shí)間。在嵌入式計(jì)算機(jī)系統(tǒng)中,系統(tǒng)在全速運(yùn)行的時(shí)候遠(yuǎn)比空閑的時(shí)候少,所以設(shè)計(jì)上可通過設(shè)置使PXA270盡可能工作在空閑狀態(tài),然后通過相應(yīng)的中斷喚醒PXA270恢復(fù)到正常工作模式,處理響應(yīng)的事件,然后再進(jìn)入空閑模式。這樣的軟件設(shè)計(jì)方式可盡可能地降低系統(tǒng)的功耗。

4.2 動(dòng)態(tài)控制外設(shè)控制寄存器

PXA270處理器提供的接口控制器很多,如ADC、I2C、I2S、LCD、Flash、Timer、UART、SPI、USB等,實(shí)際應(yīng)用中只使用了部分功能,ADC、I2C、I2S和SPI都沒有用到,為節(jié)省系統(tǒng)功耗,需動(dòng)態(tài)地關(guān)注這些接口控制器的狀態(tài),及時(shí)關(guān)閉不需要的外設(shè)控制器,因?yàn)槿舨粚⒉挥玫慕涌诳刂破麝P(guān)閉,即使它們沒有處于工作狀態(tài),仍然會(huì)消耗電流。軟件通過CLKCON寄存器的設(shè)置,關(guān)閉不需要的功能模塊,經(jīng)測(cè)量可節(jié)省2mA的電流。另外,動(dòng)態(tài)關(guān)閉一些仍然需要的外設(shè)控制器來(lái)進(jìn)一步節(jié)省能量。

如在空閑模式下,PXA270內(nèi)核停止運(yùn)行,我們還可以進(jìn)一步關(guān)閉一些其他的外設(shè)控制器,如USB、SDI、FLASH等,只要保證喚醒PXA270的

I/O控制器正常工作即可,如通過UART喚醒,則UART控制器不能被關(guān)閉。等到PXA270被喚醒后,再將USB、SDI、Flash等控制器打開。

上述的軟件低功耗設(shè)計(jì)的兩種方式,一種是通過改變了系統(tǒng)的時(shí)鐘頻率,另一種是通過控制外設(shè)控制器的開關(guān)來(lái)達(dá)到節(jié)約能量的目的。除此之外,同時(shí)可通過動(dòng)態(tài)改變處理器的電壓和頻率來(lái)進(jìn)一步節(jié)省功率,我們選擇的PXA270微處理器就加入了Intel Speed Step動(dòng)態(tài)電源管理技術(shù),在保證CPU性能的情況下,最大限度地降低嵌入式計(jì)算機(jī)系統(tǒng)的功耗。

5 結(jié)束語(yǔ)

嵌入式計(jì)算機(jī)系統(tǒng)的低功耗設(shè)計(jì),本身就是理論和設(shè)計(jì)實(shí)踐相結(jié)和的問題,要降低功耗,系統(tǒng)中各個(gè)環(huán)節(jié)都不容忽視,這也是一個(gè)不斷優(yōu)化的過程。本文的設(shè)計(jì)中綜合考慮各種可能的因素、條件和狀態(tài),對(duì)各種細(xì)節(jié)進(jìn)行認(rèn)真的斟酌和分析,取得了較為滿意的效果,達(dá)到降低系統(tǒng)功耗的目的。該設(shè)計(jì)已在產(chǎn)品應(yīng)用,性能穩(wěn)定,功耗較低。