MOSFET的 工作原理

MOSFET的原意是:MOS(Metal Oxide Semiconductor金屬氧化物半導(dǎo)體),F(xiàn)ET(Field Effect Transistor場(chǎng)效應(yīng)晶體管),即以金屬層(M)的柵極隔著氧化層(O)利用電場(chǎng)的效應(yīng)來控制半導(dǎo)體(S)的場(chǎng)效應(yīng)晶體管。

功率場(chǎng)效應(yīng)晶體管也分為結(jié)型和絕緣柵型,但通常主要指絕緣柵型中的MOS型(Metal Oxide Semiconductor FET),簡(jiǎn)稱功率MOSFET(Power MOSFET)。結(jié)型功率場(chǎng)效應(yīng)晶體管一般稱作靜電感應(yīng)晶體管(Static Induction Transistor——SIT)。其特點(diǎn)是用柵極電壓來控制漏極電流,驅(qū)動(dòng)電路簡(jiǎn)單,需要的驅(qū)動(dòng)功率小,開關(guān)速度快,工作頻率高,熱穩(wěn)定性優(yōu)于GTR,但其電流容量小,耐壓低,一般只適用于功率不超過10kW的電力電子裝置。

2.功率MOSFET的結(jié)構(gòu)和工作原理

功率MOSFET的種類:按導(dǎo)電溝道可分為P溝道和N溝道。按柵極電壓幅值可分為;耗盡型;當(dāng)柵極電壓為零時(shí)漏源極之間就存在導(dǎo)電溝道,增強(qiáng)型;對(duì)于N(P)溝道器件,柵極電壓大于(小于)零時(shí)才存在導(dǎo)電溝道,功率MOSFET主要是N溝道增強(qiáng)型。

2.1.功率MOSFET的結(jié)構(gòu)

功率MOSFET的內(nèi)部結(jié)構(gòu)和電氣符號(hào)如圖1所示;其導(dǎo)通時(shí)只有一種極性的載流子(多子)參與導(dǎo)電,是單極型晶體管。導(dǎo)電機(jī)理與小功率MOS管相同,但結(jié)構(gòu)上有較大區(qū)別,小功率MOS管是橫向?qū)щ娖骷β蔒OSFET大都采用垂直導(dǎo)電結(jié)構(gòu),又稱為VMOSFET(Vertical MOSFET),大大提高了MOSFET器件的耐壓和耐電流能力。

功率MOSFET的結(jié)構(gòu)圖

按垂直導(dǎo)電結(jié)構(gòu)的差異,又分為利用V型槽實(shí)現(xiàn)垂直導(dǎo)電的VVMOSFET和具有垂直導(dǎo)電雙擴(kuò)散MOS結(jié)構(gòu)的VDMOSFET(Vertical Double-diffused MOSFET),本文主要以VDMOS器件為例進(jìn)行討論。

功率MOSFET為多元集成結(jié)構(gòu),如國(guó)際整流器公司(International Rectifier)的HEXFET采用了六邊形單元;西門子公司(Siemens)的SIPMOSFET采用了正方形單元;摩托羅拉公司(Motorola)的TMOS采用了矩形單元按“品”字形排列。

2.2.功率MOSFET的工作原理

截止:漏源極間加正電源,柵源極間電壓為零。P基區(qū)與N漂移區(qū)之間形成的PN結(jié)J1反偏,漏源極之間無電流流過。

導(dǎo)電:在柵源極間加正電壓UGS,柵極是絕緣的,所以不會(huì)有柵極電流流過。但柵極的正電壓會(huì)將其下面P區(qū)中的空穴推開,而將P區(qū)中的少子—電子吸引到柵極下面的P區(qū)表面

當(dāng)UGS大于UT(開啟電壓或閾值電壓)時(shí),柵極下P區(qū)表面的電子濃度將超過空穴濃度,使P型半導(dǎo)體反型成N型而成為反型層,該反型層形成N溝道而使PN結(jié)J1消失,漏極和源極導(dǎo)電。

2.3.功率MOSFET的基本特性

2.3.1靜態(tài)特性MOSFET的轉(zhuǎn)移特性和輸出特性。

漏極電流ID和柵源間電壓UGS的關(guān)系稱為MOSFET的轉(zhuǎn)移特性,ID較大時(shí),ID與UGS的關(guān)系近似線性,曲線的斜率定義為跨導(dǎo)Gfs

MOSFET的漏極伏安特性(輸出特性):截止區(qū)(對(duì)應(yīng)于GTR的截止區(qū));飽和區(qū)(對(duì)應(yīng)于GTR的放大區(qū));非飽和區(qū)(對(duì)應(yīng)于GTR的飽和區(qū))。電力MOSFET工作在開關(guān)狀態(tài),即在截止區(qū)和非飽和區(qū)之間來回轉(zhuǎn)換。電力MOSFET漏源極之間有寄生二極管,漏源極間加反向電壓時(shí)器件導(dǎo)通。電力MOSFET的通態(tài)電阻具有正溫度系數(shù),對(duì)器件并聯(lián)時(shí)的均流有利。

2.3.2動(dòng)態(tài)特性MOSFET其測(cè)試電路和開關(guān)過程。

開通過程;開通延遲時(shí)間td(on) —Up前沿時(shí)刻到UGS=UT并開始出現(xiàn)iD的時(shí)刻間的時(shí)間段;上升時(shí)間tr— UGS從UT上升到MOSFET進(jìn)入非飽和區(qū)的柵壓UGSP的時(shí)間段;iD穩(wěn)態(tài)值由漏極電源電壓UE和漏極負(fù)載電阻決定。UGSP的大小和iD的穩(wěn)態(tài)值有關(guān),UGS達(dá)到UGSP后,在up作用下繼續(xù)升高直至達(dá)到穩(wěn)態(tài),但iD已不變。開通時(shí)間ton—開通延遲時(shí)間與上升時(shí)間之和。

關(guān)斷延遲時(shí)間td(off) —Up下降到零起,Cin通過RS和RG放電,UGS按指數(shù)曲線下降到UGSP時(shí),iD開始減小為零的時(shí)間段。下降時(shí)間tf— UGS從UGSP繼續(xù)下降起,iD減小,到UGS

2.3.3MOSFET的開關(guān)速度MOSFET的開關(guān)速度和Cin充放電有很大關(guān)系,使用者無法降低Cin,但可降低驅(qū)動(dòng)電路內(nèi)阻Rs減小時(shí)間常數(shù),加快開關(guān)速度,MOSFET只靠多子導(dǎo)電,不存在少子儲(chǔ)存效應(yīng),因而關(guān)斷過程非常迅速,開關(guān)時(shí)間在10~100ns之間,工作頻率可達(dá)100kHz以上,是主要電力電子器件中最高的。

場(chǎng)控器件靜態(tài)時(shí)幾乎不需輸入電流。但在開關(guān)過程中需對(duì)輸入電容充放電,仍需一定的驅(qū)動(dòng)功率。開關(guān)頻率越高,所需要的驅(qū)動(dòng)功率越大。

4.動(dòng)態(tài)性能的改進(jìn)

在器件應(yīng)用時(shí)除了要考慮器件的電壓、電流、頻率外,還必須掌握在應(yīng)用中如何保護(hù)器件,不使器件在瞬態(tài)變化中受損害。當(dāng)然晶閘管是兩個(gè)雙極型晶體管的組合,又加上因大面積帶來的大電容,所以其du/dt能力是較為脆弱的。對(duì)di/dt來說,它還存在一個(gè)導(dǎo)通區(qū)的擴(kuò)展問題,所以也帶來相當(dāng)嚴(yán)格的限制。

功率MOSFET的情況有很大的不同。它的dv/dt及di/dt的能力常以每納秒(而不是每微秒)的能力來估量。但盡管如此,它也存在動(dòng)態(tài)性能的限制。這些我們可以從功率MOSFET的基本結(jié)構(gòu)來予以理解。

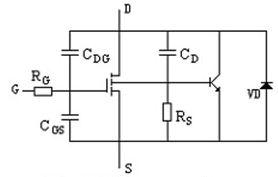

功率MOSFET的等效電路圖

上圖是功率MOSFET的等效電路,在應(yīng)用中除了要考慮功率MOSFET每一部分都存在電容以外,還必須考慮MOSFET還并聯(lián)著一個(gè)二極管。同時(shí)從某個(gè)角度看、它還存在一個(gè)寄生晶體管。(就像IGBT也寄生著一個(gè)晶閘管一樣)。這幾個(gè)方面,是研究MOSFET動(dòng)態(tài)特性很重要的因素。

首先MOSFET 結(jié)構(gòu)中所附帶的本征二極管具有一定的雪崩能力。通常用單次雪崩能力和重復(fù)雪崩能力來表達(dá)。當(dāng)反向di/dt很大時(shí),二極管會(huì)承受一個(gè)速度非常快的脈沖尖刺,它有可能進(jìn)入雪崩區(qū),一旦超越其雪崩能力就有可能將器件損壞。作為任一種PN結(jié)二極管來說,仔細(xì)研究其動(dòng)態(tài)特性是相當(dāng)復(fù)雜的。它們和我們一般理解PN 結(jié)正向時(shí)導(dǎo)通反向時(shí)阻斷的簡(jiǎn)單概念很不相同。當(dāng)電流迅速下降時(shí),二極管有一階段失去反向阻斷能力,即所謂反向恢復(fù)時(shí)間。PN結(jié)要求迅速導(dǎo)通時(shí),也會(huì)有一段時(shí)間并不顯示很低的電阻。在功率MOSFET中一旦二極管有正向注入,所注入的少數(shù)載流子也會(huì)增加作為多子器件的MOSFET的復(fù)雜性。

功率MOSFET的設(shè)計(jì)過程中采取措施使其中的寄生晶體管盡量不起作用。在不同代功率MOSFET中其措施各有不同,但總的原則是使漏極下的橫向電阻RB 盡量小。因?yàn)橹挥性诼ON區(qū)下的橫向電阻流過足夠電流為這個(gè)N區(qū)建立正偏的條件時(shí),寄生的雙極性晶閘管才開始發(fā)難。然而在嚴(yán)峻的動(dòng)態(tài)條件下,因du/dt 通過相應(yīng)電容引起的橫向電流有可能足夠大。此時(shí)這個(gè)寄生的雙極性晶體管就會(huì)起動(dòng),有可能給MOSFET帶來?yè)p壞。所以考慮瞬態(tài)性能時(shí)對(duì)功率MOSFET器件內(nèi)部的各個(gè)電容(它是dv/dt的通道)都必須予以注意。

瞬態(tài)情況是和線路情況密切相關(guān)的,這方面在應(yīng)用中應(yīng)給予足夠重視。對(duì)器件要有深入了解,才能有利于理解和分析相應(yīng)的問題。

4.功率MOSFET驅(qū)動(dòng)電路

功率MOSFET是電壓型驅(qū)動(dòng)器件,沒有少數(shù)載流子的存貯效應(yīng),輸入阻抗高,因而開關(guān)速度可以很高,驅(qū)動(dòng)功率小,電路簡(jiǎn)單。但功率MOSFET的極間電容較大,輸入電容CISS、輸出電容COSS和反饋電容CRSS與極間電容的關(guān)系可表述為: 功率MOSFET的柵極輸入端相當(dāng)于一個(gè)容性網(wǎng)絡(luò),它的工作速度與驅(qū)動(dòng)源內(nèi)阻抗有關(guān)。由于 CISS的存在,靜態(tài)時(shí)柵極驅(qū)動(dòng)電流幾乎為零,但在開通和關(guān)斷動(dòng)態(tài)過程中,仍需要一定的驅(qū)動(dòng)電流。假定開關(guān)管飽和導(dǎo)通需要的柵極電壓值為VGS,開關(guān)管的開通時(shí)間TON包括開通延遲時(shí)間TD和上升時(shí)間TR兩部分。

開關(guān)管關(guān)斷過程中,CISS通過ROFF放電,COSS由RL充電,COSS較大,VDS(T)上升較慢,隨著VDS(T)上升較慢,隨著VDS(T)的升高COSS迅速減小至接近于零時(shí),VDS(T)再迅速上升。

根據(jù)以上對(duì)功率MOSFET特性的分析,其驅(qū)動(dòng)通常要求:觸發(fā)脈沖要具有足夠快的上升和下降速度;②開通時(shí)以低電阻力柵極電容充電,關(guān)斷時(shí)為柵極提供低電阻放電回路,以提高功率MOSFET的開關(guān)速度;③為了使功率MOSFET可靠觸發(fā)導(dǎo)通,觸發(fā)脈沖電壓應(yīng)高于管子的開啟電壓,為了防止誤導(dǎo)通,在其截止時(shí)應(yīng)提供負(fù)的柵源電壓;④功率開關(guān)管開關(guān)時(shí)所需驅(qū)動(dòng)電流為柵極電容的充放電電流,功率管極間電容越大,所需電流越大,即帶負(fù)載能力越大。

4.1幾種MOSFET驅(qū)動(dòng)電路介紹及分析

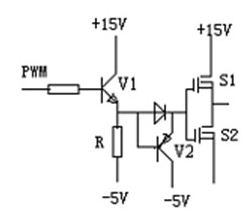

不隔離的互補(bǔ)驅(qū)動(dòng)電路圖

a)為常用的小功率驅(qū)動(dòng)電路,簡(jiǎn)單可靠成本低。適用于不要求隔離的小功率開關(guān)設(shè)備。圖7(b)所示驅(qū)動(dòng)電路開關(guān)速度很快,驅(qū)動(dòng)能力強(qiáng),為防止兩個(gè)MOSFET管直通,通常串接一個(gè)0.5~1Ω小電阻用于限流,該電路適用于不要求隔離的中功率開關(guān)設(shè)備。這兩種電路特點(diǎn)是結(jié)構(gòu)簡(jiǎn)單。

功率MOSFET 屬于電壓型控制器件,只要柵極和源極之間施加的電壓超過其閥值電壓就會(huì)導(dǎo)通。由于MOSFET存在結(jié)電容,關(guān)斷時(shí)其漏源兩端電壓的突然上升將會(huì)通過結(jié)電容在柵源兩端產(chǎn)生干擾電壓。常用的互補(bǔ)驅(qū)動(dòng)電路的關(guān)斷回路阻抗小,關(guān)斷速度較快,但它不能提供負(fù)壓,故抗干擾性較差。為了提高電路的抗干擾性,可在此種驅(qū)動(dòng)電路的基礎(chǔ)上增加一級(jí)有V1、V2、R組成的電路,產(chǎn)生一個(gè)負(fù)壓,電路原理圖如圖8所示。

提供負(fù)壓的互補(bǔ)電路圖

當(dāng)V1 導(dǎo)通時(shí),V2關(guān)斷,兩個(gè)MOSFET中的上管的柵、源極放電,下管的柵、源極充電,即上管關(guān)斷,下管導(dǎo)通,則被驅(qū)動(dòng)的功率管關(guān)斷;反之V1關(guān)斷時(shí),V2導(dǎo)通,上管導(dǎo)通,下管關(guān)斷,使驅(qū)動(dòng)的管子導(dǎo)通。因?yàn)樯舷聝蓚€(gè)管子的柵、源極通過不同的回路充放電,包含有V2的回路,由于V2會(huì)不斷退出飽和直至關(guān)斷,所以對(duì)于S1而言導(dǎo)通比關(guān)斷要慢,對(duì)于S2而言導(dǎo)通比關(guān)斷要快,所以兩管發(fā)熱程度也不完全一樣,S1比S2發(fā)熱嚴(yán)重。

該驅(qū)動(dòng)電路的缺點(diǎn)是需要雙電源,且由于R的取值不能過大,否則會(huì)使V1深度飽和,影響關(guān)斷速度,所以R上會(huì)有一定的損耗。

4.1.2隔離的驅(qū)動(dòng)電路

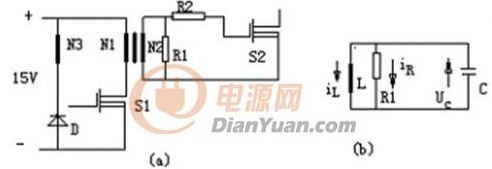

正激驅(qū)動(dòng)電路

(1)正激式驅(qū)動(dòng)電路。電路原理如圖9(a)所示,N3為去磁繞組,S2為所驅(qū)動(dòng)的功率管。R2為防止功率管柵極、源極端電壓振蕩的一個(gè)阻尼電阻。因不要求漏感較小,且從速度方面考慮,一般R2較小,故在分析中忽略不計(jì)。

其等效電路圖如圖9 (b)所示脈沖不要求的副邊并聯(lián)一電阻R1,它做為正激變換器的假負(fù)載,用于消除關(guān)斷期間輸出電壓發(fā)生振蕩而誤導(dǎo)通。同時(shí)它還可以作為功率MOSFET關(guān)斷時(shí)的能量泄放回路。該驅(qū)動(dòng)電路的導(dǎo)通速度主要與被驅(qū)動(dòng)的S2柵極、源極等效輸入電容的大小、S1的驅(qū)動(dòng)信號(hào)的速度以及S1所能提供的電流大小有關(guān)。由仿真及分析可知,占空比D越小、R1越大、L越大,磁化電流越小,U1值越小,關(guān)斷速度越慢。該電路具有以下優(yōu)點(diǎn):

①電路結(jié)構(gòu)簡(jiǎn)單可靠,實(shí)現(xiàn)了隔離驅(qū)動(dòng)。

②只需單電源即可提供導(dǎo)通時(shí)的正、關(guān)斷時(shí)負(fù)壓。

③占空比固定時(shí),通過合理的參數(shù)設(shè)計(jì),此驅(qū)動(dòng)電路也具有較快的開關(guān)速度。

該電路存在的缺點(diǎn):一是由于隔離變壓器副邊需要噎嗝假負(fù)載防振蕩,故電路損耗較大;二是當(dāng)占空比變化時(shí)關(guān)斷速度變化較大。脈寬較窄時(shí),由于是儲(chǔ)存的能量減少導(dǎo)致MOSFET柵極的關(guān)斷速度變慢。

MOSFET柵極的關(guān)斷速度變慢。

有隔離變壓器的互補(bǔ)驅(qū)動(dòng)電路

(2)有隔離變壓器的互補(bǔ)驅(qū)動(dòng)電路。如圖10所示,V1、V2為互補(bǔ)工作,電容C起隔離直流的作用,T1為高頻、高磁率的磁環(huán)或磁罐。

導(dǎo)通時(shí)隔離變壓器上的電壓為(1-D)Ui、關(guān)斷時(shí)為D Ui,若主功率管S可靠導(dǎo)通電壓為12V,而隔離變壓器原副邊匝比N1/N2為12/(1-D)/ Ui。為保證導(dǎo)通期間GS電壓穩(wěn)定C值可稍取大些。該電路具有以下優(yōu)點(diǎn):

①電路結(jié)構(gòu)簡(jiǎn)單可靠,具有電氣隔離作用。當(dāng)脈寬變化時(shí),驅(qū)動(dòng)的關(guān)斷能力不會(huì)隨著變化。

②該電路只需一個(gè)電源,即為單電源工作。隔直電容C的作用可以在關(guān)斷所驅(qū)動(dòng)的管子時(shí)提供一個(gè)負(fù)壓,從而加速了功率管的關(guān)斷,且有較高的抗干擾能力。

但該電路存在的一個(gè)較大缺點(diǎn)是輸出電壓的幅值會(huì)隨著占空比的變化而變化。當(dāng)D 較小時(shí),負(fù)向電壓小,該電路的抗干擾性變差,且正向電壓較高,應(yīng)該注意使其幅值不超過MOSFET柵極的允許電壓。當(dāng)D大于0.5時(shí)驅(qū)動(dòng)電壓正向電壓小于其負(fù)向電壓,此時(shí)應(yīng)該注意使其負(fù)電壓值不超過MOAFET柵極允許電壓。所以該電路比較適用于占空比固定或占空比變化范圍不大以及占空比小于0.5的場(chǎng)合。

(3)集成芯片UC3724/3725構(gòu)成的驅(qū)動(dòng)電路

集成芯片UC3724/3725構(gòu)成的驅(qū)動(dòng)電路

電路構(gòu)成如圖11 所示。其中UC3724用來產(chǎn)生高頻載波信號(hào),載波頻率由電容CT和電阻RT決定。一般載波頻率小于600kHz,4腳和6腳兩端產(chǎn)生高頻調(diào)制波,經(jīng)高頻小磁環(huán)變壓器隔離后送到UC3725芯片7、8兩腳經(jīng)UC3725進(jìn)行調(diào)制后得到驅(qū)動(dòng)信號(hào),UC3725內(nèi)部有一肖特基整流橋同時(shí)將7、8腳的高頻調(diào)制波整流成一直流電壓供驅(qū)動(dòng)所需功率。一般來說載波頻率越高驅(qū)動(dòng)延時(shí)越小,但太高抗干擾變差;隔離變壓器磁化電感越大磁化電流越小,UC3724發(fā)熱越少,但太大使匝數(shù)增多導(dǎo)致寄生參數(shù)影響變大,同樣會(huì)使抗干擾能力降低。根據(jù)實(shí)驗(yàn)數(shù)據(jù)得出:對(duì)于開關(guān)頻率小于100kHz的信號(hào)一般取(400~500)kHz載波頻率較好,變壓器選用較高磁導(dǎo)如5K、7K等高頻環(huán)形磁芯,其原邊磁化電感小于約1毫亨左右為好。這種驅(qū)動(dòng)電路僅適合于信號(hào)頻率小于100kHz的場(chǎng)合,因信號(hào)頻率相對(duì)載波頻率太高的話,相對(duì)延時(shí)太多,且所需驅(qū)動(dòng)功率增大,UC3724和UC3725芯片發(fā)熱溫升較高,故100kHz以上開關(guān)頻率僅對(duì)較小極電容的MOSFET才可以。對(duì)于1kVA左右開關(guān)頻率小于100kHz的場(chǎng)合,它是一種良好的驅(qū)動(dòng)電路。該電路具有以下特點(diǎn):?jiǎn)坞娫垂ぷ鳎刂菩盘?hào)與驅(qū)動(dòng)實(shí)現(xiàn)隔離,結(jié)構(gòu)簡(jiǎn)單尺寸較小,尤其適用于占空比變化不確定或信號(hào)頻率也變化的場(chǎng)合。

5.功率MOSFE發(fā)展與研發(fā)

MOSFET漏源之間的電流通過一個(gè)溝道(CHANNEL)上的柵(GATE)來控制。按MOSFET的原意,MOS代表金屬(METAL)-氧化物(OXIDE)-半導(dǎo)體(SEMICONDUCTOR),即以金屬層(M)的柵極隔著氧化層(O)利用電場(chǎng)的效應(yīng)來控制半導(dǎo)體(S)。FET (FIELDEFFECTTRANSISTOR場(chǎng)效應(yīng)晶體管)的名字也由此而來。然而我HEXFET中的柵極并不是金屬做的,而是用多晶硅(POLY)來做柵極,這也就是圖中所注明的硅柵極(SILICONGATE)。IR在1978年時(shí)是用金屬做柵極的,1979年的GEN-1HEXFET是世界上第一個(gè)采用多晶硅柵極的多原胞型功率MOSFET。

IR 功率MOSFET的基本結(jié)構(gòu)中每一個(gè)六角形是一個(gè)MOSFET的原胞(CELL)。正因?yàn)樵橇切蔚模℉EXANGULAR),因而IR常把它稱為 HEXFET。功率MOSFET通常由許多個(gè)MOSFET原胞組成。已風(fēng)行了十余年的IR第三代(GEN-3)HEXFET每平方厘米約有18萬個(gè)原胞,目前世界上密度最高的IR第八代(GEN-8)HEXFET每平方厘米已有1740萬個(gè)原胞。這就完全可以理解,現(xiàn)代功率半導(dǎo)體器件的精細(xì)工藝已和微電子電路相當(dāng)。新一代功率器件的制造技術(shù)已進(jìn)入亞微米時(shí)代。

作為功率MOSFET 來說,有兩項(xiàng)參數(shù)是最重要的。一個(gè)是RDS(ON),即通態(tài)時(shí)的漏源電阻。另一個(gè)是QG,即柵極電荷,實(shí)際即柵極電容。柵極電容細(xì)分起來可分成好幾個(gè)部分,與器件的外特性輸入與輸出電容也有較復(fù)雜的關(guān)系。除此之外有些瞬態(tài)參數(shù)也需要很好考慮,這些我們留到后面再談。

5.1通態(tài)漏源電阻RDS(ON)的降低

為降低RDS(ON),先要分析一下RDS(ON)是由哪些部分組成。這些電阻主要包括:

5.1.1 RCH:溝道電阻,即柵極下溝道的電阻。

5.1.2 RJ:JFET電阻,即把各原胞的P-基區(qū)(P-BASE)所夾住的那部分看為JEFT。JEFT是結(jié)型場(chǎng)效應(yīng)晶體管(JUNCTIONFET)的簡(jiǎn)稱。結(jié)型場(chǎng)效應(yīng)管是以PN結(jié)上的電場(chǎng)來控制所夾溝道中的電流。雖同稱為場(chǎng)效應(yīng)晶體管,但它和MOSFET是以表面電場(chǎng)來控制溝道中的電流情況不同,所以 MOSFET有時(shí)也被稱為表面場(chǎng)效應(yīng)管。

5.1.3 RD:漂移層電阻,主要是外延層中的電阻。一般做功率MOSFET都采用外延片。所謂外延片即在原始的低阻襯底(SUBSTRATE)硅片上向外延伸一層高阻層。高阻層用來耐受電壓,低阻襯底作為支撐又不增加很多電阻。對(duì)MOSFET來說,載流子(電子或空穴)在這些區(qū)域是在外界電壓下作漂移(DRIFT)運(yùn)動(dòng),故而相關(guān)的電阻稱為RD。若要求MOSFET的耐壓高,就必須提高高阻層(對(duì)N溝道MOSFET來說,稱N-層)的電阻率,但當(dāng)外延層的電阻率提高時(shí),RD也隨之提高。這也是很少出現(xiàn)一千伏以上的高壓MOSFET的原因。

(1)降低溝道電阻首先我們來看如何降低溝道電阻。前面已經(jīng)提到,當(dāng)前功率MOSFET發(fā)展的一個(gè)重要趨勢(shì)就是把單個(gè)原胞的面積愈做愈小,原胞的密度愈做愈高,其原因就是為了降低溝道電阻。為什么提高原胞的密度可降低溝道電阻呢?從圖一可以看出:HEXFET的電流在柵極下橫向流過溝道。其電阻的大小和通過溝道時(shí)的截面有關(guān)。而這個(gè)截面隨器件內(nèi)原胞周界的增長(zhǎng)而增大。當(dāng)原胞密度增大時(shí),在一定的面積內(nèi),圍繞著所有原胞的總周界長(zhǎng)度也迅速擴(kuò)大,從而使溝道電阻得以下降。

IR公司1995 年發(fā)展的第五代HEXFET,其原胞密度已比第三代大5倍。因此通過同樣電流時(shí)的硅片面積有希望縮小到原來的2/5。第五代的另一個(gè)特點(diǎn)是,其工藝大為簡(jiǎn)化,即從第三代的6塊光刻板減為4塊,這樣器件的制造成本就可能降低。當(dāng)今世界上最流行的仍是IR的第三代和第五代,第三代常用于較高電壓的器件(如 200~600伏),而第五代常用于較低電壓的器件(如30~250伏)。高密度結(jié)構(gòu)在較低電壓器件中顯示更優(yōu)越作用的原因是因?yàn)榈蛪浩骷捏w電阻RD較小,因而降低溝道電阻更易于顯出效果。過去有多年工作經(jīng)驗(yàn)的電力電子工作者,常對(duì)當(dāng)前生產(chǎn)廠熱中于發(fā)展低壓器件不感興趣或不可理解。這主要是電力電子技術(shù)的應(yīng)用面已大大拓寬,一些低壓應(yīng)用已成為新技術(shù)發(fā)展中的關(guān)鍵。最典型的是電腦中電源的需求。正在研究的是1伏甚至到0.5伏的電源,同時(shí)必須迅速通過50 或100安這樣大的電流,這種要求對(duì)半導(dǎo)體器件是十分苛刻的。就像要求一個(gè)非常低壓力的水源,瞬間流出大量的水一樣。

為進(jìn)一步增加原胞密度,也可以采用挖槽工藝。通常稱為TRENCH(溝槽)MOSFET。將溝槽結(jié)構(gòu)作了一個(gè)簡(jiǎn)單圖示。溝槽結(jié)構(gòu)的溝道是縱向的,所以其占有面積比橫向溝道為小。從而可進(jìn)一步增加原胞密度。有趣的是,最早做功率稍大的垂直型縱向MOSFET時(shí),就是從挖槽工藝開始的,當(dāng)初稱為VVMOS,但由于工藝不成熟,因而只有當(dāng)平面型的VDMOS出現(xiàn)后,才有了新一代的功率半導(dǎo)體器件的突破。在半導(dǎo)體器件的發(fā)展過程中,因?yàn)榘雽?dǎo)體工藝的迅速發(fā)展,或是一種新的應(yīng)用要求,使一些過去認(rèn)為不成熟的技術(shù)又重新有了發(fā)展,這種事例是相當(dāng)普遍的。當(dāng)前一統(tǒng)天下的縱向結(jié)構(gòu)功率MOSFET,也有可能吸納橫向結(jié)構(gòu)而為低壓器件注入新的發(fā)展方向。

(2)降低JFET電阻

為降低JFET電阻,很早就采用了一種工藝,即增加所夾溝道中的摻雜濃度,以求減小JFET的溝道電阻。

溝槽式結(jié)構(gòu)也為降低JFET電阻帶來好處。原結(jié)構(gòu)中的JFET在溝槽型結(jié)構(gòu)中已經(jīng)消失。這也就使其RDS(ON)得以進(jìn)一步下降。然而溝槽式的缺點(diǎn)是其工藝成本要比原平面型的結(jié)構(gòu)較高。

(3)降低漂移電阻

上面的討論已涉及到如何降低溝道電阻RCH和JFET電阻RJ。現(xiàn)在剩下的是如何來減小芯片的體電阻RD。上面已經(jīng)提到,當(dāng)要求MOSFET工作于較高電壓時(shí),必需提高硅片的電阻率。在雙極型晶體管中(晶閘管也一樣),有少數(shù)載流子注入基區(qū)來調(diào)節(jié)體內(nèi)電阻,所以硅片電阻率的提高對(duì)內(nèi)阻的增加影響較小。但 MOSFET則不屬于雙極型晶體管,它依賴多數(shù)載流子導(dǎo)電,所以完全是以外延層的電阻率來決定其RD。因而使MOSFET的RDS(ON)與器件耐壓有一個(gè)大概2.4到2.6次方的關(guān)系。即要求器件的耐壓提高時(shí),其RDS(ON)必然有一個(gè)十分迅速的上升。這也是為什么在600伏以上常采用IGBT的原因。IGBT是絕緣柵雙極型晶體管的簡(jiǎn)稱,IGBT雖然結(jié)構(gòu)與MOSFET相似,但卻是一種雙極型器件。它也是采用少數(shù)載流子的注入來降低其體電阻的。

一個(gè)十分聰明的構(gòu)思又為功率MOSFET提供了一條新出路。如果N-溝道MOSFET中的P基區(qū)向體內(nèi)伸出較長(zhǎng)形成一個(gè)P柱。則當(dāng)漏源之間加上電壓時(shí),其電場(chǎng)分布就會(huì)發(fā)生根本的變化。通常PN結(jié)加上電壓時(shí),電位線基本上是平行于PN結(jié)面的。但這種P柱在一定的設(shè)計(jì)下可使電位線幾乎和元件表面平行。就像P柱區(qū)和N-區(qū)已被中和為一片高阻區(qū)一樣。于是就可以采用較低的電阻率去取得器件較高的耐壓。這樣,RDS(ON)就因較低的電阻率而大大下降,和耐壓的關(guān)系也不再遵循前面所提到的2.4到2.6次方的關(guān)系了。這樣一種思路為MOSFET拓寬了往高壓的發(fā)展,今后和IGBT在高壓領(lǐng)域的競(jìng)爭(zhēng)就大為有利了。

通過上面的各種努力,IR公司MOSFET的RDS(ON)正逐年下降,或者說,正在逐季下降。應(yīng)用工作者如何抓住機(jī)會(huì)跟上器件的發(fā)展,及時(shí)把更好性能的器件用上去,就變得十分重要了。

5.2柵電荷QG的降低

MOSFET常常用在頻率較高的場(chǎng)合。開關(guān)損耗在頻率提高時(shí)愈來愈占主要位置。降低柵電荷,可有效降低開關(guān)損耗。

為了降低柵電荷,從減小電容的角度很容易理解在制造上應(yīng)采取的措施。為減小電容,增加絕緣層厚度(在這兒是增加氧化層厚度)當(dāng)然是措施之一。減低電容板一側(cè)的所需電荷(現(xiàn)在是降低溝道區(qū)的攙雜濃度)也是一個(gè)相似的措施。此外,就需要縮小電容板的面積,這也就是要減小柵極面積。縮小原胞面積增加原胞密度從單個(gè)原胞來看,似乎可以縮小多晶層的寬度,但從整體來講,其總的柵極覆蓋面積實(shí)際上是增加的。從這一點(diǎn)來看,增加原胞密度和減小電容有一定的矛盾。

采用了上述措施,IR 產(chǎn)生了第3.5代。也稱為低柵電荷MOSFET。第3.5代的米勒電容下降80%,柵電荷下降40%。當(dāng)然第3.5代還有許多其它措施來降低RDS (ON)(降低了15%),這樣所帶來的好處不僅是開通速度快了,溫升降低了,也帶來了DV/DT能力的提高,柵漏電壓的增高,同時(shí)也降低了驅(qū)動(dòng)電路的費(fèi)用。所以對(duì)應(yīng)用工作者來說,將大家最為熟悉的第三代改換用第3.5代的時(shí)機(jī)已經(jīng)來到。為緩解原胞密度增高后柵面積增大引起柵電荷過分增大的問題,一種折衷的結(jié)構(gòu)也隨之出現(xiàn)。那就是將漏極的原胞結(jié)構(gòu)改為條狀漏極。這時(shí)候可以有同樣窄的柵極(條密度很高)而不至于增加太多柵極面積,所以柵電荷得以減小。