運動控制技術(shù)是制造自動化的關(guān)鍵基礎(chǔ),其水平高低是衡量一個國家工業(yè)現(xiàn)代化的重要標(biāo)志,研究和開發(fā)具有開放式結(jié)構(gòu)的運動控制器是當(dāng)前運動控制領(lǐng)域的一個重要發(fā)展方向。隨著集成電路技術(shù)、微電子技術(shù)、計算機技術(shù)和網(wǎng)絡(luò)技術(shù)的不斷發(fā)展,運動控制器已從以單片機和微處理器作為核心的運動控制器和以專用芯片(ASIC)作為核心處理器的運動控制器,發(fā)展到了基于PC機平臺的以數(shù)字信號處理器(DSP)和現(xiàn)場可編程門陣列(FPGA)作為核心處理器的協(xié)處理架構(gòu)的開放式運動控制器。該控制器將PC機和DSP的信息處理能力與FPGA的外圍擴展功能很好的結(jié)合在一起,具有信息處理能力強、模塊化、開放程度高、運動軌跡控制精確等優(yōu)點。

1 系統(tǒng)概述

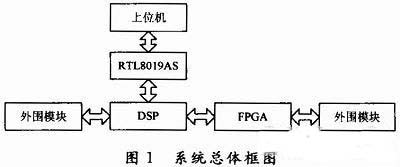

該四軸運動控制器系統(tǒng)以TI公司C2000系列DSP芯片TMS320F2812和alterA公司CycloneⅡ系列FPGA芯片EP2C8F256C6為核心,DSP通過網(wǎng)口接收上位機的控制參數(shù),完成系統(tǒng)位置、速度控制及運動軌跡規(guī)劃;FPGA完成運動控制器的精確插補功能和外圍電路的擴展,系統(tǒng)總體框圖如圖1所示。

運動控制器的主要功能包括:4路模擬電壓輸出,電壓范圍為-10~+10V,分辨率為16b;4路脈沖量信號輸出;4路脈沖方向信號輸出;4路驅(qū)動復(fù)位信號輸出;4路驅(qū)動使能信號輸出;4路差分編碼信號輸入;4路驅(qū)動報警信號輸入;8路正負(fù)限位信號輸入;4路原點信號輸入;16路通用數(shù)字量。I/O。

2 DSP模塊設(shè)計

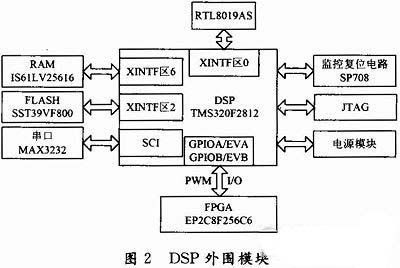

DSP根據(jù)從上位機接收的運動模式和運動參數(shù)實時計算規(guī)劃位置和規(guī)劃速度,生成所需的速度曲線,實時的輸出規(guī)劃位置。TMS320F2812是TI推出的一款專門用于電機控制的32位定點DSP芯片,采用高性能靜態(tài)CMOS技術(shù),主頻高達150MHz(指令周期6.67ns),低功耗,核心電壓為1.8V,I/O電壓3.3V,支持JTAG邊界掃描,128K×16b的片內(nèi)FLASH。有兩個事件管理器(EVA和EVB),它們都是特定的外圍設(shè)備,為多軸運動控制器而設(shè)計的。可通過外部存儲器接口XINTF擴展外部存儲器。DSP外圍模塊設(shè)計如圖2所示。

為增強抗干擾性,DSP通過以太網(wǎng)控制器RTL8019AS與上位機連接,RTL8019AS內(nèi)部含有一個16KB的SDRAM,DSP通過外部存儲器接口對其進行讀寫來接收上位機的命令或向上位機傳送反饋信號。在數(shù)據(jù)處理過程中要占用大量的存儲空間,DSP內(nèi)部僅含有18K×16b的SARAM和128K×16b的FLASH,存儲空間顯得過小,所以通過外部接口擴展了256K×16b RAM和512K×16b FLASH,RAM和FLASH芯片分別選擇IS61LV25616 AL、SST39VF800,它們都具有接口簡單、讀寫速度快等優(yōu)點。SCI模塊用于擴展RS 232串行通信接口,串口芯片使用MAX3232。

運動控制器所需電壓為5V,3.3V,1.8V,1.2V。輸入電壓5V,分別采用穩(wěn)壓芯片LM1085IS3.3,LM1117-1.8將其轉(zhuǎn)換成3.3V和1.8V,由于TMS320F2812的I/O電壓3.3V要先于內(nèi)核電源上電,所以1.8V要由3.3V降壓得到,以確保上電次序。1.2V是FPGA內(nèi)核所需電壓,由穩(wěn)壓芯片LM317S穩(wěn)壓得到,LM317S的輸出電壓范圍為1.2~25V,復(fù)位電路采用SP708低功耗微處理器監(jiān)控器件,此器件有眾多的組件,有效的增強了系統(tǒng)的可靠性及工作效率。

3 FPGA模塊設(shè)計

FPGA用于軸資源的擴展,當(dāng)接收到DSP中的規(guī)劃位置后,在軸資源中對其進行變換處理,輸出到伺服控制器中,伺服控制器將規(guī)劃位置與編碼反饋的計數(shù)位置進行比較,獲得跟隨誤差,并通過伺服控制算法得到實時的控制量,將控制量傳遞給D/A轉(zhuǎn)換器,由D/A轉(zhuǎn)換器轉(zhuǎn)換成控制電壓輸出。

EP2C8F256C6是alterA公司CycloneⅡ系列芯片,其特點為高性能低功耗,內(nèi)核供電電壓為1.2V,8256個邏輯單元(LEs),182個用戶I/O口(項目中使用了157個I/O口),165888b的內(nèi)部RAM,嵌入了18b的乘法器,每個乘法器又可拆成2個9b的乘法器,芯片內(nèi)部含有2個鎖相環(huán)(PLL),8個全局時鐘(Global Clocks)。該芯片所具有的邏輯單元數(shù)、頻率和用戶I/O口等都能很好的滿足設(shè)計需求。FPGA的外圍模塊擴展如圖3所示。

3.1 與DSP接口設(shè)計

DSP芯片的事件管理器(EVA,EVB)用于和FPGA連接,當(dāng)輸出脈沖量控制驅(qū)動器時,DSP使用兩個事件管理器進行PWM波的控制,當(dāng)輸出模擬量時,DSP使用GPIOA/GPIOB向FPGA輸出規(guī)劃位置。

3.2 模擬信號輸出電路設(shè)計

采用D/A轉(zhuǎn)換器AD669進行模擬信號的輸出,AD669具有兩級鎖存,在設(shè)計中,將其四路D/A芯片的第一級鎖存處于透明狀態(tài),第二級鎖存控制信號LDAC連在一起,當(dāng)四路D/A芯片的數(shù)據(jù)預(yù)裝好后,打開第二級鎖存,四路D/A芯片即可同時轉(zhuǎn)換,實現(xiàn)了四軸驅(qū)動的同時控制。

3.3 脈沖信號輸出電路設(shè)計

脈沖輸出電路由FPGA內(nèi)部精插補器完成,精插補器根據(jù)DSP發(fā)送來的粗插補數(shù)據(jù)產(chǎn)生均勻的脈沖輸出,脈沖的輸出有兩種格式:“脈沖+方向”和“正負(fù)脈沖”。由于差分信號對外部電磁等信號有很好的抗干擾性,特別是對共模干擾有很好的抑制作用。所以脈沖經(jīng)過光耦隔離后,再將信號接入差分線驅(qū)動器AM26LS31后輸出,差分線驅(qū)動器AM26LS31的作用是將輸入的單極性方波信號轉(zhuǎn)化為一對極性相反的電機驅(qū)動信號。

3.4 編碼反饋電路設(shè)計

電機編碼信號直接傳入電機驅(qū)動器中,電機驅(qū)動器將三對差分編碼信號A+,A-,B+,B-,N+,N-作為反饋傳給運動控制器。在電機旋轉(zhuǎn)時,所發(fā)出的編碼信號會出現(xiàn)非常多的毛刺,并且經(jīng)過驅(qū)動器大電源的干擾,如果直接接到FPGA中,可能會引起誤判斷,所以先將三對編碼信號經(jīng)過差分芯片AM26LS32轉(zhuǎn)化成單路信號A,B,N后再接入FPGA中。芯片AM26LS32功能是將輸入的一對極性相反的編碼器差分信號轉(zhuǎn)化成單極性的脈沖信號,與AM32LS31正好相反。

3.5 開關(guān)量接口和通用I/O電路設(shè)計

輸出信號包括復(fù)位信號和使能信號,由FPGA產(chǎn)生,經(jīng)光耦隔離后直接輸出;輸入信號包括驅(qū)動報警信號,正負(fù)限位信號和原點信號,這些信號經(jīng)光耦隔離、電平轉(zhuǎn)換后再由FPGA接收,當(dāng)FPGA檢測到這些信號后,確定具體的觸發(fā)信號,做出相應(yīng)的反應(yīng)。另外運動控制器還提供了八路數(shù)字量輸入通道和八路數(shù)字量輸出通道,輸入、輸出通道都經(jīng)光電隔離,以提高抗干擾性。

4 網(wǎng)口模塊設(shè)計

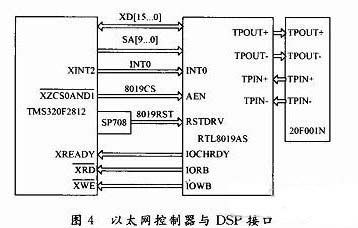

DSP通過以太網(wǎng)控制器RTL8019AS與上位機連接,RTL8019AS在一塊芯片上集成了RTL8019AS內(nèi)核和一個16KB的SDRAM存儲器,兼容RTL8019AS控制軟件和NE20008b或16b傳輸,其接口符合Ethernet2和IEEE802.3標(biāo)準(zhǔn)。RTL8019AS與主機的接口模式有三種模式:跳線模式,PnP模式,RT模式。此運動控制器使用便于DSP應(yīng)用的跳線模式。DSP與RTL8019AS的連接如圖4所示。

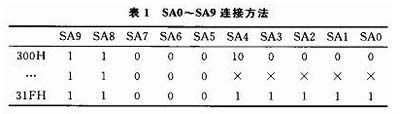

(1)數(shù)據(jù)總線和地址總線。RTL8019AS的數(shù)據(jù)總線和DSP的16位數(shù)據(jù)總線直接相連即可。RTL8019AS片內(nèi)NE2000寄存器組都是通過其映射I/O端口進行訪問,I/O端口共32個,地址偏移量為00H~1FH,把I/O基地址設(shè)為300H,則對應(yīng)的I/O端口尋址范圍為:300H~31FH。只需要10根地址線就可以對I/O端口進行尋址,把SA10~SA19接低電平,SA0~SA9按照表1接法即可。

由表1可以看出,只需要5根地址線就可以尋址32位I/O端口,所以可以直接把SA9,SA8接高電平,SA5~SA7接低電平,SA0~SA4與DSP的低5位地址線XA0~XA4相接。

(2)控制總線。RTL8019AS片選信號AEN使用DSP的擴展片選信號,IORB、IOWB直接與DSP的讀寫控制信號相連,中斷輸出引腳INT0與DSP的XINT2相連,高電平有效的復(fù)位輸入引腳與監(jiān)控電路芯片SP708的RST相連,當(dāng)DSP復(fù)位時,RTL8019AS也復(fù)位。

(3)RTL8019AS與網(wǎng)絡(luò)介質(zhì)接口。RTL8019AS可以使用同軸電纜或雙絞線作為傳輸媒介,將其AUI接口接地或懸空,使用BNC接口。BNC接口方式支持8線雙絞線或同軸電纜。20F001N是雙絞線驅(qū)動器,為耦合隔離變壓器模塊,通過它可以去除因電路數(shù)字特性導(dǎo)致的高次諧波。RTL8019AS與20F001N的連接如圖4所示。其差分輸入信號TPIN+、TPIN-與差分輸出信號TPOUT+、TPOUT-分別與20F001的對應(yīng)引腳相連。

5 結(jié)語

在PC平臺下,充分利用了DSP的數(shù)據(jù)處理能力和FPGA的硬件特性,使系統(tǒng)既能進行復(fù)雜的軌跡規(guī)劃、高速插補,又能保證運動控制器的穩(wěn)定性和精確性,這種運動控制器能應(yīng)用于數(shù)控系統(tǒng),機器人制造等控制領(lǐng)域。