中心議題:

- ADl871" title="ADl871">ADl871型模/數(shù)轉換器" title="模/數(shù)轉換器">模/數(shù)轉換器的應用

解決方案:

- 采用ADl871構成的采樣系統(tǒng)

- 接口的設計

- 時鐘設計時對MCLK 4分頻

1 引言

科學技術的發(fā)展對數(shù)據采集系統(tǒng)的采樣速率" title="采樣速率">采樣速率、分辨率、精度、接口及抗干擾能力等提出越來越高的要求。

AD1871是目前市場上動態(tài)范圍、采樣速率和采樣精度等指標都很突出數(shù)據的一款24位ADC,它的推出為設計高速、高精度數(shù)據采集系統(tǒng)提供了一種較好的解決方案。由于其輸出為串行輸出,當其和MCU直接相連時,會使采樣系統(tǒng)的采樣速率大大降低。

如果MCU的I/O端口的實際最高速率是1MHz(單片機的速率通常是這個數(shù)量級),那么I/O端13傳輸1Bit的最短時間間隔為1μs,當ADl871輸出2路各24Bit時,需要實際串行輸出64Bit,故采樣速率下降為1MHz/64=15.625kHz,這個速率遠遠低于ADl871的96kHz,另外,單片機把64位串行數(shù)據再處理為2個24位的并行數(shù)據時,速度會進一步降低。

為此,筆者采用現(xiàn)場可編程門陣列(FPGA)設計了ADl871和MCU之間的接口,由FPGA完成對ADl871的控制,并將其輸出的串行數(shù)據在FPGA的內部變?yōu)椴⑿袛?shù)據,并行后的數(shù)據以8位或12位為一組發(fā)給MCU。由于FPGA的實際傳輸速率可以滿足和ADl871的傳輸速率要求,故上述“瓶頸”得以解決。

2 接口設計

2.1 時鐘設計

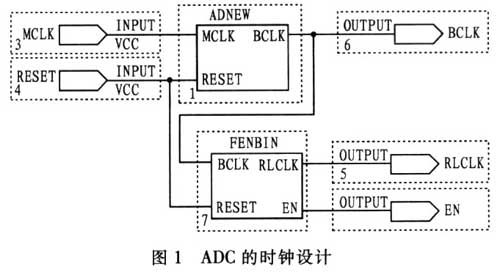

圖1示出A/D轉換器的輸入時鐘設計,MD轉換器工作在從模式下時,需要外部提供RLCLK和BCLK。在主時鐘MCLK的輸入下,通過對MCLK 4分頻得到BCLK的信號,用來作為位數(shù)據提取的信號。RLCLK是通過對BCLK的32分頻得到的,用來區(qū)分左右通道的數(shù)據,同時輸出EN信號作為后續(xù)處理的同步信號。

2.2接口設計

在圖2中,輸入為MCLK(主時鐘)、RESET(啟動信號)和SHIFTIN(A/D輸出數(shù)據),輸出為RL(左右?guī)盘?、BCLK(A/D數(shù)據位時鐘),TXT(并行數(shù)據讀取控制)和SHIFTOUT(并行數(shù)據輸出)。通過時鐘控制輸出BCLK和 RLCLK到AD1871,AD1871傳出數(shù)據SHIFTIN進入SHIFT模塊,SHIFT模塊在正確的位時鐘下讀取SHIFTIN的輸入數(shù)據,并進行串,并轉換,之后輸出8位或12位的數(shù)據。同時輸出TXT并行數(shù)據讀取控制。

2.3 SHIFT模塊程序

Emity shifill is

PORT(BCLK:IN STD_LOGIC;一輸入的BCLK位信號

CR :IN STD_LOGIC;--輸入的使能信號

SHIFTIN:IN STD_LOGIC:--AD輸入的串行信號

RLEN:IN STD_LOGIC;--輸入的RLCLK使能,幀對準信號

TXTS:OUT STD_LOGIC;--8位的組信號輸出控制信號

sddddd:OUT STD_LOGIC_VECTOR (7DOWNTO 0); --8位并行信號輸出);

end shift11:

architecture Behavioral of shift11 is

SIGNAL TEMPDATE:STD_LOGIC_VEC—TOR(8 DOWNTO 0);

SIGNAL TEMPO11:STD_LOGIC_VECTOR(7DOWNTO 0):=“00000000”;

SIGNAL Q:INTEGER RANGE 0 T0 7;

一并行信號計數(shù)8位產生一個脈沖;

SIGNAL Q4:INTEGER RANGE 0 TO 3;

--有用信號選擇,選擇32位中的24位;

筆者用MaxPlus II對以上設計進行仿真后得到圖3所示的時序圖,完全滿足設計要求,從圖3可以看出串行輸入的數(shù)據(shiflin)變成并行的數(shù)據(shiftout) 輸出,在此過程中數(shù)據延時8個周期,每個txts的上升沿提取數(shù)據能保證數(shù)據的正確性。因為從數(shù)據的變動到txts的上升沿有400ns,大于FPGA的數(shù)據建立時間(25ns~50ns),可以保證提取數(shù)據的正確性。

3 小型采樣系統(tǒng)

圖4示出采用ADl871構成的采樣系統(tǒng)結構。整個系統(tǒng)在1個FPGA上實現(xiàn),分為3部分:并轉換模塊;ADC控制和配置;UART通信。

具體的功能是實現(xiàn)ADC的初始化、信號的采集存儲及UART通信。

工作原理是由ADC控制模塊來接收PC的數(shù)據,轉發(fā)控制數(shù)據到ADC,對ADC的工作狀態(tài)進行配置。完成后ADC采樣并儲存在FIFO中,通過控制向單片機傳送數(shù)據。

從仿真結果看,整個系統(tǒng)的工作正常,說明接口設計的正確性和可行性。

4 結束語

由ADl871構成的數(shù)據采集系統(tǒng)具有高分辨率、寬動態(tài)范圍、高信噪比等特點,特別適用于高精度數(shù)據采集系統(tǒng)。∑-△型ADC具有抗干擾能力強、量化噪聲小、分辨率高、線性度好、轉換速度較高、價格合理等優(yōu)點,因此越來越多地受到電子產品用戶及設計人員的重視。解決這類ADC的接口問題在實際設計中具有重大意義。筆者設計的接口使單片機從接收數(shù)據的困境中解脫出來,大大提高了單片機的采樣速率,原來處理一幀數(shù)據需要讀64次,現(xiàn)在只需要6次,在12位輸出的情況下只需要4次,也就是說采用FPGA后單片機的I/O口可以達到1MHz/6=166.66kHz 的采樣速率,大大超過了96kHz的采樣速率,使單片機有時間對數(shù)據進行一些處理。