1.引言

SPI-4.2(System Packet Interface)是 OIF(Optical Internetworking Forum)定義的局部高速總線標(biāo)準(zhǔn),用于 PHY層芯片到鏈路層芯片的 10Gbps信號(hào)傳輸。主要應(yīng)用有 OC-192 ATM、Packet over SONET/SDH(POS)、10Gbps以太網(wǎng)等。

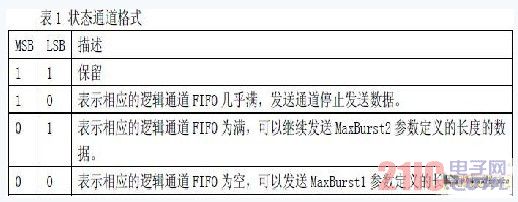

SPI4.2接口分為數(shù)據(jù)通道和狀態(tài)通道。數(shù)據(jù)通道最多分成 256個(gè)邏輯通道,16bit位寬,采用 LVDS信號(hào)電平,按照 cell格式傳送數(shù)據(jù),cell的長(zhǎng)度為 16字節(jié)的整數(shù)倍,可隨意配置,根據(jù)網(wǎng)上流量的分析,一般配置成 128字節(jié)。每個(gè) cell都是以控制字開始的,控制字一共16bit,包含邏輯端口號(hào)、報(bào)文起始標(biāo)志位、報(bào)文結(jié)束標(biāo)志位、控制字交驗(yàn)等信息。狀態(tài)通道傳輸對(duì)端反饋的邏輯通道接收 FIFO的狀態(tài),2bit位寬,LVTTL或者 LVDS信號(hào)電平,一般采用 LVTTL信號(hào)電平。狀態(tài)通道的數(shù)據(jù)結(jié)構(gòu)為 Calendar[0:n],n最大為256,長(zhǎng)度一般與邏輯通道數(shù)對(duì)應(yīng),Calendar[n]表示邏輯通道 n的接收FIFO狀態(tài)。數(shù)據(jù)通道根據(jù)狀態(tài)通道提供的信息控制數(shù)據(jù)的發(fā)送過程。狀態(tài)通道有四種狀態(tài)信息,如表 1所示:

在實(shí)際的系統(tǒng)設(shè)計(jì)中,商用芯片不一定能夠滿足需要,因此需要使用 FPGA(Field Programmable Gate Array)。本設(shè)計(jì)采用 Altera的 Stratix II系列 FPGA和 RMI公司的多核處理器 XLR732,Intel公司的網(wǎng)絡(luò)處理器 2805實(shí)現(xiàn) SPI4.2接口。

2.2805簡(jiǎn)介 2805是 Intel推出的高端 NP(Network Prosser),能夠處理 10Gbps線速轉(zhuǎn)發(fā)的以太網(wǎng)、POS、ATM等數(shù)據(jù)流量,能夠?qū)崿F(xiàn)分類、NAT、ACL、多播、流量管理等功能。 2805內(nèi)部集成一個(gè)32-bit、RISC內(nèi)核、高性能的 XScale處理器,用于系統(tǒng)的配置管理和路由表項(xiàng)的維護(hù),最高工作主頻750MHz;16個(gè)可編程的、有 8K代碼空間的微引擎,每個(gè)微引擎含有多個(gè)硬件線程,用來處理通信系統(tǒng)中的數(shù)據(jù)轉(zhuǎn)發(fā),最高工作主頻 1.5GHz。外部集成了 PCI接口,可以工作在 64bit/66MHz模式;SPI4.2接口,工作頻率為 311MHz~500MHz;3個(gè)LA-1接口,工作頻率為250MHz;4個(gè) RDRAM接口,工作頻率為 800MHz~1200MHz。

3.FPGA和 2805之間的 SPI4.2接口電路設(shè)計(jì)

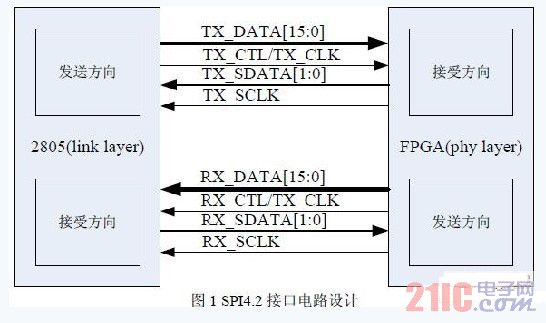

圖 1描述了 FPGA和 2805之間的 SPI4.2接口的硬件連接框圖,信號(hào)定義以 2805為參考點(diǎn)。其中 TX_DATA[15:0] 、TX_CTL、TX_CLK和 RX_DATA[15:0] 、RX_CTL、RX_CLK是 LVDS信號(hào)電平,工作在 350MHz;TX_SDATA[1:0] 、TX_SCLK和 RX_SDATA[15:0] 、 RX_SCLK是 LVTTL信號(hào)電平,工作在 87.5MHz,四分之一于數(shù)據(jù)通道時(shí)鐘頻率。

具體信號(hào)定義如下所示:

TX_DATA[15:0]:發(fā)送數(shù)據(jù), 16bit位寬, burst方式傳輸數(shù)據(jù), DDR工作模式(時(shí)鐘上升沿和下降沿都采樣);

TX_CTL:傳輸控制信號(hào),高電平表示 TX_DATA[15:0]傳輸?shù)氖强刂菩畔ⅲ碗娖奖硎?TX_DATA[15:0]傳輸?shù)氖菙?shù)據(jù);

TX_CLK:發(fā)送時(shí)鐘,隨路,是發(fā)送數(shù)據(jù)的參考時(shí)鐘。

接受方向的信號(hào)定義與發(fā)送方向的信號(hào)定義完全相同,但是方向相反。

4.FPGA的 SPI4.2接口模塊設(shè)計(jì)

Stratix II器件具有 152個(gè)接收器和 156個(gè)發(fā)送器通道,支持源同步信號(hào)進(jìn)行高達(dá) 1 Gbps的數(shù)據(jù)傳送。它的內(nèi)部含有 DPA電路,能夠不斷地將輸入數(shù)據(jù)和采樣時(shí)鐘對(duì)齊,消除了時(shí)鐘至通道和通道至通道偏移要求。它還集成了豐富的存儲(chǔ)器資源、先進(jìn)的鎖相環(huán)( PLL)技術(shù)和雙數(shù)據(jù)率( DDR)I/O等特性,結(jié)合先進(jìn)的差分 I/O能力,使其滿足 SPI4.2規(guī)范的物理信號(hào)定義。

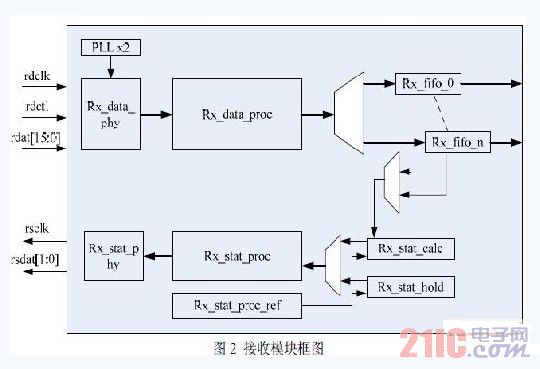

圖 2為 FPGA的接收通道邏輯框圖,上半部分是數(shù)據(jù)通道,下半部分是狀態(tài)通道。由于 SPI4.2接口的數(shù)據(jù)傳輸是 DDR模式的,rdclk經(jīng)過 FPGA內(nèi)部的 PLL模塊做倍頻處理,然后送給 Rx_data_phy模塊,該模塊根據(jù)時(shí)鐘采樣 rdat [15:0]上的數(shù)據(jù)。Rx_data_proc模塊將接收的數(shù)據(jù)按照 cell頭中的邏輯端口號(hào),分別放入不同的 Rx_fifo中。一個(gè) Rx_fifo對(duì)應(yīng)一個(gè)邏輯通道,每個(gè) Rx_fifo都會(huì)生成一個(gè)狀態(tài)信號(hào),標(biāo)示其“空”狀態(tài)或者“滿”狀態(tài), Rx_stat_calc模塊根據(jù)各個(gè) Rx_fifo的狀態(tài)信號(hào)生成 Calendar信息,由狀態(tài)通路發(fā)送出去,用來流控 2805的發(fā)送過程。Calendar也可以由軟件設(shè)置,通過 Rx_stat_proc_ref下發(fā)給 Rx_stat_calc。

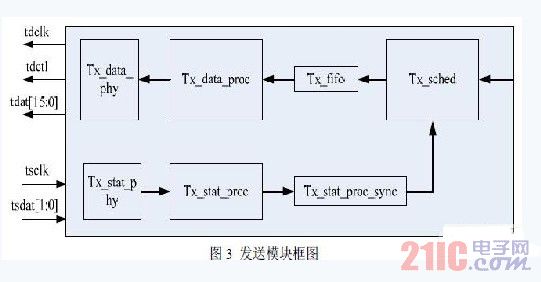

發(fā)送模塊與接收模塊不同,如圖 3所示,發(fā)送模塊的 Tx_fifo只有一個(gè),即所有的邏輯通道公用一個(gè)發(fā)送緩存區(qū)。這主要是由于 FPGA內(nèi)部的布線資源和 RAM資源有限,同時(shí)這種發(fā)送端共享 FIFO、接收端分通道 FIFO模式不影響使用,能夠?qū)崿F(xiàn)分端口的反壓。

發(fā)送端通過 Tx_stat_phy模塊接收 Calender信息,經(jīng)過 Tx_stat_proc模塊和Tx_stat_proc_sync模塊處理,送給 Tx_sched調(diào)度模塊,Tx_sched解析出各個(gè)邏輯通道的反壓情況,然后將各個(gè)通道的數(shù)據(jù)發(fā)送到 Tx_fifo中,然后經(jīng)過 Tx_data_proc模塊和Tx_data_phy模塊發(fā)送出去。

5.結(jié)果 本設(shè)計(jì)在 ALTEra的 Stratix II系列FPGA,EPM2S90上得到驗(yàn)證,與 Intel的 2805配合共同完成某通信設(shè)備的高速轉(zhuǎn)發(fā)單板的設(shè)計(jì)。

6.結(jié)束語(yǔ)

本文介紹了 SPI4.2接口在可編程邏輯器件 FPGA上的實(shí)現(xiàn)方法,并通過實(shí)際電路驗(yàn)證FPGA與 IPX2805之間通過 SPI4.2接口互通的功能。由于商業(yè)芯片的限制,有時(shí)只有 FPGA才能滿足系統(tǒng)設(shè)計(jì)的要求。相對(duì)于開發(fā)ASIC,使用 FPGA使整個(gè)設(shè)計(jì)電路簡(jiǎn)單、靈活、成本低、方便調(diào)試和修改, 大大縮短開發(fā)周期。