1 引言

隨著半導(dǎo)體工藝的發(fā)展,片上系統(tǒng)SOC已成為當(dāng)今一種主流技術(shù)。基于IP復(fù)用的SOC設(shè)計(jì)是通過(guò)用戶自定義邏輯(UDL)和連線將IP核整合為一個(gè)系統(tǒng),提高了設(shè)計(jì)效率,加快了設(shè)計(jì)過(guò)程,縮短了產(chǎn)品上市時(shí)間。但是隨著設(shè)計(jì)規(guī)模的增大,集成密度的提高,IP引腳的增多,IP的植入深度加大必然使得測(cè)試驗(yàn)證工作繁重。據(jù)統(tǒng)計(jì),在SOC設(shè)計(jì)中,各種內(nèi)核的測(cè)試驗(yàn)證工作所用的時(shí)間占整個(gè)設(shè)計(jì)過(guò)程的60%~80%,SOC及IP核的測(cè)試驗(yàn)證已成為SOC技術(shù)發(fā)展的瓶頸。如何在最短的時(shí)間內(nèi)高效迅速地通過(guò)IP核驗(yàn)證與測(cè)試.并把其集成在SOC中成為業(yè)界關(guān)注的焦點(diǎn)和研究領(lǐng)域急待突破與實(shí)現(xiàn)的方向。

基于IP核復(fù)用的SOC,其IP核類型和來(lái)源都不相同,即使已驗(yàn)證好的IP核在集成時(shí)也不能確保不出差錯(cuò)。IP核被集成到SOC后,其輸入輸出端口也嵌入到SOC,原本可測(cè)的端口失去了原有的可控性和可觀測(cè)性,變得不可測(cè)。

因此人們一直尋求有效的測(cè)試驗(yàn)證技術(shù)。本文給出了基于內(nèi)建自測(cè)試方法(BIST),在設(shè)計(jì)編譯碼器IP核的同時(shí),考慮其測(cè)試外殼設(shè)計(jì),以期提高IP核可測(cè)性。

2測(cè)試結(jié)構(gòu)

所謂測(cè)試,就是在被測(cè)電路的輸入引腳施加相應(yīng)的激勵(lì)信號(hào),然后檢測(cè)輸出引腳的響應(yīng),并將檢測(cè)的輸出引腳的響應(yīng)與期望引腳的響應(yīng)進(jìn)行比較以判斷電路是否存在故障的過(guò)程。

IP核測(cè)試的目的在于檢測(cè)IP核是否存在功能和時(shí)序錯(cuò)誤,從而對(duì)IP核進(jìn)行修改,提高產(chǎn)品的可靠性。一般采用訪問(wèn)、隔離、控制的手段對(duì)IP核的輸入端施加激勵(lì)來(lái)得到響應(yīng)與期望的響應(yīng)進(jìn)行比較。嵌入式IP核的測(cè)試結(jié)構(gòu)如圖1所示。

測(cè)試激勵(lì)源為嵌入式IP核生成測(cè)試所需的激勵(lì)。響應(yīng)分析器對(duì)所得到的響應(yīng)進(jìn)行分析,如果相同則表明沒(méi)有故障,不同則表明存在故障。測(cè)試訪問(wèn)機(jī)制是 SOC傳送數(shù)據(jù)的一種手段,它將測(cè)試激勵(lì)傳送到IP核的輸入端口并將測(cè)試響應(yīng)從IP核的輸出端口傳送到響應(yīng)分析器。測(cè)試外殼是IP核同訪問(wèn)機(jī)制及器件其他邏輯之間的接口;測(cè)試外殼以實(shí)現(xiàn)片上核與核之間的測(cè)試隔離,也可以為IP核提供了測(cè)試數(shù)據(jù)傳送通道。

3內(nèi)建自測(cè)試原理

內(nèi)建自測(cè)試是可測(cè)性設(shè)計(jì)的一種重要方法。其基本思想是讓電路自己生成測(cè)試向量,而非通過(guò)外部施加測(cè)試向量,并且依靠自身判斷所得到的結(jié)果是否正確。內(nèi)建自測(cè)試原理圖如圖2所示。

其中測(cè)試外殼(wrapper)在IP核的設(shè)計(jì)之中就予以考慮。通過(guò)測(cè)試外殼外部可以控制BIST和正常模式的切換。測(cè)試外殼內(nèi)部多采用邊界掃描模塊、移位寄存器或多路訪問(wèn)器等,它起到訪問(wèn)、隔離、控制的作用,可提高IP核的可測(cè)性。然而加入測(cè)試外殼會(huì)使IP核的面積開(kāi)銷增大,因此必須在IP核的可測(cè)性和面積之間進(jìn)行權(quán)衡。

4 內(nèi)建自測(cè)試的實(shí)現(xiàn)

可控性指驅(qū)動(dòng)一個(gè)節(jié)點(diǎn)為邏輯狀態(tài)0或1的難易程度;可觀測(cè)性指從外部端口觀察內(nèi)部節(jié)點(diǎn)故障的難易程度;可測(cè)性就是指在整個(gè)電路全部節(jié)點(diǎn)的可控性和可觀測(cè)性。很顯然,高可測(cè)性比較容易產(chǎn)生測(cè)試向量并且測(cè)試效果良好。

為了提高IP核的可測(cè)性,在IP核的設(shè)計(jì)中就考慮了設(shè)計(jì)特定電路方便測(cè)試。以BIST實(shí)現(xiàn)IP核的測(cè)試,一般具有如下優(yōu)勢(shì):簡(jiǎn)化測(cè)試接口;改善測(cè)試質(zhì)量;降低測(cè)試成本;提高測(cè)試可靠性。

基于BIST的編譯碼器IP核測(cè)試實(shí)現(xiàn)框圖如圖3所示。

通過(guò)測(cè)試外殼控制輸入/輸出寄存器將編譯碼器隔離使它們互不影響,正常狀態(tài)和測(cè)試狀態(tài)能夠切換,提高了IP核的可測(cè)性。具體的實(shí)現(xiàn)過(guò)程如下:

(1)正常狀態(tài)下原始碼輸入編碼器,由其輸出的碼再進(jìn)入譯碼器又轉(zhuǎn)換為原始碼;

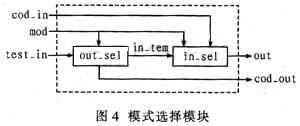

(2)測(cè)試狀態(tài)下測(cè)試外殼的測(cè)試向量輸入編碼器,由其輸出的碼直接進(jìn)入譯碼器,由譯碼器輸出的碼為測(cè)試響應(yīng)輸出,使其與期望值比較;圖3中的模式選擇模塊的邏輯結(jié)構(gòu)如圖4所示。

圖4中mod為模式選擇控制端,置0為正常狀態(tài)。當(dāng)rood為1時(shí),out_sel輸入測(cè)試向量,再由in_tem輸出,進(jìn)入in_sel;當(dāng)mod 為0時(shí),cod_out輸出片外,從而實(shí)現(xiàn)了正常狀態(tài)和測(cè)試狀態(tài)的切換。可以用硬件描述語(yǔ)言編寫(xiě)此邏輯電路。用VHDL描述如下:

此模式選擇模塊實(shí)現(xiàn)狀態(tài)之間的切換,電路簡(jiǎn)單,易于實(shí)現(xiàn)。

5 結(jié)束語(yǔ)

BIST為嵌入式內(nèi)核的測(cè)試提供了一個(gè)可解決的方案,其測(cè)試效果明顯,故障覆蓋率較高,實(shí)現(xiàn)簡(jiǎn)單。通過(guò)加入測(cè)試外殼可以實(shí)現(xiàn)對(duì)IP核的訪問(wèn)、隔離、控制,有效地提高了IP核的可測(cè)性。但是采用BIST會(huì)使電路面積增加額外開(kāi)銷,必須在IP核的可測(cè)性和面積之間進(jìn)行權(quán)衡。