效率下降是阻礙GaN基LED在高電流密度這一重要的新興應(yīng)用領(lǐng)域大施拳腳的主要原因。但RPI的研究人員表示,通過采用極性匹配的外延結(jié)構(gòu)可以克服這一缺點(diǎn)。

LED制造商們目前非常關(guān)注一些新的市場(chǎng),例如汽車前燈、大屏幕顯示和普通照明。從某種程度上說,降低價(jià)格能幫助LED打入這些領(lǐng)域,但僅僅如此還不夠。LED的芯片還需要在大驅(qū)動(dòng)電流下也能實(shí)現(xiàn)高功效。這也意味著需要解決功率下降這一廣受關(guān)注的問題。

通過比較電和光激發(fā)LED的輸出情況,可以幫助RPI的相關(guān)研究人員研究GaN基器件功率下降的原因。

功率下降具體來說是指藍(lán)光、綠光和白光LED在電流增大時(shí)效率反而下降的現(xiàn)象。GaN基LED通常僅在電流密度10A cm-2時(shí)效率達(dá)到峰值,電流密度為100A cm-2時(shí)效率降為峰值的一半。這引起了大家的關(guān)注,當(dāng)今的高亮度芯片都需要在比10A cm-2大得多的電流密度下高效地工作。

攻克這一難題顯然非常重要,而且它已經(jīng)吸引了全球工業(yè)界和學(xué)術(shù)界大批研究人員的興趣,其中也包括我們位于紐約州特洛伊市倫斯勒理工學(xué)院的研究團(tuán)隊(duì),我們?cè)谶^去的幾年里一直在探索效率下降這一問題的根源。我們相信我們能找到癥結(jié)所在,并通過完全不同的LED設(shè)計(jì)克服這一問題。

我們與位于新墨西哥州Sandia國家實(shí)驗(yàn)室的Mary Crawford研究小組合作,一起研究功率下降問題的成因。我們關(guān)注位錯(cuò)密度對(duì)于LED效率的影響,發(fā)現(xiàn)位錯(cuò)會(huì)降低低電流密度時(shí)的效率,但并不影響高電流密度下的效率降低問題。

在低電流密度時(shí),載流子通常在一個(gè)陷阱輔助的過程(即SRH復(fù)合)中損失掉了,而且會(huì)隨著位錯(cuò)密度的增加變得更加嚴(yán)重。通過增強(qiáng)自發(fā)輻射,加大電流密度起初會(huì)提高效率,但隨著電流的進(jìn)一步增加,另一個(gè)與之抗衡的載流子損耗機(jī)制會(huì)引發(fā)效率的下降。

漏電的LED

我們還與韓國三星電機(jī)公司合作。這一努力終于讓我們找到了效率下降的原因——由于量子勢(shì)阱層、量子勢(shì)壘層和電子阻擋層之間的極性失配導(dǎo)致的有源層電子泄漏。

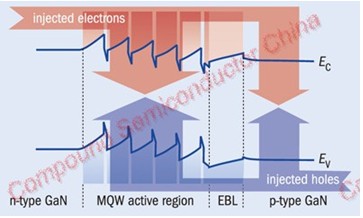

我們的解釋能說明為什么高電流密度時(shí)效率下降的主要原因——當(dāng)提高驅(qū)動(dòng)電壓時(shí),會(huì)導(dǎo)致更多注入的電子逃出有源層,抵達(dá)LED的p型區(qū),從而與p電極處的空穴進(jìn)行非輻射復(fù)合(圖2)。

通過比較LED器件在電偏壓和光激發(fā)時(shí)的光輸出(詳見“探索LED的結(jié)構(gòu)”),該理論已通過實(shí)驗(yàn)得到了驗(yàn)證。我們?cè)谑褂脭?shù)值模擬工具將載流子泄漏與極性失配聯(lián)系起來之前,就曾表明在量子阱外也有復(fù)合機(jī)制發(fā)生。

界面問題

我們的精力主要集中于在GaN傳統(tǒng)的晶面—c面上生長(zhǎng)LED。這些器件通常有很強(qiáng)的內(nèi)建電場(chǎng),在界面處會(huì)產(chǎn)生相當(dāng)強(qiáng)的表面電荷(詳見“感受內(nèi)部的力”)。

LED芯片" height="280" src="http://files.chinaaet.com/images/20111101/92a14182-0e2e-41bb-9541-adf81d0468e5.jpg" width="366" />

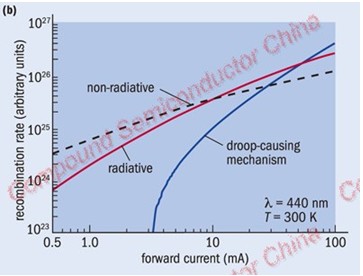

圖1a. 對(duì)面積為1mm×1mm的傳統(tǒng)GaInN LED芯片進(jìn)行測(cè)量,揭示了在驅(qū)動(dòng)電流大于10mA時(shí)輸出效率會(huì)降低。如果能完全避免引起效率下降的機(jī)制,LED芯片的效率則會(huì)隨著電流的增加而不斷增加。

圖1b.非輻射機(jī)制在低驅(qū)動(dòng)電流時(shí)占主導(dǎo)地位,隨著電流增加讓位于輻射復(fù)合,之后效率反而下降。

界面表面電荷會(huì)從兩個(gè)方面阻礙LED的性能。它們會(huì)提高電子注入多量子阱區(qū)的勢(shì)壘,同時(shí)降低來自量子阱和電流阻擋層上電子泄漏的勢(shì)壘。

我們的模擬支持了這一假設(shè),表面電荷通過電子的泄漏降低LED的性能,這也說明減少表面電荷可以緩解載流子的損失。計(jì)算同時(shí)表明缺乏對(duì)p型結(jié)構(gòu)的重?fù)诫s會(huì)加劇效率的下降,尤其是在電子阻擋層。

眾所周知,與雙極結(jié)型晶體管的基極相比,發(fā)射極的重?fù)诫s能阻止少數(shù)載流子注入發(fā)射極。而在LED中,GaN和AlGaN層p型摻雜濃度低,阻礙了空穴(p型區(qū)中空穴為多數(shù)載流子)注入有源區(qū)——這反過來加劇了電子的泄漏。

我們對(duì)電子泄漏造成LED效率下降的解釋還并未得到廣泛接受;事實(shí)上,還有研究者提出了幾種不同的機(jī)制。其中以Philips Lumileds研究人員提出的俄歇復(fù)合理論(Shen et al. 2007)為主流。

在c面GaInN/GaN雙異質(zhì)結(jié)上進(jìn)行了若干光致發(fā)光的試驗(yàn),觀察到高光激發(fā)密度時(shí)效率亦出現(xiàn)了下降。使用速率模型分析使得他們將俄歇復(fù)合當(dāng)作是多量子阱LED效率降低的原因。

為此他們引入了有效復(fù)合厚度的概念,在設(shè)計(jì)雙異質(zhì)結(jié)時(shí)選定的物理厚度更小,因?yàn)榱孔于逯须娮雍涂昭ㄝ^小的重疊。

將該復(fù)合厚度代入速率方程,得出量子阱在有電場(chǎng)時(shí)的自發(fā)輻射速率比無電場(chǎng)時(shí)的更高。但這與GaN量子阱中電場(chǎng)減弱自發(fā)輻射的事實(shí)相反。因此,我們感覺Lumileds高估了多量子阱LED中俄歇復(fù)合在大電流密度時(shí)的重要性。

布丁好不好吃,當(dāng)然嘗過了才知道。最后將我們的模擬結(jié)果付諸實(shí)施,生長(zhǎng)帶有AlGaInN勢(shì)壘層的LED。用AlGaInN層替代傳統(tǒng)的GaN勢(shì)壘層和AlGaN電子阻擋層,使得我們能自由的調(diào)節(jié)帶隙寬度和極性,并最終減少極性失配和有源區(qū)界面間的表層電荷。

圖2. RPI的研究人員認(rèn)為,電子逃逸是造成LED效率下降的主要原因。這些逃出的載流子與p型GaN區(qū)或p電極處的空穴進(jìn)行非輻射復(fù)合。

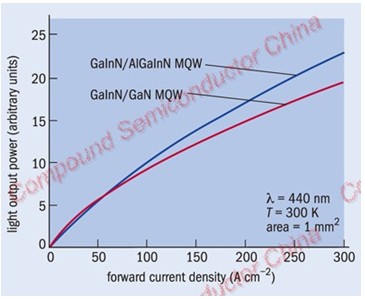

圖3.具有量子勢(shì)阱和勢(shì)壘極性匹配的LED通過減少電子泄漏,在大驅(qū)動(dòng)電流下仍能表現(xiàn)出優(yōu)異的性能。

對(duì)于量子勢(shì)壘,我們將生長(zhǎng)一種與GaN同樣帶隙寬度的四元化合物,并且能與典型量子阱的極性相匹配。這是一項(xiàng)十分艱巨的任務(wù),因?yàn)樯L(zhǎng)高銦組分和高鋁組分的AlGaInN層是非常困難的。但通過減少極性的不平衡,能顯著地提高器件的性能。這也同樣適用于電子阻擋層。

我們的模擬顯示,對(duì)極性匹配做一下調(diào)整就能獲得幾乎所有的好處,而使用勢(shì)壘和勢(shì)阱只能減少一半的極性失配。關(guān)鍵點(diǎn)是將勢(shì)壘的帶隙寬度略微減小,就能在有源區(qū)內(nèi)形成附加的載流子約束。

提高能效

這些調(diào)整已經(jīng)帶來一些令人鼓舞的結(jié)果。由于減緩了效率的下降,在大電流時(shí)光輸出提高了20%(圖3)。由于降低了載流子注入量子阱區(qū)的勢(shì)壘的高度,正向電壓也相應(yīng)的降低了。減少量子阱區(qū)表面電荷的另一個(gè)好處是將總能效提高25%。調(diào)整還帶來其它好處,由于量子阱內(nèi)的電場(chǎng)強(qiáng)度更低,減少了波長(zhǎng)隨電流變化而產(chǎn)生的漂移。

很明顯,人們對(duì)效率下降問題的興趣在不斷增加,這本身對(duì)LED的發(fā)展有益。我們加深了對(duì)它的了解,現(xiàn)有的設(shè)計(jì)看上去能解決這個(gè)問題。具有上述特性的商業(yè)器件就應(yīng)該積極籌備開拓新的市場(chǎng),直指終極目標(biāo)——替代通用照明燈泡。

探索LED的結(jié)構(gòu)

通過比較光激發(fā)和電偏壓時(shí)光的輸出,倫斯勒理工學(xué)院的研究人員研究GaInN藍(lán)光LED中效率下降的問題。上述比較是以電子和空穴的產(chǎn)生速率是相同的為前提,結(jié)果顯示效率下降是由于載流子輸運(yùn)引起的。

在穩(wěn)態(tài)光激發(fā)的條件下,不應(yīng)該存在例外的逃逸電子或空穴。如果發(fā)生了,就會(huì)損失一種載流子——這意味著在量子阱內(nèi)形成了電場(chǎng)分布,產(chǎn)生額外的載流子泄漏。電子或空穴自發(fā)的逃逸也不太可能,因?yàn)榭昭ū粐?yán)格的約束在勢(shì)阱內(nèi)。

無論如何,部分載流子確實(shí)從勢(shì)阱中逃逸出來了。使用405nm激光轟擊這一結(jié)構(gòu),會(huì)產(chǎn)生非零的開路電壓。這是因?yàn)槠骷恼蚱秒妷盒枰聪螂娏鱽硌a(bǔ)償。凈電流仍為零,這是任何一個(gè)沒有接入外部電路的器件都必須遵守的。

正向偏置改變了LED的載流子輸運(yùn)。空穴和電子對(duì)量子阱的注入和逃逸速率會(huì)發(fā)生變化,往往會(huì)導(dǎo)致電子從勢(shì)阱中泄漏出去。這需要LED在光激發(fā)和電偏置兩種情況下不同的光輸出效率來證明。RPI進(jìn)行的測(cè)量證實(shí)了這一點(diǎn)。在電泵浦的器件中觀察到了效率的下降,但在光激發(fā)的情況下卻沒有。這意味著某種形式的載流子復(fù)合機(jī)制在量子阱外的區(qū)域發(fā)生,造成了效率的下降。

感受內(nèi)部的力

GaN具有纖鋅礦晶體結(jié)構(gòu),并在c晶向上存在極化電場(chǎng)。當(dāng)LED生長(zhǎng)在這個(gè)晶向上時(shí),由于各相鄰層間在自發(fā)極化和應(yīng)變誘發(fā)的壓電極化兩方面存在差異,會(huì)在界面間產(chǎn)生較大的表面電荷。通過減少有源區(qū)的電子束縛以及增加有源區(qū)的電子泄漏,這些電荷會(huì)降低LED的效率。

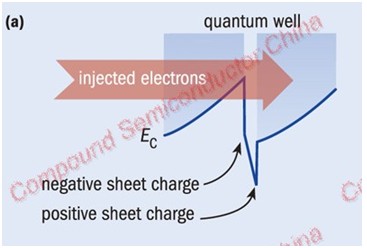

在傳統(tǒng)的藍(lán)光LED中,GaN勢(shì)壘圍繞在GaInN量子阱的兩側(cè),勢(shì)阱的n型區(qū)一側(cè)表面電荷為負(fù)。這些電荷會(huì)排斥電子,并阻礙電子注入。勢(shì)阱的p型區(qū)一側(cè)表面電荷為正,會(huì)吸收電子,增加電子逃逸的可能性(圖a)。

AlGaN電子阻擋層具有相反的效果。它們會(huì)在n型區(qū)一側(cè)產(chǎn)生正電荷,使得電子更容易跨越勢(shì)壘(圖b)。通過提高Al組分來增加電子阻擋層的帶隙寬度并不是一個(gè)很好的解決辦法,原因是表面電荷也會(huì)同時(shí)增加。

發(fā)光效果取決于接觸面

一個(gè)美國團(tuán)隊(duì)將光致發(fā)光強(qiáng)度(PLI)作為電容-電壓(CV)光譜分析法的輔助技術(shù),用以決定III-V族材料與電介質(zhì)之間的界面質(zhì)量。

這些界面嚴(yán)重影響著III-V族MOSFET的性能,作為一種可能拓展摩爾定律的器件,了解它的性能極其重要。CV光譜分析法因其復(fù)雜性一般廣泛用于測(cè)量界面態(tài)密度。

Matthias Passlack曾是前任飛思卡爾在德研究人員,現(xiàn)在正與英國格拉斯哥大學(xué)展開合作。他表示,“很不幸,CV或許被普遍誤解為非硅半導(dǎo)體的相關(guān)技術(shù)。相反,PLI數(shù)字通譯更加直截了當(dāng)一些”,這是因?yàn)榧す饧ぐl(fā)是測(cè)量過程中唯一的可變量。

利用PLI測(cè)量法得到了大量有關(guān)界面態(tài)密度的實(shí)驗(yàn)數(shù)據(jù)。很顯然,這種分析界面質(zhì)量的方法并不新鮮。早在上個(gè)世紀(jì)90年代日本北海道大學(xué)的Hasegawa小組就用該項(xiàng)技術(shù)做過實(shí)驗(yàn);而Passlack也于1994-1995年間在貝爾實(shí)驗(yàn)室建立了一些初步的PLI,并于1996-1997年間在摩托羅拉構(gòu)建了當(dāng)前的器件結(jié)構(gòu)。

Passlack最近發(fā)表的論文對(duì)一門更為復(fù)雜的學(xué)科略有陳述,里面對(duì)基于GaAs的22種材料展開了研究,包括GdGaO、In2O3和Ga2O3電介質(zhì);其中Ga2O3是唯一適合用作器件級(jí)界面的電介質(zhì)。Passlack想用PLI來分析InGaAs MOSFET,并為格拉斯哥大學(xué)的Iain Thayne小組提供幫助,為他們建立一個(gè)能實(shí)現(xiàn)此項(xiàng)測(cè)量的實(shí)驗(yàn)裝置。