引言

鎖相環(huán)(PLL: Phase-locked loops)是一種利用反饋控制原理實現(xiàn)的頻率及相位的同步技術(shù),其作用是將電路輸出的時鐘與其外部的參考時鐘保持同步。隨著集成電路加工中功能器件的尺寸縮小,器件電源電壓也呈下降趨勢,包括PLL和其它混合信號功能所用的電源。然而,PLL的關(guān)鍵元件——“壓控振蕩器”(VCO)的實用技術(shù)要求并未隨之大幅降低。給當(dāng)今的PLL或RF系統(tǒng)設(shè)計師提出了挑戰(zhàn):低壓PLL IC如何與高壓VCO實現(xiàn)接口。電平轉(zhuǎn)換接口通常利用有源濾波電路來實施,這將在下文討論。

本文將分析說明PLL的基本原理,考察采用高壓VCO的PLL設(shè)計的當(dāng)前技術(shù)水平,討論典型架構(gòu)的利弊,并介紹高壓VCO的一些替代方案。

1 PLL基本原理

鎖相環(huán)(圖1)是一個反饋系統(tǒng),其中相位比較器或鑒相器驅(qū)動反饋環(huán)路中的VCO,使振蕩器頻率(或相位)精確跟蹤所施加的參考頻率。通常需要用濾波電路,對正/負(fù)誤差信號求積分并使之平坦,以及提高環(huán)路穩(wěn)定性。反饋路徑中常包含分頻器,使輸出頻率(VCO的范圍內(nèi))為參考頻率的倍數(shù)。分頻器的頻率倍數(shù)N可以是整數(shù),也可以是小數(shù),PLL相應(yīng)地稱為“整數(shù)N分頻PLL”或“小數(shù)N分頻PLL”。

圖1. 基本鎖相環(huán)

PLL是負(fù)反饋控制環(huán)路,因此達(dá)到均衡時,頻率誤差信號必須為零,以便在VCO輸出端產(chǎn)生精確且穩(wěn)定的頻率N × FREF。

PLL有多種實施方法,根據(jù)所需頻率范圍、噪聲和雜散性能以及物理尺寸,可以采用全數(shù)字式、全模擬式或混合電路。目前,高頻(或RF)PLL的常用架構(gòu)既含有全數(shù)字式模塊,如反饋分頻器和鑒相器等,也含有高精度模擬電路,如電荷泵和VCO等。

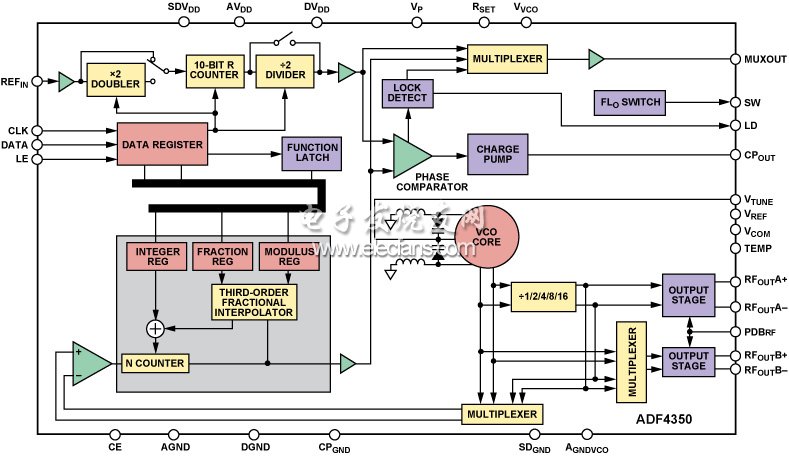

圖2顯示了當(dāng)前器件的高度集成電路示例,這是集成VCO的小數(shù)N分頻PLL IC ADF4350寬帶頻率合成器的框圖,其輸出頻率范圍為137.5 MHz至4400 MHz。

圖2. ADF4350 PLL頻率合成器框圖

限制PLL性能的主要特性有相位噪聲、雜散頻率和鎖定時間。

相位噪聲:相當(dāng)于時域中的抖動,相位噪聲是振蕩器或PLL噪聲在頻域中的表現(xiàn)。。

雜散:雜散頻率由電荷泵定期更新VCO調(diào)諧電壓而引起,并以與載波相差PFD頻率的偏移頻率出現(xiàn)。

鎖定時間:從一個頻率變?yōu)榱硪粋€頻率或響應(yīng)瞬時偏移時,PLL的相位或頻率返回鎖定范圍所需的時間。

2 為什么VCO仍然用高壓?

高性能VCO是最后幾種不為硅集成潮流所動的電子器件之一。僅幾年前,手機(jī)所用的VCO才完全集成到手機(jī)無線電芯片組中。但是,在蜂窩基站、微波點(diǎn)對點(diǎn)系統(tǒng)、軍用和航空航天產(chǎn)品以及其它高性能應(yīng)用中,基于硅的VCO則能力有限,仍然需要采用分立方式來實施VCO。原因如下:

大多數(shù)商用分立VCO采用容值可變的變?nèi)荻O管,作為LC振蕩電路的可調(diào)諧元件。改變二極管的電壓會改變其電容,從而改變振蕩電路的諧振頻率。

變?nèi)荻O管的任何電壓噪聲都會被VCO增益KV(用MHz/V表示)放大,并轉(zhuǎn)換為相位噪聲。要使VCO相位噪聲保持最小,KV必須盡可能小,但為了實現(xiàn)合理的寬調(diào)諧范圍,KV必須較大。因此,對于要求低相位噪聲和寬調(diào)諧范圍的應(yīng)用,VCO制造商通常會設(shè)計低增益、輸入電壓范圍較大的振蕩器,以滿足這些相互矛盾的要求。

3 與高壓VCO接口

大多數(shù)商用PLL頻率合成器IC提供電荷泵輸出,其上限約為5.5 V;當(dāng)環(huán)路濾波器僅使用無源器件時,VCO要求較高的調(diào)諧電壓,該輸出不足以直接驅(qū)動VCO。為了達(dá)到較高的調(diào)諧電壓,必須利用運(yùn)算放大器電路實施有源環(huán)路濾波器拓?fù)浣Y(jié)構(gòu)。

實現(xiàn)這種結(jié)構(gòu)的最簡單方法是在無源環(huán)路濾波器之后添加一個增益級。雖然易于設(shè)計,但這種方法有幾個缺點(diǎn):反相運(yùn)算放大器配置具有低輸入阻抗,會使無源環(huán)路濾波器承受負(fù)載,從而改變環(huán)路動態(tài)特性;同相配置具有足夠高的輸入阻抗,不會使濾波器承受負(fù)載,但有源濾波器增益會放大運(yùn)算放大器的任何噪聲,從而無法受益于前置無源環(huán)路濾波器的濾波功能。

圖3顯示建議有源濾波器拓?fù)浣Y(jié)構(gòu)的兩個示例,其中前置濾波分別使用反相和同相增益。請注意,這些放大器電路是真時間積分器,可強(qiáng)迫PLL環(huán)路在輸入端保持零誤差。環(huán)路之外,所示拓?fù)浣Y(jié)構(gòu)可能會漂移至供電軌

a. 反相拓?fù)浣Y(jié)構(gòu)

b. 同相拓?fù)浣Y(jié)構(gòu)

圖3. 采用前置濾波的有源濾波器

反相拓?fù)浣Y(jié)構(gòu)的優(yōu)勢是可以將電荷泵輸出偏置在固定電壓,通常為電荷泵電壓的一半(VP/2),此時對雜散性能最有利。注意應(yīng)提供干凈的偏置電壓,最好是來源于ADP150等專用低噪聲線性穩(wěn)壓器,并在盡可能靠近運(yùn)算放大器輸入引腳處充分去耦。分壓器網(wǎng)絡(luò)所用的電阻值應(yīng)盡可能小,以便降低噪聲。使用反相拓?fù)浣Y(jié)構(gòu)時,必須確保PLL IC允許PFD極性反轉(zhuǎn);如有必要,應(yīng)抵消運(yùn)算放大器的反轉(zhuǎn),以正確的極性驅(qū)動VCO。ADF4xxx系列就具有這種特性。

同相環(huán)路濾波器配置不需要專用偏置,因此這種解決方案可能更緊湊。此時,電荷泵電壓不是偏置在固定電平,而是在其工作電壓范圍內(nèi)變化。4 選擇運(yùn)算放大器

運(yùn)算放大器的選擇對于最大限度地發(fā)揮有源濾波器的潛能至關(guān)重要。

濾波器輸出直接影響所產(chǎn)生的頻率和相位;因此,運(yùn)算放大器的噪聲電壓密度可以顯示有源濾波器將增加多少相位噪聲。放大器噪聲在PLL環(huán)路帶寬內(nèi)和帶外均會產(chǎn)生影響,在環(huán)路濾波器的轉(zhuǎn)折頻率處最為顯著,具有高噪聲電壓密度的放大器尤其突出。因此,放大器噪聲必須保持較低水平,才能完成放大器和高壓VCO的使命,提供較低的相位噪聲。

相對于PFD輸出電流,如果運(yùn)算放大器具有較為明顯的輸入偏置電流,則可能會導(dǎo)致PLL輸出頻譜上出現(xiàn)較大的雜散。為使VCO調(diào)諧電壓保持恒定且PLL保持鎖定,電荷泵必須補(bǔ)償每個PFD周期中運(yùn)算放大器輸入端所耗用的偏置電流。這就會在PFD頻率調(diào)制VTUNE電壓,并在載波周圍引起雜散,其偏移等于PFD頻率。

共模電壓范圍或輸入電壓范圍(IVR)是運(yùn)算放大器的另一個重要特性,但常被忽視,導(dǎo)致終端設(shè)計發(fā)生嚴(yán)重問題。IVR決定輸入引腳上最大/最小信號與正/負(fù)供電軌之間所需的間隙。

對于采用±15 V電源供電的早期運(yùn)算放大器,典型IVR為±12 V。后來加入了緩慢的橫向PNP輸入級,使得IVR可以包括負(fù)供電軌,從而提供單電源工作能力。雖然任何運(yùn)算放大器均能采用地和正電源供電,但必須注意輸入與供電軌的間距。

表1. 建議在PLL有源環(huán)路濾波器中使用的運(yùn)算放大器

運(yùn)算放大器的選擇取決于應(yīng)用。如果PFD雜散遠(yuǎn)離環(huán)路帶寬,則可以選用雙極性結(jié)型晶體管輸入(BJT)運(yùn)算放大器,如OP184或OP27等。環(huán)路濾波器將會很好地衰減BJT的高輸入偏置電流所引起的PFD雜散,而且PLL可以充分利用BJT運(yùn)算放大器的低噪聲電壓密度特性。

如果應(yīng)用要求較小的PFD與環(huán)路帶寬比,則應(yīng)折衷考慮噪聲與雜散水平;AD820和AD8661可能是較佳選擇。

值得注意的是,雖然有源濾波器往往會增加PLL的噪聲,但它能夠充當(dāng)緩沖器,在一些特定應(yīng)用中具有無源濾波器所不及的性能優(yōu)勢。例如,如果VCO調(diào)諧端口的泄漏電流較高,導(dǎo)致PFD雜散較高,則可以使用運(yùn)算放大器來降低雜散水平。運(yùn)算放大器的低阻抗輸出可輕松彌補(bǔ)調(diào)諧端口泄漏電流。

5 設(shè)計示例

為在1-GHz頻帶上工作,同時滿足相位噪聲要求,有必要使用高壓VCO和有源環(huán)路濾波器。相位噪聲和雜散特性以及單電源限制,將決定運(yùn)算放大器的選擇。為了達(dá)到雜散要求,運(yùn)算放大器必須具有低輸入偏置電流,而為了實現(xiàn)最佳相位噪聲性能,運(yùn)算放大器必須具有低電壓噪聲。選擇JFET輸入運(yùn)算放大器可以兼顧以上兩個要求,例如AD8661,其輸入偏置電流為0.3 pA,電壓噪聲為12 nV/√Hz。該器件還能處理單電源要求。選擇RFMDUMS-2000-A16 VCO來滿足倍頻程范圍要求。

開始設(shè)計時,最好利用支持有源濾波器拓?fù)浣Y(jié)構(gòu)的ADIsimPLLTM工具進(jìn)行仿真。圖3所示為兩種推薦的濾波器類型;ADIsimPLL還支持其它配置。

PLL選擇ADF4150,它具有整數(shù)和小數(shù)兩種工作模式,提供2/4/8/16/32幾種輸出分頻器選項,可覆蓋從2 GHz至31.25 MHz的連續(xù)頻率。ADF4150與圖2所示的ADF4350相似,但前者允許選擇外部VCO,適合需要滿足更嚴(yán)苛相位噪聲要求的應(yīng)用。在仿真過程中,PLL環(huán)路濾波器設(shè)置為20 kHz,以期減小運(yùn)算放大器的噪聲貢獻(xiàn),同時使PLL鎖定時間小于2 ms。

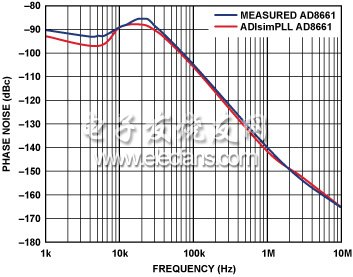

圖4所示為采用以下器件的仿真系統(tǒng)與測量系統(tǒng)噪聲(dBc)與頻率偏移關(guān)系曲線:ADF4150 PLL、UMS VCO和基于AD8661的濾波器。兩條曲線均顯示,由于有源環(huán)路濾波器增加的噪聲,約20 kHz時出現(xiàn)峰值噪聲–90 dBc,不過仍然實現(xiàn)了1 MHz偏移時–142 dBc/Hz的目標(biāo)。若要降低帶內(nèi)噪聲,可以使用OP184或OP27等噪聲更低的運(yùn)算放大器,但雜散會提高;或者將PLL環(huán)路帶寬降至20 kHz以下。

圖4. ADIsimPLL仿真性能與測量性能對比:AD8661用作PLL有源濾波器中的運(yùn)算放大器

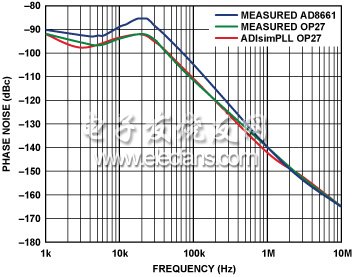

圖5顯示,使用OP27時性能約改善6 dB。這種情況下,因為環(huán)路帶寬相對較窄,所以雜散并未顯著增加。進(jìn)一步降低帶寬可以改善100 kHz以下偏移的相位噪聲,但PLL鎖定時間會延長。所有這些權(quán)衡考慮均可以在進(jìn)入實驗室設(shè)計之前,利用ADIsimPLL模擬進(jìn)行測試。

圖5. 有源環(huán)路濾波器中使用AD8661與使用OP27的PLL測量性能對比6 高壓PLL

以上討論都圍繞利用有源濾波器實現(xiàn)低壓PLL器件與高壓VCO接口而展開。不過,高壓PLL已經(jīng)出現(xiàn),因而使用有源濾波器的必要性大大降低。例如ADF4113HV PLL,它集成高壓電荷泵,歸一化相位本底噪聲為–212 dBc/Hz。

該高壓PLL系列產(chǎn)品將會不斷擴(kuò)充,不久將會出現(xiàn)最大電壓為30 V的器件,以及具有高壓電荷泵的小數(shù)N分頻PLL。有關(guān)產(chǎn)品更新和新產(chǎn)品信息,請訪問PLL網(wǎng)站。

7 集成VCO的寬帶寬PLL

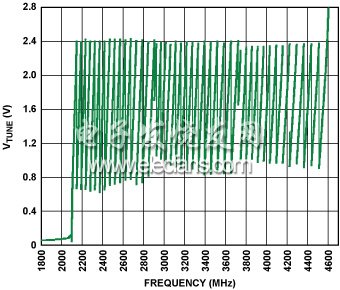

另外可以用完全集成的高性能PLL,例如圖2所示的ADF4350等,代替有源濾波器與高壓VCO組合。這種情況下,VCO集成在芯片內(nèi)。采用多頻段VCO方法可以避免上述權(quán)衡考慮寬調(diào)諧范圍與低相位噪聲的問題。ADF4350片內(nèi)集成三個獨(dú)立的VCO,每個VCO均有16個重疊子頻段,因而共有48個子頻段。

這真正體現(xiàn)出從分立式VCO設(shè)計轉(zhuǎn)向硅解決方案的優(yōu)勢:在極小的面積上實現(xiàn)非常高的集成度,從而使設(shè)計更加靈活。例如,ADF4350同時集成了可編程輸出分頻器級,可以覆蓋從137.5 MHz至4.4 GHz的頻率,這對于希望多種頻率和標(biāo)準(zhǔn)均采用同一設(shè)計的無線電設(shè)計師極具吸引力。

ADF4350采用5 mm2 LFCSP封裝,而標(biāo)準(zhǔn)VCO封裝為12.7 mm2。同時性能水平也接近分立設(shè)計;相位噪聲在100 kHz偏移時為–114 dBc/Hz,在1 MHz偏移時為–134 dBc/Hz。

圖6. ADF4350 VCO中48個不同頻段的電壓與頻率關(guān)系圖